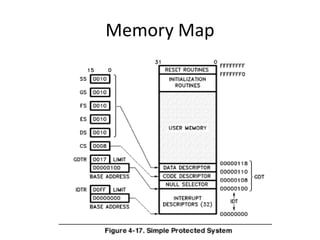

Memory map

- 1. Memory Map

- 2. Paging • In protected mode linear address space is mapped directly into a large physical memory • Or indirectly (using paging) into a smaller physical memory & disk storage. • This second method of mapping the linear address space is referred as virtual memory or demand paged virtual memory

- 3. Paging • Paging is another type of memory management useful for virtual memory multitasking operating systems • Freed space of an outgoing task always same as that needed for an incoming task

- 4. Paging • Linear address space is divided into fixed size pages • Pages can directly mapped into physical memory and/or disk storage • A page most likely corresponds to only a portion of a module or data structure

- 5. Paging • Page – – Fixed Size – May include Code/Data/Stack – Linear address is used to generate address of a page • A program on HDD is looked at as collection of same sized pages

- 6. Paging • Fixed size • Data structures and program modules can be partly in memory and partly in disk storage • Pages bear no direct relation to the logical structure of a program Segmentation • Size same as the code or data structures they hold • Data structures and program modules will have all its parts in memory • While segment selectors can be considered the logical ``name'' of a program module or data structure,

- 7. Advantages • A uniform size of 4KB for all of the elements simplifies memory allocation and reallocation schemes, since there is no problem with memory fragmentation.

- 9. Components of the paging mechanism • The page directory • The page tables • The page itself (page frame)

- 10. HDD P2.1 P1.0 P2.0 P3.0 P1.1 P1.2 P2.2 P2.3 FREE Page P1.0 P1.1 P1.2 P2.0 P2.1 P2.2 P2.3 P3.0 0 1 2 3 4 5 6 7 8 Page No. Base address 0 0 1 2 2 5 Page No. Base address 0 3 Page No. Base address 0 1 1 4 2 6 3 7 PMT : P3 process PMT : P1 process PMT : P2 process HDD

- 11. Page Map Table, Page Directory • Pages of a unique program are tabulated in a table – page Map table • Base addresses of All page tables are tabulated in a directory • Every application loaded has a unique page table

- 12. Page Directory • Tabulates information about all page tables in memory • Every record is called a Page Directory Entry (PDE) • Processor provides a special register viz CR3 to hold base address of this directory. • CR3 is known as Page Directory Base Register (PDBR)

- 14. Page Directory Entry Page Table Base Address OS Reserved (User) 0 0 D (U) A 0 0 U/S R/ W P 31 12 11 10 9 8 7 6 5 4 3 2 1 0 Pg Size – ‘0’ 4KB Whether a page table - A – Accessed P – Present Access Rights U/S – ‘0’ – table is assigned supervisor privilege level ‘1’ – table is assigned user level privilege level R/W - Read Write privileges for a group of pages i.e. table

- 15. PAGE TABLES • Each Page Table is 4K bytes and holds up to 1024 Page Table Entries. • Page Table Entries contain the starting address of the page frame and statistical information about the page • Page tables can be shared between tasks and swapped to disks.

- 16. Page Table Entry PAGE FRAME ADDRESS 31..12 OS Reserved (User) 0 0 D A 0 0 U/S R/ W P 31 12 11 10 9 8 7 6 5 4 3 2 1 0 Whether a page D - Dirty A – Accessed P – Present Access Rights U/S – ‘0’ – table is assigned supervisor privilege level ‘1’ – table is assigned user level privilege level R/W - Read Write privileges for a group of pages i.e. table

- 17. Non Present Page directory or Page Table entry 31 1 P Available to operating system for use 0

- 18. LINEAR ADDRESS TRANSLATION (4-KBYTE PAGES) To select the various table entries, the linear address is divided into three sections: • Page-directory entry—Bits 22 through 31 provide an offset to an entry in the page directory. The selected entry provides the physical base address of a page table. • Page-table entry—Bits 12 through 21 of the linear address provide an offset to an entry in the selected page table. This entry provides the physical base address of a page in physical memory. • Page offset—Bits 0 through 11 provides an offset to a physical address in the page.

- 19. Linear Address Translation - (4 KB Pages) Directory Entry Page Table Entry 4KB page PDBR Index to Directory Index to Table Offset in Page 31 22 21 12 11 0 Page Directory Page Table Page CR3

- 20. Virtual address 801C3400H Directory Entry 000E4000 Page Table Entry 00028000 PDBR Index to Directory Index to Table Offset in Page 1000000000 0111000011 010000000000 Page Directory Page Table CR3 200H 1C3H 400H + Physical address 00028400H