Flip flop& RAM ROM

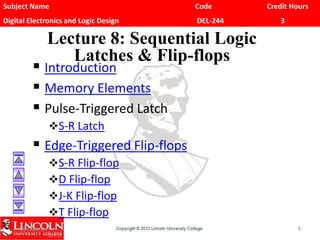

- 1. Subject Name Code Credit Hours Digital Electronics and Logic Design DEL-244 3 Lecture 8: Sequential Logic Latches & Flip-flops Introduction Memory Elements Pulse-Triggered Latch S-R Latch Edge-Triggered Flip-flops S-R Flip-flop D Flip-flop J-K Flip-flop T Flip-flop CS1104-11 1

- 2. Subject Name Code Credit Hours Digital Electronics and Logic Design DEL-244 3 Introduction A sequential circuit consists of a feedback path, and employs some memory elements. CS1104-11 Introduction 2 Combinational logic Memory elements Combinational outputs Memory outputs External inputs Sequential circuit = Combinational logic + Memory Elements

- 3. Subject Name Code Credit Hours Digital Electronics and Logic Design DEL-244 3 Introduction There are two types of sequential circuits: synchronous: outputs change only at specific time asynchronous: outputs change at any time Multivibrator: a class of sequential circuits. They can be: bistable (2 stable states) monostable or one-shot (1 stable state) astable (no stable state) Bistable logic devices: latches and flip-flops. Latches and flip-flops differ in the method used for changing their state. CS1104-11 Introduction 3

- 4. Subject Name Code Credit Hours Digital Electronics and Logic Design DEL-244 3 Memory Elements Memory element with clock. Flip-flops are memory elements that change state on clock signals. Clock is usually a square wave. CS1104-11 Memory Elements 4 command Memory element stored value Q clock Positive edges Negative edges Positive pulses

- 5. Subject Name Code Credit Hours Digital Electronics and Logic Design DEL-244 3 Memory Elements Two types of triggering/activation: pulse-triggered edge-triggered Pulse-triggered latches ON = 1, OFF = 0 Edge-triggered flip-flops positive edge-triggered (ON = from 0 to 1; OFF = other time) negative edge-triggered (ON = from 1 to 0; OFF = other time)CS1104-11 Memory Elements 5

- 6. Subject Name Code Credit Hours Digital Electronics and Logic Design DEL-244 3 S-R Latch Complementary outputs: Q and Q'. When Q is HIGH, the latch is in SET state. When Q is LOW, the latch is in RESET state. For active-HIGH input S-R latch (also known as NOR gate latch), R=HIGH (and S=LOW) a RESET state S=HIGH (and R=LOW) a SET state both inputs LOW a no change both inputs HIGH a Q and Q' both LOW (invalid)! CS1104-11 S-R Latch 6

- 7. Subject Name Code Credit Hours Digital Electronics and Logic Design DEL-244 3 S-R Latch For active-LOW input S'-R' latch (also known as NAND gate latch), R'=LOW (and S'=HIGH) a RESET state S'=LOW (and R'=HIGH) a SET state both inputs HIGH a no change both inputs LOW a Q and Q' both HIGH (invalid)! Drawback of S-R latch: invalid condition exists and must be avoided. CS1104-11 S-R Latch 7

- 8. Subject Name Code Credit Hours Digital Electronics and Logic Design DEL-244 3 S-R Latch Characteristics table for active-high input S-R latch: Characteristics table for active-low input S'- R' latch: CS1104-11 S-R Latch 8 S R Q Q' 0 0 NC NC No change. Latch remained in present state. 1 0 1 0 Latch SET. 0 1 0 1 Latch RESET. 1 1 0 0 Invalid condition. S' R' Q Q' 1 1 NC NC No change. Latch remained in present state. 0 1 1 0 Latch SET. 1 0 0 1 Latch RESET. 0 0 1 1 Invalid condition. S R Q Q' S R Q Q'

- 9. Subject Name Code Credit Hours Digital Electronics and Logic Design DEL-244 3 S-R Latch Active-HIGH input S-R latch Active-LOW input S’-R’ latch CS1104-11 S-R Latch 9 R S Q Q' S R Q Q' 1 0 1 0 initial 0 0 1 0 (afer S=1, R=0) 0 1 0 1 0 0 0 1 (after S=0, R=1) 1 1 0 0 invalid! S' R' Q Q' 1 0 0 1 initial 1 1 0 1 (afer S'=1, R'=0) 0 1 1 0 1 1 1 0 (after S'=0, R'=1) 0 0 1 1 invalid! S' R' Q Q' S' R' Q Q' 0 1 1 0 0 0 1 0 1 0 0 1 0 0 0 1 1 1 0 0

- 10. Subject Name Code Credit Hours Digital Electronics and Logic Design DEL-244 3 J-K Flip-flop J-K flip-flop: Q and Q' are fed back to the pulse-steering NAND gates. No invalid state. Include a toggle state. J=HIGH (and K=LOW) a SET state K=HIGH (and J=LOW) a RESET state both inputs LOW a no change both inputs HIGH a toggle CS1104-11 J-K Flip-Ffop 10

- 11. Subject Name Code Credit Hours Digital Electronics and Logic Design DEL-244 3 J-K Flip-flop J-K flip-flop. Characteristic table. CS1104-11 J-K Flip-flop 11 J Q Q' CLK Pulse transition detector K J K CLK Q(t+1) Comments 0 0 Q(t) No change 0 1 0 Reset 1 0 1 Set 1 1 Q(t)' Toggle Q J K Q(t+1) 0 0 0 0 0 0 1 0 0 1 0 1 0 1 1 1 1 0 0 1 1 0 1 0 1 1 0 1 1 1 1 0 Q(t+1) = J.Q' + K'.Q

- 12. Subject Name Code Credit Hours Digital Electronics and Logic Design DEL-244 3Memory Main memory consists of a number of storage locations, each of which is identified by a unique address The ability of the CPU to identify each location is known as its addressability Each location stores a word i.e. the number of bits that can be processed by the CPU in a single operation. Word length may be typically 16, 24, 32 or as many as 64 bits. A large word length improves system performance, though may be less efficient on occasions when the full word length is not used

- 13. Subject Name Code Credit Hours Digital Electronics and Logic Design DEL-244 3 Calculating the Maximum Capacity of Memory in a Computer • Max capacity = • number of address x capacity of each location Example What is the maximum amount of memory in a system which has a 16 bit data bus and a 24 bit address bus? Answer 224 x 2 16777216 x 2 33554432 bytes 32768 Kb 32Mb

- 14. Subject Name Code Credit Hours Digital Electronics and Logic Design DEL-244 3Types of main memory There are two types of main memory, Random Access Memory (RAM) and Read Only Memory (ROM) Random Access Memory (RAM) holds its data as long as the computer is switched on All data in RAM is lost when the computer is switched off Described as being volatile It is direct access as it can be both written to or read from in any order Its purpose is to temporarily hold programs and data for processing. In modern computers it also holds the operating system

- 15. Subject Name Code Credit Hours Digital Electronics and Logic Design DEL-244 3 Types of RAM 1. Dynamic Random Access Memory (DRAM) • Contents are constantly refreshed 1000 times per second • Access time 60 – 70 nanoseconds Note: a nanosecond is one billionth of a second! 2. Synchronous Dynamic Random Access Memory (SDRAM) • Quicker than DRAM • Access time less than 60 nanoseconds 3. Direct Rambus Dynamic Random Access Memory (DRDRAM) • New type of RAM architecture • Access time 20 times faster than DRAM • More expensive

- 16. Subject Name Code Credit Hours Digital Electronics and Logic Design DEL-244 3 4. Static Random Access Memory (SRAM) • Doesn’t need refreshing • Retains contents as long as power applied to the chip • Access time around 10 nanoseconds • Used for cache memory • Also for date and time settings as powered by small battery 5. Cache memory • Small amount of memory typically 256 or 512 kilobytes • Temporary store for often used instructions • Level 1 cache is built within the CPU (internal) • Level 2 cache may be on chip or nearby (external) • Faster for CPU to access than main memory Types of RAM

- 17. Subject Name Code Credit Hours Digital Electronics and Logic Design DEL-244 3 The operation of cache memory 1. Cache fetches data from next to current addresses in main memory 2. CPU checks to see whether the next instruction it requires is in cache 3. If it is, then the instruction is fetched from the cache – a very fast position 4. If not, the CPU has to fetch next instruction from main memory - a much slower process Main Memory (DRAM) CPU Cache Memory (SRAM) = Bus connections

- 18. Subject Name Code Credit Hours Digital Electronics and Logic Design DEL-244 3Types of RAM 6. Virtual memory • Uses backing storage e.g. hard disk as a temporary location for programs and data where insufficient RAM available • Swaps programs and data between the hard-disk and RAM as the CPU requires them for processing • A cheap method of running large or many programs on a computer system • Cost is speed: the CPU can access RAM in nanoseconds but hard-disk in milliseconds (Note: a millisecond is a thousandth of a second) • Virtual memory is much slower than RAM

- 19. Subject Name Code Credit Hours Digital Electronics and Logic Design DEL-244 3Read only memory (ROM) ROM holds programs and data permanently even when computer is switched off Data can be read by the CPU in any order so ROM is also direct access The contents of ROM are fixed at the time of manufacture Stores a program called the bootstrap loader that helps start up the computer Access time of between 10 and 50 nanoseconds

- 20. Subject Name Code Credit Hours Digital Electronics and Logic Design DEL-244 3 Types of ROM 1. Programmable Read Only Memory (PROM) • Empty of data when manufactured • May be permanently programmed by the user 2. Erasable Programmable Read Only Memory (EPROM) • Can be programmed, erased and reprogrammed • The EPROM chip has a small window on top allowing it to be erased by shining ultra-violet light on it • After reprogramming the window is covered to prevent new contents being erased • Access time is around 45 – 90 nanoseconds

- 21. Subject Name Code Credit Hours Digital Electronics and Logic Design DEL-244 3Types of ROM 3. Electrically Erasable Programmable Read Only Memory (EEPROM) • Reprogrammed electrically without using ultraviolet light • Must be removed from the computer and placed in a special machine to do this • Access times between 45 and 200 nanoseconds 4. Flash ROM • Similar to EEPROM • However, can be reprogrammed while still in the computer • Easier to upgrade programs stored in Flash ROM • Used to store programs in devices e.g. modems • Access time is around 45 – 90 nanoseconds 5. ROM cartridges • Commonly used in games machines • Prevents software from being easily copied

- 22. Subject Name Code Credit Hours Digital Electronics and Logic Design DEL-244 3 End of segment