Vhdlbputspdas

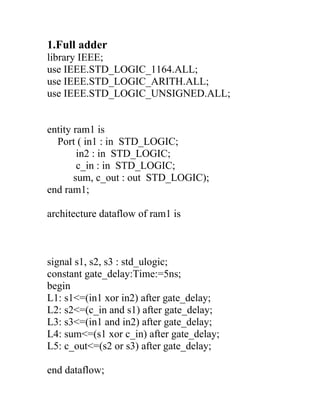

- 1. 1.Full adder library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; entity ram1 is Port ( in1 : in STD_LOGIC; in2 : in STD_LOGIC; c_in : in STD_LOGIC; sum, c_out : out STD_LOGIC); end ram1; architecture dataflow of ram1 is signal s1, s2, s3 : std_ulogic; constant gate_delay:Time:=5ns; begin L1: s1<=(in1 xor in2) after gate_delay; L2: s2<=(c_in and s1) after gate_delay; L3: s3<=(in1 and in2) after gate_delay; L4: sum<=(s1 xor c_in) after gate_delay; L5: c_out<=(s2 or s3) after gate_delay; end dataflow;

- 2. 2. 4:1 MUX (elsif) library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; entity mux1 is Port ( i : in STD_LOGIC_VECTOR (03 downto 0); s : in STD_LOGIC_VECTOR (01 downto 0); out1 : out STD_LOGIC); end mux1; architecture Behavioral of mux1 is begin process (s) begin if s="00" then out1<=i(0); elsif s="01" then out1<=i(1); elsif s="10" then out1<=i(2); elsif s="11" then out1<=i(3); end if; end process; end Behavioral;

- 3. 3. 4:1MUX using “when” library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; entity mux1 is Port ( i : in STD_LOGIC_VECTOR (03 downto 0); s : in STD_LOGIC_VECTOR (01 downto 0); out1 : out STD_LOGIC); end mux1; architecture Behavioral of mux1 is begin out1<= i(0) when (s=”00”) else out1<= i(1) when (s=”01”) else out1<= i(2) when (s=”10”) else out1<= i(3) when (s=”11”) ; end behavioral; 4. 1:4 DeMUX Entity demux_4 is Port (En: in std_logic;

- 4. Y0,Y1,Y2,Y3: out std_logic; i: in std_logic_vector (01 downto 00)); end demux_4; architecture of demux_4 is begin if i=”00” then Y0<=En; Y1<=’0’; Y2<=’0’; Y3<=’0’; elsif i=”01” then Y0<=’0’; Y1<=’En’; Y2<=’0’; Y3<=’0’; elsif i=”10” then Y0<=’0’; Y1<=’0’; Y2<=’En’; Y3<=’0’; elsif i=”11” then Y0<=’0’; Y1<=’0’; Y2<=’0’; Y3<=’En’; end behavioral;

- 5. 5. Full Adder (Behavioral) entity Add is port(a,b,ci:in std_logic; s,co: out std_logic); end add; architecture behavioral of Add is begin s<= ‘1’ when (a=’0’ and b=’1’ and ci=’0’) else ‘1’ when (a=’1’ and b=’0’ and ci=’0’) else ‘1’ when (a=’0’ and b=’0’ and ci=’1’) else ‘1’ when (a=’1’ and b=’1’ and ci=’1’) else ‘0’; c0<= ‘1’ when (a=’1’ and b=’1’ and ci=’0’) else ‘1’ when (a=’0’ and b=’1’ and ci=’1’) else ‘1’ when (a=’1’ and b=’0’ and ci=’1’) else ‘1’ when (a=’1’ and b=’1’ and ci=’1’) else ‘0’; end Add;

- 6. 6. D Latch entity D_latch is port (D: in std_logic; Q: out std_logic); end D_latch; architecture behavioral of D_latch is begin process(clk , D) begin if (clk=’1’) then Q<= D; end if; end process; end behavioral;

- 7. 7. D F/F (positive and negative edge trigger) entity DFF is port (D: in std_logic; Q: out std_logic); end DFF; architecture behavioral of DFF is begin process(clk , D) begin if (clk ‘event and clk=’1’) then Q<= D; end if; end process; end behavioral;