IEEE 2014 - 2015 VLSI PROJECT TITLES PART 2

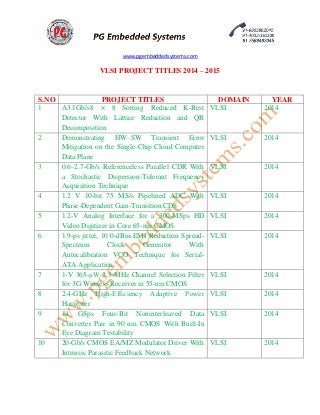

- 1. www.pgembeddedsystems.com VLSI PROJECT TITLES 2014 – 2015 S.NO PROJECT TITLES DOMAIN YEAR 1 A3.1Gb/s8 × 8 Sorting Reduced K-Best Detector With Lattice Reduction and QR Decomposition VLSI 2014 2 Demonstrating HW–SW Transient Error Mitigation on the Single-Chip Cloud Computer Data Plane VLSI 2014 3 0.6–2.7-Gb/s Referenceless Parallel CDR With a Stochastic Dispersion-Tolerant Frequency Acquisition Technique VLSI 2014 4 1.2 V 10-bit 75 MS/s Pipelined ADC With Phase-Dependent Gain-Transition CDS VLSI 2014 5 1.2-V Analog Interface for a 300-MSps HD Video Digitizer in Core 65-nm CMOS VLSI 2014 6 1.9-ps jitter, 10.0-dBm-EMI Reduction Spread- Spectrum Clock Generator With Autocalibration VCO Technique for Serial- ATA Application VLSI 2014 7 1-V 365-μW 2.5-MHz Channel Selection Filter for 3G Wireless Receiver in 55-nm CMOS VLSI 2014 8 2.4-GHz High-Efficiency Adaptive Power Harvester VLSI 2014 9 14 GSps Four-Bit Noninterleaved Data Converter Pair in 90 nm CMOS With Built-In Eye Diagram Testability VLSI 2014 10 20-Gb/s CMOS EA/MZ Modulator Driver With Intrinsic Parasitic Feedback Network VLSI 2014

- 2. www.pgembeddedsystems.com 11 28 nm 50% Power-Reducing Contacted Mask Read Only Memory Macro With 0.72-ns Read Access Time Using 2T Pair Bitcell and Dynamic Column Source Bias Control Technique VLSI 2014 12 32 Bit×32 Bit Multiprecision Razor-Based Dynamic Voltage Scaling Multiplier With Operands Scheduler VLSI 2014 13 320-Channel Active Probe for High-Resolution Neuromonitoring and Responsive Neurostimulation VLSI 2014 14 Nonvolatile CBRAM-Crossbar-Based 3-D- Integrated Hybrid Memory for Data Retention VLSI 2014 15 A 0.1–6.0-GHz Dual-Path SDR Transmitter Supporting Intraband Carrier Aggregation in 65- nm CMOS VLSI 2014 16 A 0.25-V 28-nW 58-dB Dynamic Range Asynchronous Delta Sigma Modulator in 130- nm Digital CMOS Process VLSI 2014 17 A 0.325 V, 600-kHz, 40-nm 72-kb 9T Subthreshold SRAM with Aligned Boosted Write Wordline and Negative Write Bitline Write-Assist VLSI 2014 18 A 2.5-Gb/s DLL-Based Burst-Mode Clock and Data Recovery Circuit With 4× Oversampling VLSI 2014 19 A 2-D Interpolation-Based QRD Processor With Partial Layer Mapping for MIMO-OFDM Systems VLSI 2014 20 A 3.6-mW 50-MHz PN Code Acquisition Filter via Statistical Error Compensation in 180-nm CMOS VLSI 2014

- 3. www.pgembeddedsystems.com 21 A 5.8-GHz Wideband TSPC Divide-by-16/17 Dual Modulus Prescaler VLSI 2014 22 A 12.5-Gb/s On-Chip Oscilloscope to Measure Eye Diagrams and Jitter Histograms of High- Speed Signals VLSI 2014 23 A 16-mW 8-Bit 1-GS/s Digital-Subranging ADC in 55-nm CMOS VLSI 2014 24 A 28-nm CMOS 1 V 3.5 GS/s 6-bit DAC With Signal-Independent Delta-I Noise DfT Scheme VLSI 2014 25 A 65 nm Cryptographic Processor for High Speed Pairing Computation VLSI 2014 26 A Boosting Pass Gate With Improved Switching Characteristics and No Overdriving for Programmable Routing Switch Based on Crystalline In-Ga-Zn-O Technology VLSI 2014 27 A Class of SEC-DED-DAEC Codes Derived From Orthogonal Latin Square Codes VLSI 2014 28 A CMOS PWM Transceiver Using Self- Referenced Edge Detection VLSI 2014 29 A Combined SDC-SDF Architecture for Normal I/O Pipelined Radix-2 FFT VLSI 2014 30 A Complete Resistive-Open Defect Analysis for Thermally Assisted Switching MRAMs VLSI 2014 31 A Digital Frequency Multiplication Technique for Energy Efficient Transmitters VLSI 2014 32 A Fast Application-Based Supply Voltage Optimization Method for Dual Voltage FPGA VLSI 2014 33 A Fast Transient Response Flying-Capacitor Buck–Boost Converter Utilizing Pseudocurrent Dynamic Acceleration Techniques VLSI 2014

- 4. www.pgembeddedsystems.com 34 A Fine-Grain Dynamically Reconfigurable Architecture Aimed at Reducing the FPGA- ASIC Gaps VLSI 2014 35 A Forwarded Clock Receiver Based on Injection-Locked Oscillator With AC-Coupled Clock Multiplication Unit in 0.13 µmCMOS VLSI 2014 36 A Generic and Scalable Architecture for a Large Acoustic Model and Large Vocabulary Speech Recognition Accelerator Using Logic on Memory VLSI 2014 37 A GPU-Accelerated Parallel Shooting Algorithm for Analysis of Radio Frequency and Microwave Integrated Circuits VLSI 2014 38 A Highly-Scalable Analog Equalizer Using a Tunable and Current-Reusable Active Inductor for 10-Gb/s I/O Links VLSI 2014 39 A Low-Cost Low-Power All-Digital Spread- Spectrum Clock Generator VLSI 2014 40 A Low-Jitter Cell-Based Digitally Controlled Oscillator With Differential Multiphase Outputs VLSI 2014 41 A Low-Latency and Low-Power Hybrid Scheme for On-Chip Networks VLSI 2014 42 A Method for Improving Power Grid Resilience to Electromigration-Caused via Failures VLSI 2014 43 A Method to Extend Orthogonal Latin Square Codes VLSI 2014

- 5. www.pgembeddedsystems.com 44 A Neuromorphic Approach to Path Planning Using a Reconfigurable Neuron Array IC VLSI 2014 45 A New Efficiency-Improvement Low-Ripple Charge-Pump Boost Converter Using Adaptive Slope Generator With Hysteresis Voltage Comparison Techniques VLSI 2014 46 A Process-Variation Resilient Current Mode Logic With Simultaneous Regulations for Time Constant, Voltage Swing, Level Shifting, and DC Gain Using Time-Reference-Based Adaptive Biasing Chain VLSI 2014 47 A Reconfigurable 2×/2.5×/3×/4× SC DC–DC Regulator With Fixed On-Time Control for Transcutaneous Power Transmission VLSI 2014 48 A Ripple Control Dual-Mode Single-Inductor Dual-Output Buck Converter With Fast Transient Response VLSI 2014 49 A Self-Powered High-Efficiency Rectifier With Automatic Resetting of Transducer Capacitance in Piezoelectric Energy Harvesting Systems VLSI 2014 50 A Sub-1 V Transient-Enhanced Output- Capacitorless LDO Regulator With Push–Pull Composite Power Transistor VLSI 2014 51 A Supply Voltage and Temperature Variation- Tolerant Relaxation Oscillator for Biomedical Systems Based on Dynamic Threshold and Switched Resistors VLSI 2014 52 A Synergetic Use of Bloom Filters for Error Detection and Correction VLSI 2014 53 A Systematic Design Methodology for Low- Power NoCs VLSI 2014

- 6. www.pgembeddedsystems.com 54 A Unified Write Buffer Cache Management Scheme for Flash Memory VLSI 2014 55 A Voltage Monitoring IC With HV Multiplexer and HV Transceiver for Battery Management Systems VLSI 2014 56 A Voltage-Based Leakage Current Calculation Scheme and its Application to Nanoscale MOSFET and FinFET Standard-Cell Designs VLSI 2014 57 A Wide-Range Multiport LC-Ladder Oscillator and Its Applications to a 1.2–10.1 GHz PLL VLSI 2014 58 Accelerating Scalar Conversion for Koblitz Curve Cryptoprocessors on Hardware Platforms VLSI 2014 59 Accurate and Efficient On-Chip Spectral Analysis for Built-In Testing and Calibration Approaches VLSI 2014 60 Achieving High-Performance On-Chip Networks With Shared-Buffer Routers VLSI 2014 61 Actively Alleviate Power Gating-Induced Power/Ground Noise Using Parasitic Capacitance of On-Chip Memories in MPSoC VLSI 2014 62 Adaptive Floating-Gate Circuit Enabled Large-Scale FPAA VLSI 2014 63 ADC-Based Backplane Receiver Design-Space Exploration VLSI 2014 64 Addressing Partitioning Issues in Parallel Circuit Simulation VLSI 2014 65 Aging-Aware Reliable Multiplier Design With Adaptive Hold Logic VLSI 2014 66 Algorithm and Architecture for a Low-Power Content-Addressable Memory Based on Sparse Clustered Networks VLSI 2014 67 All Digital Energy Sensing for Minimum Energy Tracking VLSI 2014

- 7. www.pgembeddedsystems.com 68 An 8 bit 0.3–0.8 V 0.2–40 MS/s 2-bit/Step SAR ADC With Successively Activated Threshold Configuring Comparators in 40 nm CMOS VLSI 2014 69 An 11.5 Gb/s 1/4th Baud-Rate CTLE and Two- Tap DFE With Boosted High Frequency Gain in 110-nm CMOS VLSI 2014 70 An Accuracy-Adjustment Fixed-Width Booth Multiplier Based on Multilevel Conditional Probability VLSI 2014 71 An Analog VLSI Implementation of the Inner Hair Cell and Auditory Nerve Using a Dual AGC Model VLSI 2014 72 An Efficient VLSI Architecture of a Reconfigurable Pulse-Shaping FIR Interpolation Filter for Multistandard DUC VLSI 2014 73 An Event-Based Neural Network Architecture With An Inter/Intra-Chip Optical Network for Manycore Processorsan Asynchronous Programmable Synaptic Memory VLSI 2014 74 An Inter/Intra-Chip Optical Network for Manycore Processors VLSI 2014 75 An I/O Efficient Model Checking Algorithm for Large-Scale Systems VLSI 2014 76 An Offset-Canceling Triple-Stage Sensing Circuit for Deep Submicrometer STT-RAM VLSI 2014 77 An Ultralow Power Multirate FSK Demodulator With Digital-Assisted Calibrated Delay-Line Based Phase Shifter for High-Speed Biomedical Zero-IF Receivers VLSI 2014 78 Analysis and Design of a Low-Voltage Low- Power Double-Tail Comparator VLSI 2014 79 Application Mapping Onto Mesh-Based Network-on-Chip Using Discrete Particle Swarm Optimization VLSI 2014

- 8. www.pgembeddedsystems.com 80 Application-Guided Power Gating Reducing Register File Static Power VLSI 2014 81 Application-Independent Testing of 3-D Field Programmable Gate Array Interconnect Faults VLSI 2014 82 Architecture-Aware Analytical Yield Model for Read Access in Static Random Access Memory VLSI 2014 83 Area-Delay Efficient Binary Adders in QCA VLSI 2014 84 Area-Delay-Power Efficient Fixed-Point LMS Adaptive Filter With Low Adaptation-Delay VLSI 2014 85 Area-Efficient Asynchronous Multilevel Single- Track Pipeline Template VLSI 2014 86 Arithmetic-Based Binary-to-RNS Converter Modulo {2n ± k} for jn-Bit Dynamic Range VLSI 2014 87 ASIC and FPGA Implementation of the Gaussian Mixture Model Algorithm for Real- Time Segmentation of High Definition video VLSI 2014 88 Asymmetric Aging: Introduction and Solution for Power-Managed Mixed-Signal SoCs VLSI 2014 89 Asynchronous Domino Logic Pipeline Design Based on Constructed Critical Data Path VLSI 2014 90 Aurora: A Cross-Layer Solution for Thermally Resilient Photonic Network-on-Chip VLSI 2014 91 Average-8T Differential-Sensing Subthreshold SRAM With Bit Interleaving and 1k Bits Per Bitline VLSI 2014 92 AWARE (Asymmetric Write Architecture with REdundant blocks): A High Write Speed STT-MRAM Cache Architecture VLSI 2014 93 Beware the Dynamic C-Element VLSI 2014 94 Built-In Binary Code Inversion Technique for On-Chip Flash Memory Sense Amplifier With Reduced Read Current Consumption VLSI 2014

- 9. www.pgembeddedsystems.com 95 Built-in Self-Calibration and Digital-Trim Technique for 14-Bit SAR ADCs Achieving ±1LSBINL VLSI 2014 96 Built-In Self-Test of Transmitter I/Q Mismatch and Nonlinearity Using Self-Mixing Envelope Detector VLSI 2014 97 CMOS Charge Pump With No Reversion Loss and Enhanced Drivability VLSI 2014 98 Comparative Study of Various Latch-Type Sense Amplifiers VLSI 2014 99 Compiler-Assisted Leakage- and Temperature- Aware Instruction-Level VLIW Scheduling VLSI 2014 100 Compiler-Assisted Leakage- and Temperature- Aware Instruction-Level VLIW Scheduling VLSI 2014 101 Computation on Stochastic Bit Streams Digital Image Processing Case Studies VLSI 2014 102 Configuration Mapping Algorithms to Reduce Energy and Time Reconfiguration Overheads in Reconfigurable Systems VLSI 2014 103 Constructing Sub-Arrays with Short Interconnects from Degradable VLSI Arrays VLSI 2014 104 Dark Silicon AwareMulticore Systems: Employing Design AutomationWith Architectural Insight VLSI 2014 105 Data Encoding Techniques for Reducing Energy Consumption in Network-on-Chip VLSI 2014 106 Data Remapping for Static NUCA in Degradable Chip Multiprocessors VLSI 2014 107 Data-Dependent Operation Speed-Up Through Automatically Inserted Signal Transition Detectors for Ultralow Voltage Logic Circuits VLSI 2014 108 Debugging RTL Using Structural Dominance VLSI 2014 109 Delay Test for Diagnosis of Power Switches VLSI 2014

- 10. www.pgembeddedsystems.com 110 Demystifying Iddq Data With Process Variation for Automatic Chip Classification VLSI 2014 111 Design Flow for Flip-Flop Grouping in Data- Driven Clock Gating VLSI 2014 112 Design for Testability Support for Launch and Capture Power Reduction in Launch-Off-Shift and Launch-Off-Capture Testing VLSI 2014 113 Design of a Low-Voltage Low-Dropout Regulator VLSI 2014 114 Design of On-Chip Lightweight Sensors for Effective Detection of Recycled ICs VLSI 2014 115 Design of Self-Timed Reconfigurable Controllers for Parallel Synchronization via Wagging VLSI 2014 116 Design Techniques to Improve Blocker Tolerance of Continuous-Time ADCs VLSI 2014 117 Designing a SAR-Based All-Digital Delay- LockedLoop With Constant Acquisition Cycles Using a Resettable Delay Line VLSI 2014 118 Diagnose Failures Caused by Multiple Locations at a Time VLSI 2014 119 Diagnosis and Layout Aware (DLA) Scan Chain Stitching VLSI 2014 120 Digitally Controlled Pulse Width Modulator for On-Chip Power Management VLSI 2014 121 Economizing TSV Resources in 3-D Network-on-Chip Design VLSI 2014 122 Efficient Hardware Architecture of ηT Pairing Accelerator Over Characteristic Three VLSI 2014 123 Efficient Parallel Turbo-Decoding for High- Throughput Wireless Systems VLSI 2014

- 11. www.pgembeddedsystems.com 124 Efficient Power-Analysis-Resistant Dual-Field Elliptic Curve Cryptographic Processor Using Heterogeneous Dual-Processing-Element Architecture VLSI 2014 125 Efficient Register Renaming and Recovery for High-Performance Processors VLSI 2014 126 Efficient VLSI Implementation of Neural Networks With Hyperbolic Tangent Activation Function VLSI 2014 127 Eleven Ways to Boost Your Synchronizer VLSI 2014 128 Eliminating Synchronization Latency Using Sequenced Latching VLSI 2014 129 Energy Aware Mapping for Reconfigurable Wireless MPSoCs VLSI 2014 130 Energy Efficiency Optimization Through Codesign of the Transmitter and Receiver in High-Speed On-Chip Interconnects VLSI 2014 131 Energy Efficient Programmable MIMO Decoder Accelerator Chip in 65-nm CMOS VLSI 2014 132 Energy-Efficient Soft-Input Soft-Output Signal Detector for Iterative MIMO Receivers VLSI 2014 133 Enhanced Memory Reliability Against Multiple Cell Upsets Using Decimal Matrix Code VLSI 2014 134 Equalization-Based Digital Background Calibration Technique for Pipelined ADCs VLSI 2014 135 Error Correction Encoding for Tightly Coupled On-Chip Buses VLSI 2014 136 Evaluation of Leakage Reduction Alternatives for Deep Submicron Dynamic Nonuniform Cache Architecture Caches VLSI 2014 137 Examining Timing Path Robustness Under Wide-Bandwidth Power Supply Noise Through Multi-Functional-Cycle Delay Test VLSI 2014

- 12. www.pgembeddedsystems.com 138 Experimental Validation of a Two-Phase Clock Scheme for Fine-Grained Pipelined Circuits Based on Monostable to Bistable Logic Elements VLSI 2014 139 Exploiting Early Tag Access for Reducing L1 Data Cache Energy in Embedded Processors VLSI 2014 140 Exploiting Same Tag Bits to Improve the Reliability of the Cache Memories VLSI 2014 141 Exploring High-Throughput Computing Paradigm for Global Routing VLSI 2014 142 Extraction of VLSI Multiconductor Transmission Line Parameters by Complementarity VLSI 2014 143 Failure Mitigation Techniques for 1T-1MTJ Spin-Transfer Torque MRAM Bit-cells VLSI 2014 144 Fast and Flexible Hardware Support for ECC Over Multiple Standard Prime Fields VLSI 2014 145 Fast and Wide Range Voltage Conversion in Multisupply Voltage Designs VLSI 2014 146 Fast Design Optimization Through Simple Kriging Metamodeling: A Sense Amplifier Case Study VLSI 2014 147 Fast RC Reduction of Flip-Chip Power Grids Using Geometric Templates VLSI 2014 148 Fast Sign Detection Algorithm for the RNS Moduli Set {2n+1 − 1, 2n − 1, 2n} VLSI 2014 149 Fast Thermal Aware Placement With Accurate Thermal Analysis Based on Green Function VLSI 2014 150 Fast Transistor Threshold Voltage Measurement Method for High-Speed, High-Accuracy Advanced Process Characterization VLSI 2014 151 Fat-Tree-Based Optical Interconnection Networks Under Crosstalk Noise Constraint VLSI 2014 152 Fault Tolerant Parallel Filters Based on Error Correction Codes VLSI 2014

- 13. www.pgembeddedsystems.com 153 Fault-Duration and-Location Aware CED Technique With Runtime Adaptability VLSI 2014 154 Fin CANON: A PVT-Aware Integrated Delay and Power Modeling Framework for FinFET- Based Caches and On-Chip Networks VLSI 2014 155 Fine-Grained Fast Field-Programmable Gate Array Scrubbing VLSI 2014 156 Flexible Low Complexity Uniform and Nonuniform Digital Filter Banks With High Frequency Resolution for Multistandard Radios VLSI 2014 157 FPGA-Based Bit Error Rate Performance Measurement of Wireless Systems VLSI 2014 158 FPGA-RPI: A Novel FPGA Architecture With RRAM-Based Programmable Interconnects VLSI 2014 159 Framework for Multiple-Fault Diagnosis Based on Multiple Fault Simulation Using Particle Swarm Optimization VLSI 2014 160 Framework for Multiple-Fault Diagnosis Based on Multiple Fault Simulation Using Particle Swarm Optimization VLSI 2014 161 Frequency-Independent Warning Detection Sequential for Dynamic Voltage and Frequency Scaling in ASICs VLSI 2014 162 Friendly Fast Poisson Solver Preconditioning Technique for Power Grid Analysis VLSI 2014 163 FTQLS: Fault-Tolerant Quantum Logic Synthesis VLSI 2014 164 Fully Reused VLSI Architecture of FM0/Manchester Encoding Using SOLS Technique for DSRC Applications VLSI 2014 165 Functional Constraint Extraction From Register Transfer Level for ATPG VLSI 2014 166 Gate Mapping Automation for Asynchronous NULL Convention Logic Circuits VLSI 2014

- 14. www.pgembeddedsystems.com 167 Hardware Efficient Mixed Radix-25/16/9 FFT for LTE Systems VLSI 2014 168 High Fill Factor Low-Voltage CMOS Image Sensor Based on Time-to-Threshold PWM VLSI Architecture VLSI 2014 169 High-Frequency CMOS Active Inductor: Design Methodology and Noise Analysis VLSI 2014 170 High-Performance H.264/AVC Intra-Prediction Architecture for Ultra High Definition Video Applications VLSI 2014 171 High-Resolution All-Digital Duty-Cycle Corrector in 65-nm CMOS Technology VLSI 2014 172 High-Throughput and Low-Complexity BCH Decoding Architecture for Solid-State Drives VLSI 2014 173 High-Throughput Multistandard Transform Core Supporting MPEG/H.264/VC-1 Using Common Sharing Distributed Arithmetic VLSI 2014 174 Impact of Bias Temperature Instability on Soft Error Susceptibility VLSI 2014 175 Improved Accuracy Current-ModeMultiplier Circuits With Applications in Analog Signal Processing VLSI 2014 176 Improved Analytical Delay Models for RC- Coupled Interconnects VLSI 2014 177 Improved Matching-Pursuit Implementation for LTE Channel Estimation VLSI 2014 178 Improving Energy Efficiency in FPGA Through Judicious Mapping of Computation to Embedded Memory Blocks VLSI 2014 179 Incorporating Hot-Carrier Injection Effects Into Timing Analysis for Large Circuits VLSI 2014 180 Increase in Read Noise Margin of Single-Bit- Line SRAM Using Adiabatic Change of Word Line Voltage VLSI 2014

- 15. www.pgembeddedsystems.com 181 Incremental Trace-Buffer Insertion for FPGA Debug VLSI 2014 182 Input VectorMonitoring Concurrent BIST Architecture Using SRAM Cells VLSI 2014 183 Integrated Algorithm for 3-D IC Through- Silicon Via Assignment VLSI 2014 184 Interleaving Test Algorithm for Subthreshold Leakage-Current Defects in DRAM Considering the Equal Bit Line Stress VLSI 2014 185 Iterative Linear Interpolation Based on Fuzzy Gradient Model for Low-Cost VLSI Implementation VLSI 2014 186 Large-Scale Memristive Associative Memories VLSI 2014 187 LASIC: Loop-Aware Sleepy Instruction Caches Based on STT-RAM Technology VLSI 2014 188 Layout-Based Refined NPSF Model for DRAM Characterization and Testing VLSI 2014 189 Level-Converting Retention Flip-Flop for Reducing Standby Power in ZigBee SoCs VLSI 2014 190 Leveraging Hotspots and Improving Chip Reliability via Carbon Nanotube Grid Thermal Structure VLSI 2014 191 Lifetime Enhancement Techniques for PCM- Based Image Buffer in Multimedia Applications VLSI 2014 192 Light-Weight On-Chip Structure for Measuring Timing Uncertainty Induced by Noise in Integrated Circuits VLSI 2014 193 Linearization Technique for Binary Phase Detectors in a Collaborative Timing Recovery Circuit VLSI 2014 194 Litho-Friendly DecompositionMethod for Self- AlignedTriple Patterning VLSI 2014

- 16. www.pgembeddedsystems.com 195 Logic Drivers: A Propagation Delay Modeling Paradigm for Statistical Simulation of Standard Cell Designs VLSI 2014 196 Logical Effort for CMOS-Based Dual Mode Logic Gates VLSI 2014 197 Low Overhead Software Wear Leveling for Hybrid PCM + DRAM Main Memory on Embedded Systems VLSI 2014 198 Low-Complexity Hardware Design for Fast Solving LSPs With Coordinated Polynomial Solution VLSI 2014 199 Low-Complexity Low-Latency Architecture for Matching of Data EncodedWith Hard Systematic Error-Correcting Codes VLSI 2014 200 Low-Complexity Reconfigurable Fast Filter Bank for Multi-StandardWireless Receivers VLSI 2014 201 Low-Cost Control Flow Protection via Available Redundancies in the Microprocessor Pipeline VLSI 2014 202 Low-Cost Low-Power ASIC Solution for Both DAB+ and DAB Audio Decoding VLSI 2014 203 Low-Cost On-Chip Clock Jitter Measurement Scheme VLSI 2014 204 Low-Cost Per-Core Voltage Domain Support for Power-Constrained High-Performance Processors VLSI 2014 205 Low-Energy Two-Stage Algorithm for High Efficacy Epileptic Seizure Detection VLSI 2014 206 Low-Latency Maximal-Throughput Communication Interfaces for Rationally Related Clock Domains VLSI 2014 207 Low-Power Digital Signal Processor Architecture for Wireless Sensor Nodes VLSI 2014

- 17. www.pgembeddedsystems.com 208 Low-Power Programmable PRPG With Test Compression Capabilities VLSI 2014 209 Low-Power Pulse-Triggered Flip-Flop Design Based on a Signal Feed-Through Scheme VLSI 2014 210 Low-Power Test Generation by Merging of Functional Broadside Test Cubes VLSI 2014 211 Low-Power, Minimally Invasive Process Compensation Technique for Sub-Micron CMOS Amplifiers VLSI 2014 212 Configuration Mapping Algorithms to Reduce Energy and Time Reconfiguration Overheads in Reconfigurable Systems VLSI 2014 213 Mapping Loop Structures onto Parametrized Hardware Pipelines VLSI 2014 214 Memory-Hierarchical and Mode-Adaptive HEVC Intra Prediction Architecture for Quad Full HD Video Decoding VLSI 2014 215 Minitaur, an Event-Driven FPGA-Based Spiking Network Accelerator VLSI 2014 216 Monolithic Low-EMI CMOS DC–DC Boost Converter for Portable Applications VLSI 2014 217 Multiple-Vote Symbol-Flipping Decoder for Nonbinary LDPC Codes VLSI 2014 218 Multivoltage Aware Resistive Open Fault Model VLSI 2014 219 Nano Magnetic STT-Logic Partitioning for Optimum Performance VLSI 2014 220 New 2-D Eye-Opening Monitor for Gb/s Serial Links VLSI 2014 221 Nonbinary LDPC Decoder Based on Simplified Enhanced Generalized Bit-Flipping Algorithm VLSI 2014

- 18. www.pgembeddedsystems.com 222 Nonvolatile CBRAM-Crossbar-Based 3-D- Integrated Hybrid Memory for Data Retention VLSI 2014 223 Novel Circuit-Level Model for Gate Oxide Short and its Testing Method in SRAMs VLSI 2014 224 Novel Class of Energy-Efficient Very High- Speed Conditional Push–Pull Pulsed Latches VLSI 2014 225 Novel Field-Programmable Gate Array Architecture for Computing the Eigenvalue Decomposition of Para-Hermitian Polynomial Matrices VLSI 2014 226 Novel Reconfigurable Hardware Architecture for Polynomial Matrix Multiplications VLSI 2014 227 Novel Structures for Cyclic Convolution Using Improved First-Order Moment Algorithm VLSI 2014 228 Obfuscating DSP Circuits via High-Level Transformations VLSI 2014 229 Obstacle-Avoiding and Slew-Constrained Clock Tree Synthesis With Efficient Buffer Insertion VLSI 2014 230 On Deadlock Problem of On-Chip Buses Supporting Out-of-Order Transactions VLSI 2014 231 On System-on-Chip Testing Using Hybrid Test Vector Compression VLSI 2014 232 On the Automatic Generation of Optimized Software-Based Self-Test Programs for VLIW Processors VLSI 2014 233 On the Nonvolatile Performance of Flip- Flop/SRAM Cells With a Single MTJ VLSI 2014 234 On-Chip Memory Hierarchy in One Coarse-Grained Reconfigurable Architecture to Compress Memory Space and to Reduce Reconfiguration Time and Data-Reference Time VLSI 2014

- 19. www.pgembeddedsystems.com 235 One-Sided Static Noise Margin and Gaussian-Tail-Fitting Method for SRAM VLSI 2014 236 On-the-Field Test and Configuration Infrastructure for 2-D-Mesh NoCs in Shared- Memory Many-Core Architectures VLSI 2014 237 Optimization Scheme to Minimize Reference Resistance Distribution of Spin-Transfer-Torque MRAM VLSI 2014 238 Orchestrator: Guarding Against Voltage Emergencies in Multithreaded Applications VLSI 2014 239 PaCC: A Parallel Compare and Compress Codec for Area Reduction in Nonvolatile Processors VLSI 2014 240 Parallel Thermal Analysis of 3-D Integrated Circuits With Liquid Cooling on CPU-GPU Platforms VLSI 2014 241 Efficient Parallel Turbo-Decoding for High-Throughput Wireless Systems VLSI 2014 242 Parameterized All-Digital PLL Architecture and its Compiler to Support Easy Process Migration VLSI 2014 243 Parasitics-Aware Design of Symmetric and Asymmetric Gate-Workfunction FinFET SRAMs VLSI 2014 244 Partial Access Mode: New Method for Reducing Power Consumption of Dynamic Random Access Memory VLSI 2014 245 Partial Parity Cache and Data Cache Management Method to Improve the Performance of an SSD-Based RAID VLSI 2014 246 Per-Core DVFS With Switched-Capacitor Converters for Energy Efficiency in Manycore Processors VLSI 2014

- 20. www.pgembeddedsystems.com 247 Power and Bandwidth Scalable 10-b 30-MS/s SAR ADC VLSI 2014 248 Power Blurring: Fast Static and Transient Thermal Analysis Method for Packaged Integrated Circuits and Power Devices VLSI 2014 249 Power Efficient Class AB Op-AmpsWith High and Symmetrical Slew Rate VLSI 2014 250 Efficient Power-Analysis-Resistant Dual-Field Elliptic Curve Cryptographic Processor Using Heterogeneous Dual-Processing-Element Architecture VLSI 2014 251 Power-Planning-Aware Soft Error Hardening via Selective Voltage Assignment VLSI 2014 252 Practical Routability-Driven Design Flow for Multilayer Power Networks Using Aluminum-Pad Layer VLSI 2014 253 Predictive Application of PIDF and PPC for Interconnects’ Crosstalk, TSV, and LER Issues in UDSM ICs and Nano-Systems VLSI 2014 254 Processor Tile Shapes and Interconnect Topologies for Dense On-Chip Networks VLSI 2014 255 Protein Alignment Systolic Array Throughput Optimization VLSI 2014 256 Pulsed-Latch Utilization for Clock-Tree Power Optimization VLSI 2014 257 Quaternary Logic Lookup Table in Standard CMOS VLSI 2014 258 Radiation-Hard Field-Programmable Gate Arrays Configuration Technique Using Silicon on Sapphire VLSI 2014 259 Randomized Multitopology Logic Against Differential Power Analysis VLSI 2014

- 21. www.pgembeddedsystems.com 260 Range Unlimited Delay-Interleaving and – Recycling Clock Skew Compensation and Duty- Cycle Correction Circuit VLSI 2014 261 Rate-0.96 LDPC Decoding VLSI for Soft- Decision Error Correction of NAND Flash Memory VLSI 2014 262 Razor Based Programmable Truncated Multiply and Accumulate, Energy-Reduction for Efficient Digital Signal Processing VLSI 2014 263 Read Performance: The Newest Barrier in Scaled STT-RAM VLSI 2014 264 Reconfigurable CORDIC-Based Low-Power DCT Architecture Based on Data Priority VLSI 2014 265 Recursive Approach to the Design of a Parallel Self-Timed Adder VLSI 2014 266 Reducing Energy at the Minimum Energy Operating Point Via Statistical Error Compensation VLSI 2014 267 Reliability-Oriented Placement and Routing Algorithm for SRAM-Based FPGAs VLSI 2014 268 Reliable Concurrent Error Detection Architectures for Extended Euclidean-Based Division Over GF(2m) VLSI 2014 269 Reliable Low-Power Multiplier Design Using Fixed-Width Replica Redundancy Block VLSI 2014 270 Resistive Open Faults Detectability Analysis and Implications for Testing Low Power Nanometric ICs VLSI 2014 271 Resistive Threshold Logic VLSI 2014 272 Restoration-Based Procedures With Set Covering Heuristics for Static Test Compaction of Functional Test Sequences VLSI 2014

- 22. www.pgembeddedsystems.com 273 Reverse Converter Design via Parallel-Prefix Adders Novel Components, Methodology, and Implementations VLSI 2014 274 Revisiting Central Limit Theorem: Accurate Gaussian Random Number Generation in VLSI VLSI 2014 275 Runtime Adaptive Circuit Switching and Flow Priority in NoC-Based MPSoCs VLSI 2014 276 Runtime Thermal Management for 3-D Chip- Multiprocessors With Hybrid SRAM/MRAM L2 Cache VLSI 2014 277 SACCI: Scan-Based Characterization Through Clock Phase Sweep for Counterfeit Chip Detection VLSI 2014 278 Scalable Effort Hardware Design VLSI 2014 279 Scan Test of Die Logic in 3-D ICs Using TSV Probing VLSI 2014 280 Segmented Architecture for Successive Approximation Analog-to-Digital Converters VLSI 2014 281 Sensitization Input Vector Impact on Propagation Delay for Nanometer CMOS ICs: Analysis and Solutions VLSI 2014 282 Signal Processing With Direct Computations on Compressively Sensed Data VLSI 2014 283 Signature Driven Hierarchical Post-Manufacture Tuning of RF Systems for Performance and Power VLSI 2014 284 Simplifying Clock Gating Logic by Matching Factored Forms VLSI 2014 285 SimRPU: A Simulation Environment for Reconfigurable Architecture Exploration VLSI 2014

- 23. www.pgembeddedsystems.com 286 Single-Bit Pseudoparallel Processing Low-Oversampling Delta–Sigma Modulator Suitable for SDR Wireless Transmitters VLSI 2014 287 Single-Port SRAM-Based Transpose Memory With Diagonal Data Mapping for Large Size 2- D DCT/IDCT VLSI 2014 288 Single-Source, Single-Destination Charge Migration in Hybrid Electrical Energy Storage Systems VLSI 2014 289 Skewed-Load Test Cubes Based on Functional Broadside Tests for a Low-Power Test Set VLSI 2014 290 Smart Reliable Network-on-Chip VLSI 2014 291 Software/Hardware Parallel Long-Period Random Number Generation Framework Based on the WELL Method VLSI 2014 292 Spech Processing on a Reconfigurable Analog Platform VLSI 2014 293 Split-SAR ADCs: Improved Linearity With Power and Speed Optimization VLSI 2014 294 Stability Estimation of a 6T-SRAM Cell Using a Nonlinear Regression VLSI 2014 295 Static Power Reduction Using Variation- Tolerant and Reconfigurable Multi-Mode Power Switches VLSI 2014 296 Statistical Framework for Designing On-Chip Thermal Sensing Infrastructure in Nanoscale Systems VLSI 2014 297 STT-MRAM Sensing CircuitWith Self-Body Biasing in Deep Submicron Technologies VLSI 2014 298 STT-RAM Cache Hierarchy With Multiretention MTJ Designs VLSI 2014

- 24. www.pgembeddedsystems.com 299 Super Fast Physics-Based Methodology for Accurate Memory Yield Prediction VLSI 2014 300 Supply Noise and Impedance of On-Chip Power Distribution Networks in ICs With Nonuniform Power Consumption and Interblock Decoupling Capacitors VLSI 2014 301 Supply-Noise Interactions Among Submodules Inside a Charge-Pump PLL VLSI 2014 302 Survey and Analysis of Delay-Locked Loops Used in DRAM Interfaces VLSI 2014 303 System Level Methodology for Interconnect Aware and Temperature Constrained Power Management of 3-D MP-SOCs VLSI 2014 304 Task Migrations for Distributed Thermal Management Considering Transient Effects VLSI 2014 305 Temperature Sensing RRAM Architecture for 3-D ICs VLSI 2014 306 Test Compaction by Sharing of Transparent- Scan Sequences Among Logic Blocks VLSI 2014 307 Testing of TSV-Induced Small Delay Faults for 3-D Integrated Circuits VLSI 2014 308 The Dependence of BTI and HCI-Induced Frequency Degradation on Interconnect Length and Its Circuit Level Implications VLSI 2014 309 Thirty Two-Stage CMOS TDI Image SensorWith On-Chip Analog Accumulator VLSI 2014 310 Three-Dimensional Chips Can Be Cool: Thermal Study of VeSFET-Based 3-D Chips VLSI 2014 311 Thwarting Scan-Based Attacks on Secure-ICs With On-Chip Comparison VLSI 2014 312 Time-Based All-Digital Technique for Analog Built-in Self-Test VLSI 2014

- 25. www.pgembeddedsystems.com 313 True-Damage-Aware Enumerative Coding for Improving NAND Flash Memory Endurance VLSI 2014 314 Tunnel FETs for Ultralow Voltage Digital VLSI Circuits: Part I—Device–Circuit Interaction and Evaluation at Device Level VLSI 2014 315 Tunnel FETs for Ultra-Low Voltage Digital VLSI Circuits: Part II–Evaluation at Circuit Level and Design Perspectives VLSI 2014 316 Ultra-High Throughput Low-Power Packet Classification VLSI 2014 317 UNION: A Unified Inter/Intrachip Optical Network for Chip Multiprocessors VLSI 2014 318 Unipolar Logic Gates Based on Spatial Wave-Function Switched FETs VLSI 2014 319 Use of SSTA Tools for Evaluating BTI Impact on Combinational Circuits VLSI 2014 320 Using Lifetime-Aware Progressive Programming to Improve SLC NAND Flash Memory Write Endurance VLSI 2014 321 Utilizing Circuit Structure for Scan Chain Diagnosis VLSI 2014 322 Variation-Aware Variable Latency Design VLSI 2014 323 Vector-Matrix Multiply and Winner-Take-All as an Analog Classifier VLSI 2014 324 VLSI Implementation of an Adaptive Edge- Enhanced Color Interpolation Processor for Real-Time Video Applications VLSI 2014 325 Watermarking in Hard Intellectual Property for Pre-Fab and Post-Fab Verification VLSI 2014 326 Way Stealing: A Unified Data Cache and Architecturally Visible Storage for Instruction Set Extensions VLSI 2014

- 26. www.pgembeddedsystems.com 327 WCET-Aware Re-Scheduling Register Allocation for Real-Time Embedded Systems With Clustered VLIW Architecture VLSI 2014 328 Wearout Resilience in NoCs Through an Aging Aware Adaptive Routing Algorithm VLSI 2014 329 Within-Die Delay Variation Measurement and Power Transient Analysis Using REBEL VLSI 2014 330 Worst Case Noise Prediction With Nonzero Current Transition Times for Power Grid Planning VLSI 2014 331 ZoneDefense: A Fault-Tolerant Routing for 2-D Meshes Without Virtual Channels VLSI 2014 332 Z-TCAM: An SRAM-based Architecture for TCAM VLSI 2014 333 Efficient Register Renaming and Recovery for High-Performance Processors VLSI 2014 334 A Real-Time Motion-Feature-Extraction VLSI Employing Digital-Pixel-Sensor-Based Parallel Architecture VLSI 2014 335 A Synergetic Use of Bloom Filters for Error Detection and Correction VLSI 2014 336 An Accuracy-Adjustment Fixed-Width Booth Multiplier Based on Multilevel Conditional Probability VLSI 2014 337 Evaluation and FPGA Implementation of Sparse Linear Solvers for Video Processing Applications VLSI 2014 338 Hardware Efficient Mixed Radix-25/16/9 FFT for LTE Systems VLSI 2014 339 High-Throughput and Low-Complexity BCH Decoding Architecture for Solid-State Drives VLSI 2014