Sistemas Digitales I - Primera Evaluación

•

0 j'aime•533 vues

Signaler

Partager

Signaler

Partager

Télécharger pour lire hors ligne

Contenu connexe

Tendances

Tendances (19)

En vedette

En vedette (10)

++Circuitos combinacionales -clase p repaso del examen-- 2

++Circuitos combinacionales -clase p repaso del examen-- 2

Similaire à Sistemas Digitales I - Primera Evaluación

Similaire à Sistemas Digitales I - Primera Evaluación (12)

09 sd capitulo vii circuitos logicos combinacionales

09 sd capitulo vii circuitos logicos combinacionales

Sumadores, codificadores, decodificadores, multiplexores, demultiplexores

Sumadores, codificadores, decodificadores, multiplexores, demultiplexores

Plus de johanna20

Plus de johanna20 (20)

Ciclo Contable De Una Empresa Comercial Parte Ii.Ppt(3parte)

Ciclo Contable De Una Empresa Comercial Parte Ii.Ppt(3parte)

Dernier

Dernier (20)

Evaluación y Mejora Continua Guía de Seguimiento y Monitoreo para Cursos de C...

Evaluación y Mejora Continua Guía de Seguimiento y Monitoreo para Cursos de C...

VAMOS MANAOS, análisis e historia de la empresa Manaos

VAMOS MANAOS, análisis e historia de la empresa Manaos

Determinación de la Demanda Tecnológica del cultivo de camu camu en las Provi...

Determinación de la Demanda Tecnológica del cultivo de camu camu en las Provi...

20240418-CambraSabadell-SesInf-AdopTecnologica-CasoPractico.pdf

20240418-CambraSabadell-SesInf-AdopTecnologica-CasoPractico.pdf

PRESENTACIÓN NOM-004-STPS-2020 SEGURIDAD EN MAQUINARIA

PRESENTACIÓN NOM-004-STPS-2020 SEGURIDAD EN MAQUINARIA

Habilidades de un ejecutivo y sus caracteristicas.pptx

Habilidades de un ejecutivo y sus caracteristicas.pptx

El MCP abre convocatoria de Monitoreo Estratégico y apoyo técnico

El MCP abre convocatoria de Monitoreo Estratégico y apoyo técnico

Sistemas Digitales I - Primera Evaluación

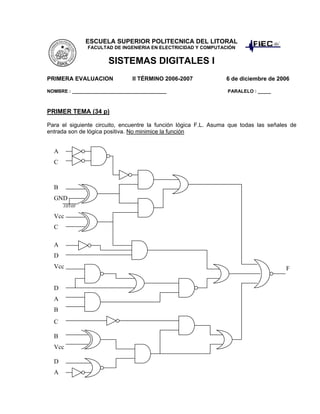

- 1. ESCUELA SUPERIOR POLITECNICA DEL LITORAL FACULTAD DE INGENIERIA EN ELECTRICIDAD Y COMPUTACIÓN SISTEMAS DIGITALES I PRIMERA EVALUACION II TÉRMINO 2006-2007 6 de diciembre de 2006 NOMBRE : ____________________________________ PARALELO : _____ PRIMER TEMA (34 p) Para el siguiente circuito, encuentre la función lógica F.L. Asuma que todas las señales de entrada son de lógica positiva. No minimice la función F A C B GND Vcc C A D Vcc D A B C B Vcc D A

- 2. SEGUNDO TEMA (33 p) Presentar la Tabla de Verdad de un Convertidor de Código cuya entrada B sea un código de 4 bits (B3 B2 B1 B0) que representa a los dígitos hexadecimales codificados en binario. Además tiene una entrada habilitadora de lógica negativa EN.L. Las salidas del convertidor de código son enviadas a un display de 7 segmentos que muestran el símbolo hexadecimal correspondiente al número binario ingresado. Los dígitos hexadecimales B y D se muestran en minúsculas para diferenciarlos de los números 8 y 0 respectivamente. Cuando EN.L = L, el Convertidor de Código muestra en el display el número binario convertido a hexadecimal. Por otro lado, cuando EN.L = H, el Convertidor de Código muestra totalmente apagado al display. Las entradas tienen la siguiente lógica: B3.H, B2.H, B1.H, B0.H, EN.L. Todas las salidas son de lógica positiva. a b c d e f g 4 g f e d c b a Convertidor de Código (B)2 EN.L TERCER TEMA (33p) Para cada una de las siguientes funciones lógicas, presente: a) Minimización de la función usando Mapas de Karnaugh b) Implementación de la función minimizada, mediante un programa en VHDL usando descripción RTL. Asuma que todas las señales trabajan en lógica positiva. 1. ∑∑ += φ )12,10,8,7,4,2()15,14,6,0(),,,( 1 1 DCBAF 2. DCBADCBDCACBADBDBCAF .........)...(.2 +++++= 3. WYXWZYXZYXWYXWZXWZYF .............3 +++++=