Electrónica digital

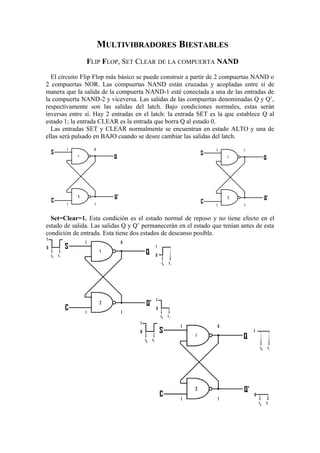

- 1. MULTIVIBRADORES BIESTABLES FLIP FLOP, SET CLEAR DE LA COMPUERTA NAND El circuito Flip Flop más básico se puede construir a partir de 2 compuertas NAND o 2 compuertas NOR. Las compuertas NAND están cruzadas y acopladas entre sí de manera que la salida de la compuerta NAND-1 esté conectada a una de las entradas de la compuerta NAND-2 y viceversa. Las salidas de las compuertas denominadas Q y Q’, respectivamente son las salidas del latch. Bajo condiciones normales, estas serán inversas entre sí. Hay 2 entradas en el latch: la entrada SET es la que establece Q al estado 1; la entrada CLEAR es la entrada que borra Q al estado 0. Las entradas SET y CLEAR normalmente se encuentran en estado ALTO y una de ellas será pulsado en BAJO cuando se desee cambiar las salidas del latch. Set=Clear=1. Esta condición es el estado normal de reposo y no tiene efecto en el estado de salida. Las salidas Q y Q’ permanecerán en el estado que tenían antes de esta condición de entrada. Esta tiene dos estados de descanso posible.

- 2. Set=0; Clear=1. Esto siempre causará que la salida pase al estado Q=1, donde permanecerá incluso después de que SET retorne a ALTO. Esto se llama establecimiento del latch. Set=1; Clear=0. Esto siempre producirá el estado Q=0, en el cual la salida permanecerá incluso después de que CLEAR retorne a ALTO. A esto se le llama restablecimiento del latch. Set=Clear=0. Esta condición intenta establecer y borrar al mismo tiempo y puede producir resultados ambiguos. No se debe de emplear.

- 3. SET CLEAR SALIDA 1 1 Sin cambio 0 1 Q=1 1 0 Q=0 0 0 Inválida NAND SR Se combinan 2 circuitos idénticos pero hacemos que funcione frente a la señal de reloj. Cuando CLK=0, S y R se desconectan de la entrada, ningún cambio en las señales de entrada pueden afectar su salida. Cuando CLK=1, S y R controlan el estado de cierre. El tiempo y la señal invertida de CLK al cierre auxiliar. NAND D Se derivan fácilmente de 2 contrapartes de RS. El único requisito es subsistir la entrada R por la versión invertida de la señal S, de tal modo queda D. Cuando la entrada de reloj baja a 0 y las salidas pueden cambiar de estado, siempre las toma al salir Q en el estado de la D entrada en el momento del borde de reloj.

- 4. FLIP FLOP, SET CLEAR DE LA COMPUERTA NOR El análisis de operabilidad del latch NOR se puede realizar de la misma manera que para el latch NAND. Set=Clear=0. Este es el estado normal de reposo y no tiene efecto en la salida. Q y Q’ permanecerán igual que antes de la condición. Set=1; Clear=0. Esto resultará Q=1, donde permanecerá después de que SET retorne a 0. Set=0; Clear=1. Esto resultará Q=0, donde permanecerá después de que CLEAR retorne a 0. Set=Clear=1. Esta condición trata de establecer y borrar. Es ambigua e inválida. SET CLEAR SALIDA 0 0 Sin cambio 1 0 Q=1 0 1 Q=0 1 1 Inválida NOR SR Entradas R y S para fijo y reset. Las entradas deben ser 0 lógico a evitar de eliminar la acción que trabaja, las entradas no se invierten. Para el circuito lógico latch NOR, ambas entradas deben ser 0 al igual que la segunda entrada, permitiendo que la salida se eleve hasta alcanzar el 1 lógico. No pueden entrar en el estado ALTO, puesto que, obligaría a la salida a estar en estado BAJO.

- 5. NOR D Dos circuitos cerrados almacenan señales D y D’; y aplican este al cierre de la salida. Mientras CLK es 0 lógico de los cambios de entrada D afectan en el estado BAJO y más en la salida. Otras puertas son bloqueadas en sus estados de salida por sus interconexiones. Cuando CLK=1 las dos puertas entran en 0. Esto aísla la eficacia. Cuando CLK=0 se traba ya que es ilegal o inválido e inmediatamente controlará el estado de salida.

- 6. RESUMEN

- 7. FLIP FLOP, CON SEÑALES DE RELOJ Los Flip Flop, los contadores y los registros necesitan recibir una señal de reloj para poder cumplir su función en los circuitos secuenciales. Los circuitos más conocidos para desempeñar esta función de reloj son los llamados osciladores o generadores de pulso. Los osciladores son circuitos que cambian el estado de su salida entre 0 y 1. Por esta razón estos circuitos son útiles para generar señales de reloj para los circuitos secuenciales síncronos y lo hacen mediante resistencias, condensadores, inversores y compuertas. El siguiente esquema, es un circuito generador de pulsos sin rebote y opera de forma manual, en la posición 1 la salida será 0 lógico y cuando se ubique en la posición 2 la salida será un 1 lógico. En el b y c se muestran dos circuitos que pueden implementar usando inversores y compuertas. La frecuencia de oscilación depende de los valores de la resistencia y el condensador. Se recomienda el uso de circuitos CMOS de la serie B ya que tienen tiempos menores.

- 8. OSCILADOR CON DISPARADOR DE SCHMITT La salida VO es una onda aproximadamente cuadrada y su forma depende de los valores R y C. Oscilador INTEGRADO FRECUENCIA VALOR R 7414 0.8/RC R ≤500W 74LS14 0.8/RC R ≤2W 74HC14 1.2/RC R ≤10mW MULTIVIBRADOR ESTABLE CON CI-555 Es un dispositivo de tecnología TTL que funciona de varios modos. Observa la manera de conectar los componentes al CI de forma que opere de multivibrador estable. La frecuencia de oscilación de la señal depende de los valores de la resistencia de RA, RB y C

- 9. La señal de salida es una onda cuadrada: RESUMEN

- 10. BIESTABLES CON RELOJ Los sistemas digitales pueden trabajar de forma síncrona y asíncrona. En los sistemas síncronos, las salidas de los circuitos lógicos pueden cambiar en cualquier momento en que varíen una o más de las entradas. El sistema asíncrono por lo general es más difícil diseñar y detectar las fallas que en un circuito síncrono. En los sistemas síncronos, los tiempos exactos en que cualquier salida puede cambiar de estado se determinan mediante una señal comúnmente llamada de reloj o clock (CLK). Esta por lo general es un tren de pulsos rectangulares o una onda cuadrada. La señal de reloj se distribuye en todas partes del sistema y la mayoría de las salidas pueden cambiar de estado, sólo cuando el reloj hace una transición. Las transiciones o bordes se indican en la siguiente figura. Las señales de reloj cuando cambian de 0 a 1 se llama transición con pendiente positiva (TPP). Cuando cambia de 1 a 0 se llama transición con pendiente negativa (TPN). La mayoría de los sistemas digitales son principalmente síncronos, ya que en los circuitos es más fácil de diseñar y detectar fallas; porque en las salidas pueden cambiar solo en un instante específico. A parte todas las partes y componentes se sincronizan gracias a la señal de reloj. Estas sincronizaciones son fáciles gracias al uso de FF sincronizados por reloj que se diseñan para cambiar estados en una u otra de las sincronizaciones.

- 11. APLICACIONES DE LOS FLIP FLOP Los FF disparados de borde (Sincronizados por Reloj) son dispositivos versátiles que se pueden usar en una amplia gama de aplicaciones; incluyendo el conteo y almacenamiento de datos binarios, transferencia de datos binarios de una ubicación a otra y mucho más. En casi, todas estas aplicaciones se emplea la sincronización por reloj de FF’s. Muchas de ellas caen en la categoría de Circuitos Secuenciales que son aquellos en el que las salidas siguen una frecuencia predeterminada de estado, dando lugar a un nuevo estado cada vez que ocurre un pulso de reloj. Los ejemplos más comunes son los osciladores y contadores.

- 12. CONTADORES Y REGISTROS CONTADORES ASÍNCRONOS Cuando cada salida de un FF excita la entrada CLK, a esta configuración se le llama contador asíncrono porque los FF no cambian de estado en sincronía exacta con los pulsos de reloj aplicados; sólo el FF A responde a los pulsos de reloj. El FF B debe esperar a que el FF A cambie de estado antes que él lo pueda hacer; el FF C debe esperar a que el FF B cambie y así sucesivamente… De esta manera hay un retardo entre las respuestas sucesivas de los FF’s, este retardo es del orden de 5 a 20 nanosegundos por FF. En algunos casos este retardo puede ocasionar problemas. Con frecuencia también se le llama contador de rizo debido a la forma en que los FF responden uno después de otro en una especie de efecto ondulatorio.

- 13. NÚMERO MOD El número MOD siempre es igual al número de estados por los cuales pasa el contador en cada ciclo completo, antes de que se recicle nuevamente a su estado inicial. El número MOD se puede incrementar agregando más FF al contador es decir: Número MOD=2N Donde N es el número de FF conectados en la configuración. CONTADORES CON NÚMEROS MOD<2N Algunos contadores están limitados a números MOD que son iguales a 2N donde N es el número de FF. En realidad este es el número MOD máximo que se puede obtener utilizando N FF. El contador básico se puede modificar para producir números MOD menores que 2N, permitiendo que el contador omita estados que normalmente son parte de la secuencia del contador. Uno de los métodos más comunes para hacer esto se ilustra a continuación, en la cual se muestra un contador de 3 bits. Sin considerar por un momento la compuerta NAND, se ve que el contador es un MOD-8 binario que contará en secuencia de 000 a 111. sin embargo la compuerta NAND modifica su funcionamiento. 1. La salida de NAND está conectada en las entradas asíncronas CLEAR de FF. Mientras la salida NAND sea alta, no tendrá efecto. Sin embargo cuando es baja borrará todos los FF, de modo que el contador pasará a 000. 2. Las entradas NAND son salidas de un FF B y C y por donde la salida será baja cuando B=C=1 esta condición pasará cuando el contador pase de estado 101 a 110 en TPN del pulso de entrada 6. En el estado bajo de la salida de la compuerta NAND inmediatamente (por lo general en nanosegundos) restablecerá al estado 000. una vez restablecidos, la salida de la compuerta NAND retornará a alto, ya que, la condición B=C=1 ya no existe. 3. La secuencia de conteo es:

- 14. Aunque el contador pase al estado 110, permanece allí solo unos nanosegundos antes de reciclarse a 000. Así que el contador cuenta de 000 (cero) a 101 (cinco) y luego se recicla. En esencia omite 110 y 111, de tal forma que pasa por seis estados y se trata de un contador MOD-6.

- 15. NÚMERO MOD ELECTRÓNICA DIGITAL II CONCEPTO DE MEMORIA El estudio de los dispositivos y sistemas de memoria tiene mucha terminología y veremos a continuación algunos conceptos: Celda de memoria: Dispositivo o circuito electrónico que se utiliza para almacenar un solo bit (0 ó 1) por ejemplo: un FF, un capacitor con carga etc. Palabra de memoria: Grupo de bits (celdas) en una memoria que representa instrucciones o datos de algún tipo. Por ejemplo: un registro que consta de 8 FF’s puede considerarse como una memoria que almacena una palabra de 8 bits, este varía de 4 a 64 bits según cada computadora. Byte: Término especial para una palabra de 8 bits para las microcomputadoras. Capacidad: Es la cantidad de bits que puede almacenar un dispositivo de memoria en particular. Densidad: Significa que puede almacenar más bits en la misma cantidad de espacio, o sea, más denso.