Short notes on digital electronics for specialist officer it exam by das sir,kolkata (08961556195)

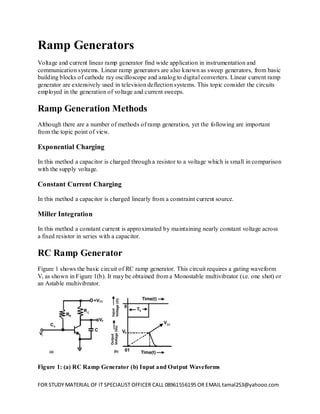

- 1. FOR STUDY MATERIAL OF IT SPECIALIST OFFICER CALL 08961556195 OR EMAIL tamal253@yahooo.com Ramp Generators Voltage and current linear ramp generator find wide application in instrumentation and communication systems. Linear ramp generators are also known as sweep generators, from basic building blocks of cathode ray oscilloscope and analog to digital converters. Linear current ramp generator are extensively used in television deflection systems. This topic consider the circuits employed in the generation of voltage and current sweeps. Ramp Generation Methods Although there are a number of methods of ramp generation, yet the following are important from the topic point of view. Exponential Charging In this method a capacitor is charged through a resistor to a voltage which is small in comparison with the supply voltage. Constant Current Charging In this method a capacitor is charged linearly from a constraint current source. Miller Integration In this method a constant current is approximated by maintaining nearly constant voltage across a fixed resistor in series with a capacitor. RC Ramp Generator Figure 1 shows the basic circuit of RC ramp generator. This circuit requires a gating waveform Vi as shown in Figure 1(b). It may be obtained from a Monostable multivibrator (i.e. one shot) or an Astable multivibrator. Figure 1: (a) RC Ramp Generator (b) Input and Output Waveforms

- 2. FOR STUDY MATERIAL OF IT SPECIALIST OFFICER CALL 08961556195 OR EMAIL tamal253@yahooo.com Initially the transistor is biased ON and operates in the saturation region. Thus when there is no input (i.e. Vi = 0 ), the output voltage is zero. Actually its value is equal to VCE (sat). When gating pulse i.e. a negative pulse is applied the transistor turns OFF. As a result of this, the capacitor voltage rises to a target value VCC with a time constant RCC. The charging curve ignoring VCE (sat) is given by the relation. If t / RCC << 1, then above relation may be expanded into a power series in t / RCC. Then taking only the first term of the power series, the output voltage. This equation represents an approximately linear waveform. It may be observed that the transistor switch is OFF only for the gating time (TS). At the end of time TS, the capacitor discharges and the voltage is again zero. Constant Current Ramp Generator Figure 2: Constant Current Ramp Generator Figure 2 shows a circuit to generate a ramp using constant current from a common base transistor. We know that except for very small value of collector to base voltage, teh collector current of a transistor in the common base configuration is very nearly constant, when the emitter current is held fixed. This characteristics may be used to generate a quite linear ramp by causing a constant current to flow into a capacitor. The value of emitter current is given by the relation.

- 3. FOR STUDY MATERIAL OF IT SPECIALIST OFFICER CALL 08961556195 OR EMAIL tamal253@yahooo.com IE = ( VEE - VEB ) / RE If the emitter to base voltage VEB remains constant with time after the switch S is opened, then the collector current will be a constant whose normal value, IC = hFB . IB = α IE The draw back of constant current ramp circuit is that it makes the sweep rate as a function of temperature. Since the emitter base junction voltage VBE for a fixed current decreases by about 2 mv/co, therefore the ramp speed increases with the temperature. UJT Relaxation Oscillator The UJT relaxation as a relaxation oscillator is shown in Figure 3, generates a voltage waveform VB1 (Figure 3), which can be applied as a triggering pulse to an SCR gate to turn on the SCR. When switch S is first closed, applying power to the circuit, capacitor C starts charging exponentially through R to the applied volatage V. The voltage across its the volatge VE applied to the emitter of UJT. When C has charged to the peak point voltage VP of the UJT, the UJT is turned on, decreasing greatly the effective resistance RB1 between the emitter and base1. A sharp pulse of current IE (limited only be R1) flows from base 1 into the emitter, discharging C. When the voltage across C has dropped to approximately 2V, the UJT turns off and the cycle is repeated. The waveforms in figure 3 shows the saw-tooth voltage VE, generated by the charging of C and the output pulse VB1 developed across R1, VB1 is the pulse which will be applied to the gate of an SCR to trigger the SCR. Figure 3: UJT Relaxation Oscillator The frequency f of the relaxation oscillator depends on the time constant RC and the characteristics of the UJT. For values of R1 < 100KΩ, the period of oscillation T is given approximately by the equation. T = 1 / f = RT CT1Ƞ (1 / 1 - Ƞ)

- 4. FOR STUDY MATERIAL OF IT SPECIALIST OFFICER CALL 08961556195 OR EMAIL tamal253@yahooo.com The value of R is limited to the range 3000Ω to 3MΩ. The supply voltage V normally used lies in the range of 10 to 35 V and etc Ƞ is called intrinsic standoff ratio of injunction transistor ( i.e. ratio of RB1 and RBB) Bootstrap Ramp Generator Figure 4: Bootstrap Ramp Generator Figure 4 shows the bootstrap ramp generator. In such case the transistor Q1 acts as a switch and Q2 as an emitter follower i.e. a unity gain amplifier. Suppose the transistor Q1 is ON and Q2 is OFF. Therefore the capacitor C1 is charged to VCC through the diode forward resistance RE. At this instant, the output voltage Vo is zero. When negative pulse as shown in Figure 4 is applied to the base of transistor Q2 it turns OFF. Since transistor Q2 is an emitter follower, therefore the output voltage (Vo) is the same as the base voltage of transistor Q2. Thus as the transistor Q1 turns OFF, the capacitor C1 starts charging this capacitor C through resistor R. As a result of this , both the base voltage of Q2 and the output voltage begins to increase from zero. As the output voltage increases, the diode D becomes reverse biased. It is because of the fact that the output voltage is coupled through the capacitor C1 to the diode. Since the value of capacitor C1 is much larger than that of capacitor C, therefore the voltage across capacitor C1 practically remains constant. Thus the voltage drop across the resistor R also remains constant because of this, the current iR through the resistor also remains constant. This causes the voltage across the capacitor C (and hence the output voltage) to increase linearly with time. Miller Integrator Ramp Generator

- 5. FOR STUDY MATERIAL OF IT SPECIALIST OFFICER CALL 08961556195 OR EMAIL tamal253@yahooo.com Figure 5: Miller Integrator Ramp Generator Figure 5 shows the miller integration ramp generator. It is also called Miller integrator. In such a case transistor Q1 acts as a switch and transistor Q2 is a common emitter amplifier i.e. a high gain amplifier. Suppose that initially, the transistor Q1 is ON and Q2 is OFF. At this instant, the voltage across the capacitor and the output voltage is equal to VCC. Let us suppose that a pulse of negative polarity as shown in Figure 5(b) is applied at the base of the transistor Q1. As a result of this, the emitter-base junction of the transistor Q1 is reverse biased and it turns OFF. This causes the transistor Q2 to turn ON. As the transistor Q2 conducts, the output voltage begins to decrease towards zero. Since the capacitor C is coupled to the base of transistor Q2 therefore the rate of decrease of the output voltage is controlled by the rate of discharge of capacitor C. The time constant of the discharge is RBC. As the value of time constant is very large, therefore the discharge current remains constant. Hence a result of this, the rundown of the collector voltage is linear. When the input pulse is removed the transistor Q1 turns ON and Q2 turns OFF. It will be interesting to know that as the transistor Q1 turns OFF, the capacitor C charges quickly through resistor RC to VCC with the time constant equal to RCC. The waveform of the generated ramp or the output voltage is shown in Figure 5(b). The Miller integrator provide an excellent ramp linearity as compared to the other ramp circuits. ************************************************************************* ******** Clocked or Triggered Flip Flop A clock pulse used to operate a flip flop is illustrated in Figure 1(a). The pulse goes from a low level 0 volt, the positive logical 0 condition, to a high level ( +5 volts , the positive logic logical

- 6. FOR STUDY MATERIAL OF IT SPECIALIST OFFICER CALL 08961556195 OR EMAIL tamal253@yahooo.com 1 condition going between the two logic levels at a fixed frequency rate. A clock signal as seen in Figure 1(a) has two transitions, one from low to high level the other from high to low level. For positive logic operation we define the low to high transition as the leading edge of the clock signal (Figure 1(b)) while the transition from high to low is called the clock trailing edge (Figure 1(c)). Figure 1: Clock Waveform (a) Full Clock Pulse (b) Leading edge (c) Trailing edge Some flip flop circuits are triggered by the clock leading edge while other units are triggered on the clock trailing edge. The particular flip flop specifications will provide this information as we shall see. Some flip flop are other logic units are triggered when the clock reaches prescribed voltage levels or goes from one voltage level to another usually without regard to voltage rise or fall time. A circuit clocked by the leading edge, as in Figure 1 (b) is referred to as being positive edge triggered while another circuit triggering on the trailing edge, as in Figure 1(c) is negative edge triggered. Positive Edge Triggered Flip Flop In positive edge triggered flip flops the clock samples the input line at the positive edge (rising edge or leading edge) of the clock pulse. The state of the output of the flip flop is set or reset depending upon the state of the input at positive edge of the clock. This state of the output remains for one clock cycle and the clock again samples the input line on the next positive edge of the clock. A symbolic representation for positive edge triggering has been shown in Figure 2. The arrow head at clock terminal indicates positive edge triggering. The arrow head symbol is termed as dynamic signal indicator.

- 7. FOR STUDY MATERIAL OF IT SPECIALIST OFFICER CALL 08961556195 OR EMAIL tamal253@yahooo.com Figure 2: Positive Edge Triggered JK Flip Flop Negative Edge Triggered Flip Flop In negative edge triggered flip flops the clock samples the input lines at the negative edge (falling edge or trailing edge) of the clock pulse. The output of the flip flop is set or reset at the negative edge of the clock pulse. A symbolic representation of negative edge triggering has been shown in Figure 3. A small circle is put before the arrow head to indicate negative edge triggering. Figure 3: Negative Edge Triggered Flip Flop

- 8. FOR STUDY MATERIAL OF IT SPECIALIST OFFICER CALL 08961556195 OR EMAIL tamal253@yahooo.com Level Triggered Flip Flops The level triggering may be of two types: 1. Positive Triggering 2. Negative Triggering In the positive triggering the clock samples the input line as the clock pulse is positive, and sets/resets the flip flop according to the state of the input lines. When clock is low the outputs does not change it remains in the previous state which was at the end of the positive clock pulse. Similarly, in negative triggering the clock samples the input line as the clock is negative and sets/resets the flip flop according to the state of the input lines. When clock is high the output does not change, it remains in the previous state which was at the end of the negative clock pulse. ************************************************************************* ******** COUNTERS Counting is frequently required in digital computers and other digital systems to record the number of events occurring in a specified interval of time. Normally an electronic counter is used for counting the number of pulses coming at the input line in a specified time period. The counter must possess memory since it has to remember its past states. As with other sequential logic circuits counters can be synchronous or asynchronous. As the name suggests, it is a circuit which counts. The main purpose of the counter is to record the number of occurrence of some input. There are many types of counter both binary and decimal. Commonly used counters are 1. Binary Ripple Counter 2. Ring Counter

- 9. FOR STUDY MATERIAL OF IT SPECIALIST OFFICER CALL 08961556195 OR EMAIL tamal253@yahooo.com 3. BCD Counter 4. Decade counter 5. Up down Counter 6. Frequency Counter Binary Ripple Counter A binary ripple counter is generally using bistable multivibrator circuits so that cache input applied to the counter causes the count to advance or decrease. A basic counter circuit is shown in Figure 1 using two triggered (T-type) flip flop stages. Each clock pulse applied to the T-input causes the stage to toggle. The Q and output terminals are always logically opposite. If the Q output is logical 1 (SET), the output is then logical 0. If the Q output is logical 0 (REST), then the output is logical 1. The clock input causes the flip flop to toggle or change stage once clock pulse Figure 2 (a) shows the clock input signal and Q output signal. Notice that the circuit used in this case toggles on the trailing edge of the clock signal (when logic signal goes from 1 to 0). Referring back to Figure 1 the Q output of the first stage (called the 2o stage or units position stage) is used here as the toggle input to the second stage (called the 21 or two’s position stage). The Q output from the two successive stage are marked A and B, respectively, to differentiate them. Notice that the output of each stage is marked with a negative bar over the letter designation, so that whatever logical stage A is at, is the opposite logical state. Since the Q output (A signal) from the first stage triggers the second stage, the second stage changes state only when the Q output of first stage goes from logical 1 to logical 0 as shown in Figure 2(b).

- 10. FOR STUDY MATERIAL OF IT SPECIALIST OFFICER CALL 08961556195 OR EMAIL tamal253@yahooo.com Table 1 COUNT FOR 2-STAGE BINARY COUNTER Input Pulses 2n Output (B) 2n Output (A) 0 0 0 1 0 1 2 1 0 3 1 1 4 or 0 0 0 An arrow is included on the waveform of stage A as a reminder that it triggers stage B only on a trailing edge (1 or 0 logical change). Notice that the output waveform of succeeding stage

- 11. FOR STUDY MATERIAL OF IT SPECIALIST OFFICER CALL 08961556195 OR EMAIL tamal253@yahooo.com operates half as fast as its input. To see that this circuit operates as a binary counter a table can be prepared to show the Q output states after each clock pulse is applied. Table 1 shows this operation for the circuit of Figure 1. To see how a counter is made using more stage considers the 4 stage counter of Figure 3. The counter is simply made with the Q output of each state connected as the toggle input to the succeeding state. With four stages the counter cycle will repeat every sixteen clock pulses. In general there are 2n counts with an n-stage counter. For the four stages used here the count goes 24 or 16 steps as a rule, for a binary counter. Number of counts = N = 2n Where, n = number of counter stage. A six stage counter n = 6 would be provide a count that repeats every N = 26 = 64 counts. A ten-stage counter (n = 10) would recycle every N = 210 = 1024 counts. Returning to the 4 stage counter Figure 3. Arrows are included in the table to act as reminder that a change from 1 to 0 results in a succeeding stage being toggled. Notice in Table 2 that the 20 stage toggles on every four clock pulses. The 21 stage toggles every two clock pulses, the 22 stage toggles every clock pulses. This implies that we can associate a weighting value to the stage output. The 23 stage output can be considered of value eight, the 22 output equal four, 21 output equals two and 20 equals one. We can see then that the binary state of the counter can be read as a number equals to the pulses input count. After the counter reaches the count 111, which is the largest count obtained using four stages, the next input pulse causes the counter to go to 000 and new count cycle repeats. Table 2 COUNT UP OPERATION (FOUR STAGES) Input Pulses 23Output (D) 22 Output (C) 21 Output (B) 20 Output (A)

- 12. FOR STUDY MATERIAL OF IT SPECIALIST OFFICER CALL 08961556195 OR EMAIL tamal253@yahooo.com 0 0 0 0 0 1 0 0 0 1 2 0 0 1 0 3 0 0 1 1 4 0 1 0 0 5 0 1 0 1 6 0 1 1 0 7 0 1 1 1 8 1 0 0 0 9 1 0 0 1 10 1 0 1 0 11 1 0 1 1 12 1 1 0 0 13 1 1 0 1 14 1 1 1 0 15 1 1 1 1 16 or 0 0 0 0 0 It should be obvious that the count sequence is an increasing binary count for each input clock pulse. Then the counter is also referred to as a count up binary counter the resulting output waveform for each stage is shown in Figure 4. The count is called a ripple counter because of the rippling change of state from lower order to higher order stages when the count changes i.e. the 20 stage toggles the 21 stage, which may toggle the 22 stage etc. Count-Down Counter A simple four stage count down counter is shown is Figure 5. The Q-output of each stage is now used as trigger input to the following stage. It still use the Q-output as indication the state of each stage as shown in the count table (table 3). Starting with the counter RESET Q-output of each

- 13. FOR STUDY MATERIAL OF IT SPECIALIST OFFICER CALL 08961556195 OR EMAIL tamal253@yahooo.com stage is logical-0, the first input pulse causes stage A to toggle form 0 to 1. The trigger pulse to stage B being taken from the Q-output of stage A goes from 1 to 0 at this time so that stage B is also toggled. The Q-output of stage B going from 1 to 0 causes stage C to be toggled, which then causes stage D to toggle. Figure 5: Four Stage Count-down Binary Counter Table 5: Count-down Counter of Figure 5 Input Pulse D C B A Decimal Output Count 0 0 0 0 0 0 (or 16) 1 1 1 1 1 15 2 1 1 1 0 14 3 1 1 0 1 13 4 1 1 0 0 12 5 1 0 1 1 11 6 1 0 1 0 10 7 1 0 0 1 9 8 1 0 0 0 8 9 0 1 1 1 7 10 0 1 1 0 6 11 0 1 0 1 5 12 0 1 0 0 4 13 0 0 0 1 3 14 0 0 1 0 2 15 0 0 0 1 1 16 0 0 0 0 0 (or 16) 1 1 1 1 15 Table 5 shows, then that the count goes to 1111. The next input puse toggles A. Since the signal A (used to toggle stage B) now goes input 0 to 1. Stage B and C and D remain the same, the count now being 1110. Thus, the count has deceased as a result of the input trigger pulse. In fact the count will countinue to decrease by one binary count for each input trigger pulse applied.

- 14. FOR STUDY MATERIAL OF IT SPECIALIST OFFICER CALL 08961556195 OR EMAIL tamal253@yahooo.com Table 5 shows that the count will decrease to 0000 after which it will go to 1111 to repeat another count circle. Using four stage the count down counter provides a full cut off N = 2n = 24 = 16 count but in decreasing count mode of operation. Decade Counter A decade counter is the one which goes through 10 unique combinations of outputs and then resets as the clock proceeds. We may use some sort of a feedback in a 4-bit binary counter to skip any six of the sixteen possible output states from 0000 to 1111 to get to a decade counter. A decade counter does not necessarily count from 0000 to 1001 it could count as 0000,0001, 0010, 1000, 1001, 1010, 1011, 1110, 1111, 0000, 0001 and so on. Figure 6 shows a decade counter having a binary count that is always equivalent to the input pulse count. The circuit is essentially, a ripple counter which count up to 16. We desire however, a circuit operation in which the count advance from 0 to 9 and then reset to 0 for a new cycle. This reset is a accomplished at the desired count as follows. 1. With counter REST count = 0000 the counter is ready to stage counter cycle. 2. Input pulses advance counter in binary sequence up to count of a (count = 1001) 3. The next count pulse advance the count to 10 count = 1010. A logic NAND gate decodes the count of 10 providing a level change at that time to trigger the one shot unit which then resets all counter stages. Thus, the pulse after the counter is at count = 9, effectively results in the counter going to count = 0. Figure 6: Decade Counter Table 6: Decade Counter Truth Table Input Pulses D C B A 0 0 0 0 0

- 15. FOR STUDY MATERIAL OF IT SPECIALIST OFFICER CALL 08961556195 OR EMAIL tamal253@yahooo.com Table 6: Decade Counter Truth Table Input Pulses D C B A 1 0 0 0 1 2 0 0 1 0 3 0 0 1 1 4 0 1 0 0 5 0 1 0 1 6 0 1 1 0 7 0 1 1 1 8 1 0 0 0 9 1 0 0 1 10 1 0 1 0 0 0 0 0 0 Table 6 provides a count table showing the binary count equivalent to the decimal count of input pulses. The table also shows that the count goes momentarily count from nine (1001) to ten (1010) before resetting to zero(0000). The NAND gate provides an output of 1 until the count reach ten. The count of ten is decoded (or sensed in this case ) by using logic inputs that are all 1 at the count of ten. When the count becomes ten the NAND gate output goes to logical 0, providing a 1 to 0 logic change to trigger the one shot unit, which then provides a short pulse to reset all counter stages. The Q signal is used since it is normally high and goes low during the one shot timing period the flip flop in this circuit being reset by a low signal level (active low clearing). The one shot pulse need only be long enough so that slowest counter stage resets. Actually, at this time only the 21and 23 stage need be reset, but all stages are reset to insure that a new cycle at the count 0000. Ring Counter The ring counter is the simplest example of a shift register. The simplest counter is called a Ring counter. The ring counter contains only one logical 1 or 0 which it circulates. The total cycle length is equal to the number of stages. The ring counter is useful in applications where count has to be recognized in order to perform some other logical operation. Since only one output is ever at logic 1 at given time extra logic gates are not required to decode the counts and the flip flop outputs may be used directly to perform the required operation.

- 16. FOR STUDY MATERIAL OF IT SPECIALIST OFFICER CALL 08961556195 OR EMAIL tamal253@yahooo.com Figure 7: Simple Ring Counter Note that in the above diagram the Reset will reset Q2, Q3 and Q4 but will put Q1 to a logic 1 state. This 1 will circulate when clock pulses are applied. Table 7: Ring Counter Truth Table Clock 01 02 03 04 1 1 0 0 0 2 0 1 0 0 3 0 0 1 0 4 0 0 0 1 5 1 0 0 0 Up-Down Counter An up down counter is a bi-directional counter and it can be made to count upwards as well as downwards. In other words an up down counter is one which can provide oth count up and down counts operations in a single unit. In the previous section it was seen that if triggering pulses are obtained from output the counter is a count up and if the triggering pulses are obtained from outputs, the counter is a count down. Figure 8 gives an up down counter. When the count up signal is high the AND gate connecting Q output and count up siganl gives and output 1 which passes through the OR gate to trigger the next flip flop. This results in the count up operation. Similarly a signal from count down line will result the circuit to act as a down counter.

- 17. FOR STUDY MATERIAL OF IT SPECIALIST OFFICER CALL 08961556195 OR EMAIL tamal253@yahooo.com Figure 8: Up Down Counter BCD Counter It is a special case of a decade counter in which the counter counts 0000 to 1001 and then resets. The output weights of the flip flops in these counters are in accordance with 8421 code. For instance, at the end of seventh clock pulse, the output sequence will be 0111 (Decimal euivalent of 0111 as per 8421 code is 7). These counters will thus be different from other decade counters that provide the same count by using some kind of forced feedback to skip some of the natural binary counts Figure 9 shows a counter of the BCD type. Figure 9: BCD Counter Frequency Counter Frequency counter is a digital device which can be used to measure the frequency of the periodic waveforms. The block diagram of frequency counter is shown in Figure 10. Figure 10: Frequency Counter

- 18. FOR STUDY MATERIAL OF IT SPECIALIST OFFICER CALL 08961556195 OR EMAIL tamal253@yahooo.com A signal having time period t applied at one of the input terminal of AND gate. While a unknown signal is also applied at the other input terminal of the AND gate. Hence, it is used as a clock for counter indicates the frequency of the unknown signal in respect to this time period. The time interval of the counter may be called contents. Let us suppose that time period of gate signal is one second and unknown signal is a square wave of 250 Hertz. In this condition counter counts 250 at the end of one second. This will be frequency of unknown signal. ************************************************************************* ********* Shift Registers A register is a device which is used to store information. Flip flops are often used to make a register. Each flip flop can store 1-bit of information and therefore for storing a n-bit word n-flip- flops are required in the register for example a computer employing 16-bit word length requires 16 flip-flops to hold the number before it is manipulated. The input to a register or output from it may be either in serial or parallel form depending upon the requirement. Shift Register A shift register is a storage device that used to store binary data. When a number of flip flop are connected in series it is called a register. A single flip flop is supposed to stay in one of the two stable states 1 or 0 or in other words the flip flop contains a number 1 or 0 depending upon the state in which it is. A register will thus contain a series of bits which can be termed as a word or a byte. If in these registers the connection is done in such a way that the output of one of the flip flop forms in input to other, it is known as a shift register. The data in a shift register is moved serially (one bit at a time). The shift register can be built using RS, JK or D flip-flops various types of shift registers are available some of them are given as under. 1. Shift Left Register 2. Shift Right Register 3. Shift Around Register 4. Bi-directional Shift Register

- 19. FOR STUDY MATERIAL OF IT SPECIALIST OFFICER CALL 08961556195 OR EMAIL tamal253@yahooo.com Shift Left Register A four stage shift-left register is shown in figure 1. The individual stages are JK flip-flops. Notice that the date input consists of opposite binary signals, the reference data signal going to the J input and the opposite data signal going to the K input. For the D-type stage the single data input line is connected as the D-input. Figure 1: Shift Registers (a) JK (b) D-type The shift pulse is applied to each stage operating each simultaneously. When the shift pulse occurs the data input is shifted in to that stage. Each stage is set or reset corresponding to the input data at the time the shift pulse occurs. Thus the input data bit is shift in to stage A by the first shift pulse. At the same time the data of stage A is shifted into the stage B and so on for the following stages. At each shift pulse data stored in the register stages shifts left by one stage. New data shifted into stage A, whereas the data present in stage D is shifted out to the left for use by some other shift register or computer unit. For example consider starting with all stages reset all Q-outputs to logical 0 and applying steady logical 1 input as data input stage A. Table 1 shows the data in each stage after each of four shift pulses. Notice table 2 how the logical 1 input first shifts into stage A and then left to stage D after four shift pulses. As another example consider shifting alternate 0 and 1 data into stage A starting with all stages 1. Table 2 shows the data in each stage after each of four shift pulses. Finally as a third example of shift register operation. Consider starting with the count in step 4 of table 2 and applying four more shift pulses with placing a steady logical 0 input as data input to stage A table 3 show this operation.

- 20. FOR STUDY MATERIAL OF IT SPECIALIST OFFICER CALL 08961556195 OR EMAIL tamal253@yahooo.com Table 1 OPERATION OF SHIFT-LEFT REGISTER Shift Pulse D C B A 0 0 0 0 0 1 0 0 0 1 2 0 0 1 1 3 0 1 1 1 4 1 1 1 1 Table 2 OPERATION OF SHIFT-LEFT REGISTER Shift Pulse D C B A 0 1 1 1 1 1 1 1 1 0 2 1 1 0 1 3 1 0 1 0 4 0 1 0 1 Table 3 OPERATION OF SHIFT-LEFT REGISTER Shift Pulse D C B A 0 0 1 1 1 1 1 1 1 0 2 0 1 0 0 3 1 0 0 0 4 0 1 0 0 Consider the data in stage A as least significant (2o) bits (LSB) and those in stage D as most significant bits MSB shift-left register operation provides data starting with MSB bit. A few points should be made clear in register operation. 1. The number of shift pulses be the same as the number of shift in register stages.Consider the data in stage A as least significant (2o) bits (LSB) and those in stage D as most significant bits MSB shift-left register operation provides data starting with MSB bit. A few points should be made clear in register operation.

- 21. FOR STUDY MATERIAL OF IT SPECIALIST OFFICER CALL 08961556195 OR EMAIL tamal253@yahooo.com 2. Changes in the shift stages take place simultaneously but only the shift pulse occurs. 3. Data shift into a register stage depends only on what logic levels were present at input terminals J and K at the time the shift pulse occurred. Changes that then take place resulting from data shifted will not affect the next stage until the next shift pulse occurs. Shift Right Register Sometimes it is necessary to shift the least significant digit first, as when addition is to be carried out serially. In that case a shift right register is used as in Figure 2 input data is applied to stage D and shifted right. The shift operation is the same as discussed in Shift Left Register except that data transfers to the right. Table 4 shows the action of shifting all logical 1 inputs into an initially reset shift register. In addition to shifting data register, data into a register data is also of a register. Table 5 shows register operation for an initial value of 1101. Notice that the output from stage A contains the binary number each bit (starting initially with LSB) appearing at the output of each shift step. In the present example it was assumed that logical 0 was shifted as input data so that after four shift pulses have occurred the data has passed through the register and the stages are left reset after the fourth shift pulse. Figure 2: Shift Right Register (a) D-type (b) JK Table 4 SHIFT RIGHT OPERATION Shift Pulse D C B A 0 0 0 0 0

- 22. FOR STUDY MATERIAL OF IT SPECIALIST OFFICER CALL 08961556195 OR EMAIL tamal253@yahooo.com 1 1 0 0 0 2 1 1 0 0 3 1 1 1 0 4 1 1 1 1 Table 5 SHIFTED OUT OF SHIFT RIGHT REGISTER Shift Pulse D C B A 0 1 1 0 1 1 0 1 1 0 2 0 0 1 1 3 0 0 0 1 4 0 0 0 0 Shift Around Register When it is required to shift data out of a register with out losing the initial data a shift around register can be used. Figure 3 shows the JK stages in a shift right, shift around register connection. All that was needed was connection of the input of stage A as into the stage D. Then as four shift pulses move the binary data into stage A, the data being shift out of stage A is shift into stage D and returns into the register. Figure 3: Shift Right Around Register Table 6 AROUND ACTION WITH SHIFT RIGHT REGISTER Shift Pulse D C B A 0 1 1 0 1

- 23. FOR STUDY MATERIAL OF IT SPECIALIST OFFICER CALL 08961556195 OR EMAIL tamal253@yahooo.com 1 1 1 1 0 2 0 1 1 1 3 1 0 1 1 4 1 1 0 1 Table 6 shows the result of shifting the binary number 1101 through (and around) the shift register. Notice that after four shift pulses have occurred the initial value is again in the shift register. To see how any action has taken place other than just shifting the number around there register consider tow shift register stages as in Figure 4 each register, shows in block form, is a four stage shift right register. Externally connecting the A and output of register 1 back to the data input of the same register results in it acting as a shift around register. The logic signal appearing at output A and is also shifted into register 2. Table 7 shows the operation of starting with 1101 in register 1 and 000 in register 2 if the shift around of register 1 were not used and data input were left uncommented (logical 0) then after four shift pulses the data originally in register 1 would be in register 2, with register 1 then reset. Figure 4: Two Shift Right Registers Table 7 OPERATION OF SHIFT REGISTERS OF FIGURE 4 Shift Pulse D C B A H G F E 0 1 1 0 1 0 0 0 0 1 1 1 1 0 1 0 0 0 2 0 1 1 1 0 1 0 0

- 24. FOR STUDY MATERIAL OF IT SPECIALIST OFFICER CALL 08961556195 OR EMAIL tamal253@yahooo.com 3 1 0 1 1 1 0 1 0 4 1 1 0 1 1 1 0 1 Bidirectional Shift Register A bidirectional shift register is one which can do both the shift left and shift right operations. The arrangement is shown in Figure 5 there are two separate sets of flip-flops. The following steps are controlled by a clock sequentially. The clock and timing arrangements have not been shown in the figure. The lower register is the one in which the data being shifted right or left. The upper register is being used as a temporary storage. The steps are as follows. 1. The contents of the lower register are gated up directly to the upper register, which is assumed to have been cleared previously. This is a parallel transfer of data and is achieved by the first pulse or gate up pulse applied as the gate up terminals. 2. All the lower registers are reset i.e. set =0 by giving a pulse at the reset terminals. 3. The contents of the upper register are gate down to the lower register either one position to the right or to the left as desired. This is again a parallel transfer of data. 4. The upper register is reset for the next shift operation. Asynchronous and Synchronous Shift Registers Asynchronous circuits changes state each time the input changes the state, while synchronous circuit changes state only when triggered by a momentary change in the input signal. This momentary change is called triggering. Shift registers are made of flip flops their operation depends upon the state at the flip flop and their operation depends upon the state at the flip flops. Flip flops changes their states due to triggering when flip flop change their state on the base of input pulse then it is called Edge triggering. In edge triggering flip flop change its state on the basses of Leading edge or trailing edge. When flip flop works on the bases of change in DC level, that is called Asynchronous Triggering. And the shift registers work on this principle are called Asynchronous shift registers. On the other hand, shift registers changes their state only when triggered by clock pulse are called Synchronous shift registers these type of shift registers usually used in counters. ************************************************************************* *******

- 25. FOR STUDY MATERIAL OF IT SPECIALIST OFFICER CALL 08961556195 OR EMAIL tamal253@yahooo.com Intel 8085 8-bit Microprocessor Intel 8085 is an 8-bit, NMOS microprocessor. It is a 40 pin C package fabricated on a single LSI chip. The Intel 8085A uses a single +5V D.C supply for its operation. Its clock speed is about 3 MHz. The clock cycle is of 320 ns. The time for the back cycle of the Intel 8085 A-2 is 200 ns. It has 80 basic instructions and 246 opcodes. Figure 1 shows the block diagram of Intel 8085A. It consists of three main sections, an arithmetic and logic unit a timing and control unit and several registers. These important sections are described as under. ALU The arithmetic and logic unit, ALU performs the following arithmetic and logic operations. 1. Addition 2. Subtraction 3. Logical AND 4. Logical OR 5. Logical EXCLUSIVE OR 6. Complement (logical NOT) 7. Increment (add 1) 8. Decrement (subtract 1) 9. Left shift (add input to itself) 10. Clear (result is zero) Timing and Control Unit The timing and control unit is a section of the CPU. It generates timing and control signals which are necessary for the execution of instructions. It controls provides status, control and timing signals which are required for the operation of memory and I/O devices. It controls the entire operation of the microprocessor and peripherals consented to it. Thus it is seen that control unit of the CPU acts as a brain of the computer. Registers Figure 1 show the various registers of Intel 8085A. Registers are small memories within the CPU. They are used by the microprocessor for temporary storage and manipulation of data and instructions. Data remain in the registers till they are sent to the memory or I/O devices. In a large computer the number of registers is more and hence the program requires less transfer of data to and from the memory. In small computers the number of registers is small due to the limited size of the chip. Intel 8085 microprocessor has the following registers. 1. One 8-bit accumulator (ACC) i.e. register A. 2. Six 8-bit general purpose registers. These are B, C, D, E, H and L. 3. One 16-bit program counter, PC.

- 26. FOR STUDY MATERIAL OF IT SPECIALIST OFFICER CALL 08961556195 OR EMAIL tamal253@yahooo.com 4. Instruction register 5. Status register 6. Temporary register. Figure 1: Intel 8085 Microprocessor Internal Block Diagram In addition to the above mentioned registers Intel 8085 microprocessor also contains address buffer and data/address buffer. Figure 1 the block diagram of Intel 8085. The program counter PC, contains the address of the next instruction. The CPU fetches an instruction from the

- 27. FOR STUDY MATERIAL OF IT SPECIALIST OFFICER CALL 08961556195 OR EMAIL tamal253@yahooo.com memory executes it and increments the content of the program counter. Thus in the next instruction cycle it will fetch next instruction. Instructions are executed sequentially unless an instruction changes the content of the program counter. The instruction register holds the instruction until it is decoded. This cannot be accessed by the programmer. The stack pointer SP, holds the address of the stack top. The stack is a sequence of memory locations defined by the programmer. The stack is used to save the content of a register during the execution of a program. The last memory location of the occupied portion of the stack is called stack top. For example, suppose that the stack location 2000 is the stack top which is contained by the stack pointer. Now the contents of B-C pair so to be saved. This will be stored in the stack locations 1999 and 1998. The new stack top will be stored in the stack pointer. The new stack top is the location 1998. If more data come they will be stored in the stack location 1997 onwards. Suppose the contents of H-L pair is to be pushed. They will go in 1997 and 1996. The new stack top will be the stack location 1996 and vacant locations are 1995 onward. There are six 8-bit registers which are used for general purpose as desired by the programmer. These 8-bit registers are A, B, C, D, E, H and L. To handle 16-bit data two 8-bit registers can be combined. The combination of two 8-bit registers is called a register pair. The valid register pairs in Intel 8085 are B-C, D-E and H-L. The H-L pair is used to address memories. The register A is accumulator in Intel 8080/8085. This is for temporary storage used during the execution to a program. It holds one of the operands. The other operand may be either in the memory or in one of the registers. There is a set of five flip-flops which act as status flags. Each of these flip-flop holds 1-bit flag at indicate certain condition which arises during arithmetic and logic operations. The following status flags have been provided in Intel 8085. 1. CARRY (CS) 2. ZERO (Z) 3. SIGN (S) 4. PARITY (P) 5. AUXILIARY CARRY (AC) Carry (CS) The carry status flag holds carry out of the most significant bit resulting from the execution of an arithmetic operation. If there is a carry from addition or a borrow from subtraction or comparison, the carry flag CS is set to 1, otherwise 0. Zero (Z) The zero status flag Z is set to 1 if the result of an arithmetic or logical operation is zero. For non-zero result it is set to 0. Sign (S)

- 28. FOR STUDY MATERIAL OF IT SPECIALIST OFFICER CALL 08961556195 OR EMAIL tamal253@yahooo.com The sign status flag is set to 1 if the most significant bit of the result of an arithmetic or logical operation is 1 otherwise 0. Parity (P) The parity status flag is set to 1 when result of the operation contains even number of 1's. It is set to zero when there is odd number of 1's. Auxiliary Carry (AC) The auxiliary carry status flag holds carry out of bit 3 to 4 resulting from the execution of an arithmetic operation. Figure 3 shows the status flags for ADD operation. Take an example of the instruction ADD B. The execution of the instruction ADD B will add the content of the register B to the contents of the accumulator. Suppose the contents of the accumulator and register B are C.B and ES respectively. Now C.B and ES are added and the result is 01, B4. As the accumulator is an 8-bit register B4 remains in the accumulator and there is a carry. The various status flags are shown in figure 2. Figure 3: Status Flag for ADD Operation

- 29. FOR STUDY MATERIAL OF IT SPECIALIST OFFICER CALL 08961556195 OR EMAIL tamal253@yahooo.com PSW In figure 2 Five bits indicate the five status flags and three bits are undefined. The combination of these 8 bits is called Program Status Word (PSW). PSW and the accumulator are treated as a 16-bit unit for stack operations. Data and Address Bus The Intel 8085 is an 8-bit microprocessor. Its data bus is 8-bit wide and hence, 8 bits of data can be transmitted in parallel from or to the microprocessor. The Intel 8085 requires a 16-bits. The 8 most significant bits of the address are transmitted by the address bus, (Pins A8, to A15). The 8 least significant bits of the address are transmitted by address/data bus, (Pins AD0 to AD7). The address/data bus transmits data and address at different moments. At a particular moment it transmits either data or address. Thus the AD-bus operates in time shared mode. This technique is known as multiplexing. First of all 16-bit memory address is transmitted by the microprocessor the 8 MSBs of the address on the A-bus and the 8 LSBs of the address on AD- bus. Thus the effective width of the address is latched so that the complete 16-bit address remains available for further operation. The 8-bit AD-bus now becomes free, and it is available for data transmission 216 (i.e. 64K, where 1K = 1024 bytes) memory location can be addressed directly by Intel 8085. Each memory location contains 1 byte of data. Timing and Control Signals The timing and control unit generates timing signals for the execution of instruction and control of peripheral devices. The organization of a microprocessor and types of registers differ from processor to processor. The timing used for the execution of instructions and control of peripherals are different for different microprocessors. The selection of a suitable microprocessor for a particular application is a tough task for an engineer. The knowledge of the organization and timing and control system helps an engineer in the selection of a microprocessor. The design and cost of a processor also depends on the timing structure and register organization. For the execution of an instruction a microprocessor fetches the instruction from the memory and executes it. The time taken for the execution of an instruction is called instruction cycle (IC). An instruction cycle (IC). An instruction cycle consists of a fetch cycle (FC) and an execute cycle (EC). A fetch cycle is the time required for the fetch operation in which the machine code of the instruction (opcode) is fetched from the memory. This time is a fixed slot of time. An execute cycle is of variable width which depends on the instruction to be executed. The total time for the execution is given by IC = FC + EC Fetch Operation

- 30. FOR STUDY MATERIAL OF IT SPECIALIST OFFICER CALL 08961556195 OR EMAIL tamal253@yahooo.com In fetch operation the microprocessor gets the 1st byte of the instruction, which is operation code (opcode), from the memory. The program counter keeps the track of address of the next instruction to be executed. In the beginning of the fetch cycle the content of the program counter is sent to the memory. This takes one clock cycle. The memory first reads the opcode. This operation also takes one clock cycle. Then the memory sends the opcode to the microprocessor, which takes one clock period. The total time for fetch operation is the time required for fetching an opcode from the memory. This time is called fetch cycle. Having received the address from the microprocessor the memory takes two clock cycles to respond as explained above. If the memory is slow, it may take more time. In that case the microprocessor has to wait for some time till it receives the opcode from the memory. The time for which the microprocessor waits is called wait cycle. Most of the microprocessor have provision for wait cycles to cope with slow memory. Execute Operation The opcode fetched from the memory goes to the data register, DR (data/address buffer in Intel 8085) and then to instruction register, IR. From the instruction register it goes to the decoder circuitry is within the microprocessor. After the instruction is decoded, execution begins. If the operand is in the general purpose registers, execution is immediately performed. The time taken in decoding and the address of the data, some read cycles are also necessary to receive the data from the memory. These read cycle are similar to opcode fetch cycle. The fetch quantities in these cycles are address or data. Figure 4 (a) and Figure 4 (b) shows an instruction and fetch cycle respectively.

- 31. FOR STUDY MATERIAL OF IT SPECIALIST OFFICER CALL 08961556195 OR EMAIL tamal253@yahooo.com Machine Cycle An instruction cycle consists of one or more machine cycles as shown in Figure 5. This figure is for MVI instruction. A machine cycle consists of a number of clock cycles. One clock cycle is known as state. Applications of Microprocessor Microprocessor are being used for numerous applications and the list of applications is becoming longer and longer. To give an idea of microprocessor applications few areas are given below. 1. Personal Computer 2. Numerical Control 3. Mobile Phones 4. Automobiles 5. Bending Machines 6. Medical Diagnostic Equipment 7. Automatic voice recognizing systems 8. Prosthetics 9. Traffic light Control 10. Entertainment Games 11. Digital Signal Processing 12. Communication terminals 13. Process Control 14. Calculators 15. Sophisticated Instruments 16. Telecommunication Switching Systems 17. Automatic Test Systems.