More Related Content

Similar to Điện tử số thầy Phạm Ngọc Nam. (20)

Điện tử số thầy Phạm Ngọc Nam.

- 1. ©

R.Lauwereins

Imec 2001

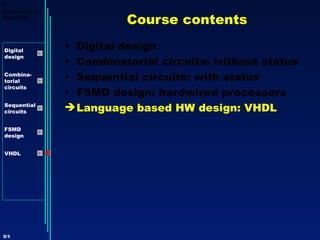

Course contents

Digital

• Digital design

design

• Combinatorial circuits: without status

Combina-

torial • Sequential circuits: with status

circuits

• FSMD design: hardwired processors

Sequential

circuits Language based HW design: VHDL

FSMD

design

VHDL

5/1

- 2. Language based HW design:

©

R.Lauwereins

Imec 2001

a VHDL primer

Digital

• Introduction

design

• A first look at VHDL

Combina-

torial • Signals and data types

circuits

• VHDL operators

Sequential

circuits • Concurrent versus sequential

statements

FSMD

design • Sequential construction statements

VHDL • Higher performance, less portability:

e.g. synthesis issues for Xilinx

5/2

- 3. Language based HW design:

©

R.Lauwereins

Imec 2001

a VHDL primer

Digital

Introduction

design

• A first look at VHDL

Combina-

torial • Signals and data types

circuits

• VHDL operators

Sequential

circuits • Concurrent versus sequential

statements

FSMD

design • Sequential construction statements

VHDL • Higher performance, less portability:

e.g. synthesis issues for Xilinx

5/3

- 4. ©

R.Lauwereins

Imec 2001

VHDL primer: Introduction

Digital

• Acronym:

design

VHDL = VHSIC Hardware Description Language

Combina- VHSIC = Very High Speed Integrated Circuit

torial

circuits • What is VHDL?

A programming language for describing the behavior

Sequential

circuits of digital systems

Design entry language, used for

FSMD

design Unambiguous specification at behavioral and RTL

level

VHDL Simulation (executable specification…)

Synthesis

Documentation

• Standardisation: IEEE 1076

First version: 1986

Second version: 1993

New version about to appear

5/4

- 5. ©

R.Lauwereins

Imec 2001

VHDL primer: Introduction

Digital

• When to use VHDL instead of

design

schematics?

Combina- Drawbacks:

torial

circuits VHDL is easy to learn but hard to master

(semantics are quite different from software

Sequential languages)

circuits

VHDL has a difficult syntax (Language sensitive

FSMD

editors with templates for all language

design constructs)

VHDL is very ‘wordy’: lots of code to type for just

VHDL

a few simple things

A list of instructions is less intuitive to

understand than a block diagram for a human

being

VHDL is designed to make simulation efficient:

contains aspects that have hardly anything to do

with hardware behavior, but is useful to speed-up

event driven simulation

5/5

- 6. ©

R.Lauwereins

Imec 2001

VHDL primer: Introduction

Digital

• When to use VHDL instead of

design

schematics?

Combina- Easier to capture complex circuits: higher level

torial

circuits

of abstraction with automated synthesis

you specify ‘add’ instead of jotting

Sequential

circuits down a specific type of adder: the

FSMD

synthesis tool will instantiate the

design best type of adder under timing, area

VHDL

& power constraints

easy to parametrise (e.g. word

length, queue depth)

easy to specify arrays of

components

Portable across many tools for simulation,

synthesis, analysis, verification, … of different

5/6

- 7. ©

R.Lauwereins

Imec 2001

VHDL primer: Introduction

Digital

• Limitations of VHDL

design

The standard only describes syntax and

Combina-

semantics, but not the coding style

torial you can specify the same behavior (e.g. MUX) in

circuits

an almost unlimited number of ways

Sequential each leading to a completely different

circuits implementation (e.g. Multiplexor or tri-state bus)

which is synthesis tool dependent.

FSMD

design You should do lots of experimentation with style-

tool combinations to be able to predict how the

VHDL

hardware will look like that will be synthesised.

Is prediction necessary? You also do not predict

the ASM generated by C; C is less efficient than

ASM but faster to write. Currently, it is hard to

tolerate the inefficiency caused by the higher

level specification for hardware.

Note: for DSP processors programmed in C, we do

predict ASM and have to experiment with style-

5/7 compiler combinations for efficiency reasons!!

- 8. ©

R.Lauwereins

Imec 2001

VHDL primer: Introduction

Digital

• Limitations of VHDL (ctud)

design

Only a subset of VHDL can be automatically

Combina-

synthesised; each vendor supports a different

torial subset

circuits

Only digital; special extension (not yet widely

Sequential adopted) for analog: VHDL-AMS (acronym for

circuits

VHDL Analog and Mixed Signal)

FSMD

design

IEEE standard 1076.1-1999

is a super-set of the full IEEE VHDL

VHDL

1076-1993 standard for digital design

5/8

- 9. ©

R.Lauwereins

Imec 2001

VHDL primer: Introduction

Digital

• Abstraction levels

design

Behavioral

Combina- Interconnected functions

torial

circuits

Only info on functions or algorithms

Sequential (what)

circuits

Only timing needed to let the

FSMD

design

function work correctly

OK for VHDL

VHDL

Behavioral synthesisers immature;

used for high level executable

specification in top-down design and

manual synthesis into RTL

5/9

- 10. ©

R.Lauwereins

Imec 2001

VHDL primer: Introduction

Digital

• Abstraction levels

design

RTL

Combina- Interconnected registers and combinatorial units

torial

circuits

Info on function (what) and architecture (how)

Cycle accurate

Sequential No technology dependent timing info

circuits

OK for VHDL

FSMD Good synthesisers

design

Gate level

VHDL Interconnected gates and flip-flops

Info on function and architecture

Info on technology dependent timing (gate

delays)

Layout

Info on layout on silicon

Continuous timing

5/10 Analog effects

- 11. ©

R.Lauwereins

Imec 2001

VHDL primer: Introduction

Digital

• Other hardware description languages

design

(HDL)

Combina- Verilog

torial

circuits More widespread in USA than in

Sequential

Europe

circuits

Often required for gate level or RTL

FSMD level ASIC sign-off

design

Never ending discussion which is

VHDL

better

PLD languages like ABEL, PALASM, …

These are more at the gate level,

capturing also technology dependent

features (e.g. detailed timing)

5/11

- 12. ©

R.Lauwereins

Imec 2001

VHDL primer: Introduction

Digital

• Difference between HDLs and traditional

design

software programming languages

Combina- Concurrency: all hardware components operate

torial

circuits

in parallel

Data types: support is needed for arbitrary size

Sequential

circuits

integers, bit vectors, fixed point numbers

Concept of time

FSMD

design

VHDL

5/12

- 13. Language based HW design:

©

R.Lauwereins

Imec 2001

a VHDL primer

Digital

• Introduction

design

A first look at VHDL

Combina-

torial • Signals and data types

circuits

• VHDL operators

Sequential

circuits • Concurrent versus sequential

statements

FSMD

design • Sequential construction statements

VHDL • Higher performance, less portability:

e.g. synthesis issues for Xilinx

5/13

- 14. A First look at VHDL:

©

R.Lauwereins

Imec 2001

Example 1 task description

Digital

• Design a circuit named ‘Test’ with 3 8-bit

design

inputs (In1, In2, In3) and two boolean

Combina- outputs (Out1, Out2). The first output

torial

circuits equals ‘1’ when the first and second input

are equal; the second output equals ‘1’

Sequential

circuits when the first and third input are equal.

FSMD • Let’s first make a schematic design:

design

VHDL

5/14

- 15. A First look at VHDL:

©

R.Lauwereins

Imec 2001

Schematic specification

Digital

• The circuit will be hierarchically

design

decomposed into a top level component

Combina- ‘Test’ containing 2 instantiations of a

torial

circuits comparator component ‘Compare’

Sequential

circuits Test

Compare

FSMD

In1 Out1

design A

EQ

VHDL

B

In2

Compare

A

In3 EQ Out2

B

5/15

- 16. A First look at VHDL:

©

R.Lauwereins

Imec 2001

Schematic specification

Digital

• The comparator is then hierarchically

design

decomposed into a gate level

Combina- combinatorial circuit

torial

circuits

Compare

Sequential

circuits A[0] XNOR

A

FSMD B[0]

design

A[1] AND

VHDL EQ

B[1] EQ

B

A[7]

B[7]

5/16

- 17. A First look at VHDL:

©

R.Lauwereins

Imec 2001

Entity and Architecture

Digital

• Declaration of the ‘Compare’ design

design

entity: ‘Entity’ specifies

Combina-

the interface

torial -- Eight bit comparator to the circuit, the

circuits -- black box of a

entity Compare is schematic

Sequential port( A,B: in bit_vector(0 to 7);

circuits EQ: out bit); Input and output

end entity Compare; signals are called

FSMD ‘ports’

design

architecture Behav1 of Compare is

begin ‘Architecture’ describes

VHDL EQ <= ‘1’ when (A=B) else ‘0’; the behavior and structure

end architecture Behav1; of the entity,

Notes: the internals of the box

- Multiple architectures per entity are possible: different ways

of implementing same behavior

- This architecture specifies behavior at RTL level and not

the actual structure of gates; synthesis tool will automatically

translate this RTL behavioral description into gate level

5/17 - Ports have an explicit direction and are (vectors of) bits

- 18. A First look at VHDL:

©

R.Lauwereins

Imec 2001

Component and Instantiation

Digital

• Specification of the next higher level in

design

the circuit hierarchy: ‘Test’

Virtual device: allows

-- Dual comparator Test component

Combina- for concurrent

torial --

development of both

circuits entity Test is

hierarchical levels,

port( In1,In2,In3: in bit_vector(0 to 7);

by different persons.

Sequential Out1,Out2: out bit);

‘Comparator’ will be

circuits end entity Test;

bound to ‘Compare’

later

FSMD architecture Struct1 of Test is

design component Comparator is

port( X,Y: in bit_vector(0 to 7); Two instantiations

VHDL Z: out bit); of the same component

end component Comparator; ‘Comparator’ with its

begin signal binding

Compare1: component Comparator port map (In1,In2,Out1);

Compare2: component Comparator port map (In1,In3,Out2);

end architecture Struct1;

Notes:

- The two ‘comparator’ components work concurrently!!!

- This architecture describes structure, i.e. how this entity

5/18 consists of an interconnection of lower level components

- 19. A First look at VHDL:

©

R.Lauwereins

Imec 2001

Comparison with C

Digital

• This is very similar to software

design

programming languages, e.g. C

Combina-

torial /* Eight bit comparator

circuits

*/ Interface to the function

int Compare

Sequential (int A, int B)

circuits

Inputs and outputs are

called ‘arguments’

{

FSMD

design

return (A == B); Behavior of the function

}

VHDL

Notes:

- Only one behavior per function possible

- Behavior is specified at rather high level and will be

automatically translated by the compiler into ASM instructions

- Function arguments do not have a direction and are of type int

5/19

- 20. A First look at VHDL:

©

R.Lauwereins

Imec 2001

Comparison with C

Digital

• This is how the higher hierarchical level

design

looks like in C

Combina- /* Dual comparator Test program

torial */

circuits

main()

Sequential {

circuits

Two calls to the function

int In1, In2, In3; ‘Compare’ with its

int Out1, Out2; argument binding

FSMD

design

Out1 = Compare(In1, In2);

VHDL

Out2 = Compare(In1, In3);

}

Notes:

- The two ‘compare’ function calls are executed sequentially

- This main program is executed once and stops. In VHDL, all

components describe relations that are valid continuously and

forever

5/20

- 21. A First look at VHDL:

©

R.Lauwereins

Imec 2001

Configuration

Digital

• When an entity has multiple

design

architectures, how do you indicate which

Combina- one to use?

torial

circuits • How do you bind ‘Components’ to

Sequential

‘Entities’?

circuits -- Configuration information: architecture selection

-- and component-entity binding

FSMD

Both ‘use entity’s could

design be combined in one:

configuration Build1 of Test is

for All: Comparator ...

for Struct1

VHDL

for Compare1: Comparator use entity Compare(Behav1)

port map (A => X, B => Y, EQ => Z);

end for;

for others: Comparator use entity Compare(Behav1)

port map (A => X, B => Y, EQ => Z);

end for;

end for;

end configuration Build1;

5/21

Note: ‘configuration’ corresponds in SW to ‘linking’

- 22. A First look at VHDL:

©

R.Lauwereins

Imec 2001

Syntax

Digital

design

ENTITY:

Combina-

torial entity Entity_name is

circuits

port( Signal_name: in Signal_type;

Signal_name: out Signal_type);

Sequential

circuits

end entity Entity_name;

FSMD

design

ARCHITECTURE:

VHDL

architecture Architecture_name of Entity_name is

local_signal_declarations;

component_declarations;

begin

statements;

end architecture Architecture_name;

5/22

- 23. A First look at VHDL:

©

R.Lauwereins

Imec 2001

Syntax

Digital COMPONENT:

design component Component_name is

port( Signal_name: in Signal_type;

Combina- Signal_name: out Signal_type);

torial end component Component_name;

circuits

Sequential COMPONENT INSTANTIATION:

circuits -- component instantiation

Instance_name: component Component_name

FSMD port map (Signal_list);

design or

-- direct instantiation

VHDL Instance_name: entity Entity_name(Architecture_name)

port map (Signal_list);

Name used in

SIGNAL LIST: component declaration

-- two variants:

-- variant 1: ordered list of signals as in software languages

-- e.g. (In1,In2,Out1)

-- variant 2: named list Locally used name

-- e.g. (B => In2, EQ => Out1, A => In1)

5/23

- 24. A First look at VHDL:

©

R.Lauwereins

Imec 2001

Syntax

Digital

design CONFIGURATION:

Combina- configuration Config_name of Entity_name is

torial for Architecture_name

circuits

for Instance_name: Component_name use entity

Entity_name(Architecture_name)

Sequential

circuits

port map (Signal_list);

end for;

end for;

FSMD

design end configuration Config_name;

VHDL

5/24

- 25. A First look at VHDL:

©

R.Lauwereins

Imec 2001

Example 2

Digital • Declare a 3-input AND gate

design

Combina- A

Y

torial B

circuits

C

Sequential

circuits

-- 3-input AND gate

entity AND3 is

FSMD

design port ( A,B,C: in bit;

Y: out bit);

VHDL end entity AND3;

architecture RTL of AND3 is

begin

Y <= ‘1’ when ((A=‘1’) and (B=‘1’) and (C=‘1’)) else ‘0’;

end architecture RTL;

5/25

- 26. A First look at VHDL:

©

R.Lauwereins

Imec 2001

Example 2

Digital • Declare a 3-input OR gate

design

Combina- A

Y

torial B

circuits

C

Sequential

circuits

-- 3-input OR gate

entity OR3 is

FSMD

design port ( A,B,C: in bit;

Y: out bit);

VHDL end entity OR3;

architecture RTL of OR3 is

begin

Y <= ‘0’ when ((A=‘0’) and (B=‘0’) and (C=‘0’)) else ‘1’;

end architecture RTL;

5/26

- 27. A First look at VHDL:

©

R.Lauwereins

Imec 2001

Example 2

Digital • Declare an INV gate

design

Combina-

torial A Y

circuits

Sequential

circuits

-- INV gate

entity INV is

FSMD

design port ( A: in bit;

Y: out bit);

VHDL end entity INV;

architecture RTL of INV is

begin

Y <= ‘1’ when (A=‘0’) else ‘0’;

end architecture RTL;

5/27

- 28. A First look at VHDL:

©

R.Lauwereins

Imec 2001

Example 3

Digital

• Build a 2-to-1 MUX using both a

design

behavioral as well as a structural

Combina- description

torial A

circuits Y

B

Sequential

circuits S

entity MUX21 is The black box

port ( A,B,S: in bit; interface

FSMD

design Y: out bit);

end entity MUX21;

VHDL

architecture Behav of MUX21 is

begin Behavioral description

Y <= A when (S=‘1’) else B;

end architecture Behav;

5/28

- 29. A First look at VHDL:

©

R.Lauwereins

Imec 2001

Example 3

Digital

• Build a 2-to-1 MUX using both a behav. as

design

well as a structural description A

Y

Combina- architecture Struct of MUX21 is B

torial signal U,V,W : bit;

circuits component AND2 is S

port ( X,Y: in bit;

Sequential Z: out bit); Structural description

circuits

end component AND2;

component OR2 is A

FSMD

port ( X,Y: in bit; W

design

Z: out bit);

S Y

end component OR2;

VHDL

component INV is U V

port ( X: in bit;

Z: out bit); B

end component INV;

begin

Gate1: component INV port map (X=>S,Z=>U);

Gate2: component AND2 port map (X=>A,Y=>S,Z=>W);

Gate3: component AND2 port map (X=>U,Y=>B,Z=>V);

Gate4: component OR2 port map (X=>W,Y=>V,Z=>Y);

5/29 end architecture Struct;

- 30. A First look at VHDL:

©

R.Lauwereins

Imec 2001

Example 3

Digital

• Assume that we want to use the

design

previously declared AND3, OR3 and INV

Combina- for this structural description of MUX

torial

circuits

configuration Use3InputGates of MUX21 is

Sequential for Behav Entities

circuits A

end for; Y

for Struct B

FSMD for Gate1:INV use entity INV(RTL) C

design

port map (A=>X,Y=>Z);

end for; A Y

VHDL

for All:AND2 use entity AND3(RTL)

port map (A=>X,B=>Y,C=>’1’,Y=>Z);

end for;

for Gate4:OR2 use entity OR3(RTL) Components

port map (A=>X,B=>Y,C=>’0’,Y=>Z);

X

end for; Z

end for;

Y

end configuration Use3InputGates;

X Z

5/30

- 31. A First look at VHDL:

©

R.Lauwereins

Imec 2001

Test bench

Digital

• How can we verify the circuit that we

design

made?

Combina- We have to apply representative stimuli

torial

circuits to the circuit

and check whether the outputs are correct

Sequential

circuits

• A VHDL ‘test bench’ can be considered to

FSMD be the top level of a design

design

It instantiates the Design Under Test (DUT)

VHDL applies stimuli to it

checks whether the stimuli are correct

or

captures the outputs for visualisation in a

waveform viewer

5/31

- 32. A First look at VHDL:

©

R.Lauwereins

Imec 2001

Test bench

Digital • Create a test bench for the behavioral

design

version of the MUX

Combina- entity Testbench is Testbench is A

torial

circuits end entity Testbench; self-contained: Y

B MUX21

no ports

Sequential

circuits S

FSMD architecture BehavTest of Testbench is

design Signal In1,In2,Select,Out : bit;

begin

VHDL DUT: entity MUX21(Behav) port map (In1, In2, Select, Out);

Stimulus: process is

begin

In1<=‘0’;In2<=‘1’;Select<=‘0’; wait for 20 ns;

Select<=‘1’; wait for 20 ns;

In1<=‘1’;In2<=‘0’; wait for 20 ns;

...

end process Stimulus;

end architecture BehavTest;

5/32

- 33. A First look at VHDL:

©

R.Lauwereins

Imec 2001

Re-use

Digital

• Often, parts of a design can be re-used in

design

another design

Combina-

torial

• New products in industry often contain

circuits 95% of re-used parts and 5% is newly

Sequential

designed: evolutionary design

• VHDL encourages this by the concept of

circuits

FSMD ‘Packages’

design

• A ‘Package’ contains definitions of

VHDL

constant values, component declarations,

user data types, and sub-programs of

VHDL code

• But first the concept ‘Library’: a library is

name of directory into which the binary

code resulting from analysis/compilation

5/33 is stored. Default: WORK

- 34. A First look at VHDL:

©

R.Lauwereins

Imec 2001

Re-use

Digital

Package interface declaration:

design

package Package_name is

Combina- -- constants

torial -- user defined types

circuits -- component declarations

-- sub programs

Sequential end package Package_name;

circuits

FSMD

design

VHDL

How to use a package?

use Library_name.Package_name.all;

…

U1: entity Package_name.Entity_name(Architecture_name);

5/34

- 35. Language based HW design:

©

R.Lauwereins

Imec 2001

a VHDL primer

Digital

• Introduction

design

• A first look at VHDL

Combina-

torial

Signals and data types

circuits

• VHDL operators

Sequential

circuits • Concurrent versus sequential

statements

FSMD

design • Sequential construction statements

VHDL • Higher performance, less portability:

e.g. synthesis issues for Xilinx

5/35

- 36. Signals and Data Types:

©

R.Lauwereins

Imec 2001

Predefined signal types

Digital package Standard is

design type Bit is (‘0’,’1’);

type Boolean is (False, True);

Combina- type Character is (--ASCII set);

torial

type Integer is range implementation_defined;

circuits

type Real is range implementation_defined;

type Bit_vector is (--array of bits);

Sequential

circuits type String is (--array of characters);

type Time is range implementation_defined;

FSMD

end package Standard;

design

Bit, Boolean and Character are enumeration types

VHDL

All standard types are ‘unresolved’ (see later for the meaning

of this)

5/36

- 37. Signals and Data Types:

©

R.Lauwereins

Imec 2001

Predefined signal types

Digital

design Examples of integer declarations:

type Year is range 0 to 99;

Combina- type Memory_address is range 65535 downto 0;

torial

circuits

Checked by simulator

Examples of real declarations:

Sequential

circuits type Probability is range 0.0 to 1.0;

type Input_level is range -5.0 to 5.0;

FSMD

design

A Bit_vector is a collection of bits; a value is specified between

VHDL double quotes:

constant State1: bit_vector(4 downto 0) := “00100”;

MSB, bit 4 LSB

A String is a collection of characters; a value is specified

between double quotes:

constant Error_message: string

:= “Unknown error: ask your poor sysop for help”;

5/37

- 38. Signals and Data Types:

©

R.Lauwereins

Imec 2001

Predefined signal types

Digital

design Time is a physical type:

type Time is range implementation_defined

Combina- units

torial fs; Primary unit:

circuits ps = 1000 fs; resolution limit

ns = 1000 ps;

Sequential us = 1000 ns;

circuits

ms = 1000 us; Secondary units

sec = 1000 ms;

FSMD min = 60 sec;

design

hr = 60 min;

end units;

VHDL

Examples of use:

wait for 20 ns;

constant Sample_period: time := 2 ms;

constant Clock_period: time := 50 ns;

5/38

- 39. Signals and Data Types:

©

R.Lauwereins

Imec 2001

User defined physical types

Digital

design The user may define his/her own physical types:

type Length is range 0 to 1E9

Combina- units Primary unit:

torial um; resolution limit

circuits mm = 1000 um;

m = 1000 mm;

Metric secondary units

Sequential km = 1000 m;

circuits

mil = 254 um;

inch = 1000 mil;

FSMD foot = 12 inch;

design Imperial secondary units

yard = 3 foot;

end units;

VHDL

5/39

- 40. Signals and Data Types:

©

R.Lauwereins

Imec 2001

User defined enumeration types

Digital

design The user may define his/her own enumeration types:

type FSM_states is (reset, wait, input, calculate, output);

Combina-

torial

circuits

Not all synthesis tools support enumerated types

Sequential

circuits When they do support them, the default encoding is often

straightforward encoding using the minimum number of bits

FSMD

design

Often, the default encoding may be over-written by somewhere

specifying something like “encoding_style is gray_code” or by

VHDL

explicitly specifying the encoding for each possible value:

constant reset: bit_vector := “10000”;

constant wait: bit_vector := “01000”;

constant input: bit_vector := “00100”;

constant calculate: bit_vector := “00010”;

constant output: bit_vector := “00001”;

5/40

- 41. Signals and Data Types:

©

R.Lauwereins

Imec 2001

Array types

Digital

design

The user may define arrays of types:

type 1D_array is array (1 to 10) of integer;

Combina- type 2D_array is array (5 downto 0, 1 to 10) of real;

torial

circuits

Keep in mind that a vector of bits has NO numerical meaning

Sequential

circuits

and that hence arithmetic operations on vectors of bits make

no sense:

FSMD

design signal Bus,Address : bit_vector (0 to 3);

VHDL Bus <= Address + 1; -- This makes no sense!!!

Solution: via operator overloading (cf. C++):

- two functions ‘+’ will exist, one working on integers and

one working on vectors of bits

- the latter is defined in a vendor specific ‘vector

arithmetic package’ that should be use’d at the beginning

of your VHDL

5/41

- 42. Signals and Data Types:

©

R.Lauwereins

Imec 2001

Standard logic

Digital

• We have seen that we need more logic

design

levels than just ‘0’ and ‘1’ (e.g. don’t care,

Combina- unknown after setup violation, …)

torial

circuits • Therefore the IEEE defined in standard

Sequential

number 1164 9-valued logic signals and

circuits

operations on them: use always those

FSMD instead of ‘bit’!!

design

• Exists in unresolved form (std_ulogic) and

VHDL resolved form (std_logic) -- again: see

later for meaning

• Exists in single bit and array form:

constant A: std_ulogic := ‘U’; -- unitialized

constant B: std_logic := ‘U’;

constant C: std_ulogic_vector (0 to 15);

5/42 constant D: std_logic_vector (15 downto 0);

- 43. Signals and Data Types:

©

R.Lauwereins

Imec 2001

Standard logic

Digital

design library IEEE;

use IEEE.Std_logic_1164.All;

Combina-

torial type std_logic is (

circuits

‘U’, -- uninitialized e.g. after power-up

‘X’, -- strongly driven unknown e.g. after setup violation

Sequential

circuits ‘0’, -- strongly driven logic zero

‘1’, -- strongly driven logic one

FSMD

‘Z’, -- high impedance e.g. not driven at all

design ‘W’, -- weakly driven unknown

‘L’, -- weakly driven logic zero

VHDL ‘H’, -- weakly driven logic one

‘-’); -- don’t care

5/43

- 44. Signals and Data Types:

©

R.Lauwereins

Imec 2001

Assignment to signals

Digital Is the following code valid?

design

signal Z,A,B: std_ulogic;

Combina-

torial Z <= A;

circuits

Z <= B;

Sequential

circuits No, because:

- all statements are concurrently valid and are not executed

FSMD sequentially as in SW languages

design

- when A=‘0’ and B=‘1’, we have a short circuit

VHDL

A A Resolver

circuit

R

Z Z

B B

5/44

- 45. Signals and Data Types:

©

R.Lauwereins

Imec 2001

Assignment to signals

Digital

• VHDL is a single assignment language for

design

unresolved data types

Combina-

torial

• For resolved data types (std_logic &

circuits std_logic_vector), the resolver circuit is

Sequential

inferred by the synthesis tool

circuits

FSMD

design

A Resolver

signal Z,A,B: std_logic; circuit

VHDL

Z <= A;

R

Z <= B;

B Z

5/45

- 46. Signals and Data Types:

©

R.Lauwereins

Imec 2001

Assignment to signals

Digital • When an array is assigned to another

design

array, both arrays must have same size

Combina-

torial

• Assignment is by position, not by index!!!

circuits

signal Down: std_logic_vector (3 downto 0);

Sequential signal Up: std_logic_vector (0 to 3);

circuits

Up <= Down;

FSMD

design

Which of the two following interpretations is correct?

VHDL

Up(0) Down(3) Up(0) Down(0)

Up(1) Down(2) Up(1) Down(1)

OR

Up(2) Down(1) Up(2) Down(2)

Up(3) Down(0) Up(3) Down(3)

5/46 Correspondence by position!

- 47. Signals and Data Types:

©

R.Lauwereins

Imec 2001

Assignment to signals

Digital

• Assignment to a part of an array is

design

possible

Combina-

torial

• Make sure that the direction (to or

circuits downto) is the same as in the declaration

Sequential signal Bus: std_logic_vector (7 downto 0);

circuits

signal A: std_logic_vector (0 to 3);

FSMD Which of the following VHDL codes is correct?

design

Bus(0 to 3) <= A; Direction of Bus differs from declaration

VHDL

Bus <= A; Array sizes do not match

Bus(3 downto 0) <= A; OK! Bus(3) is driven by A(0)

Bus(5 downto 4) <= A(0 to 1); OK! Bus(5) is driven by A(0)

Bus(5 downto 4) <= A(0 to 1); OK! Bus(4) is driven by A(1)

Bus(4 downto 3) <= A(2 to 3); and by A(2): resolved data

5/47 type… use with care!!

- 48. Signals and Data Types:

©

R.Lauwereins

Imec 2001

Assignment to signals

Digital • ‘Concatenation’: bring wire bundles

design

together to assign them to a bigger array

Combina- signal Byte_bus: std_logic_vector(7 downto 0);

torial

circuits

signal Nibble_busA, Nibble_busB: std_logic_vector(3 downto 0);

Byte_bus <= Nibble_busA & Nibble_busB;

Sequential

circuits

Nibble_busA(3)

FSMD Nibble_busA(2)

design Byte_bus(7) Nibble_busA(1)

Byte_bus(6) Nibble_busA(0)

VHDL Byte_bus(5)

Byte_bus(4)

Byte_bus(3)

Byte_bus(2)

Byte_bus(1) Nibble_busB(3)

Byte_bus(0) Nibble_busB(2)

Nibble_busB(1)

Nibble_busB(0)

5/48

- 49. Signals and Data Types:

©

R.Lauwereins

Imec 2001

Assignment to signals

Digital

• ‘Aggregation’: alternative method to

design

assign multiple small arrays to a bigger

Combina- array

torial

circuits • Not supported by all synthesis tools!!

Sequential

circuits signal X,Y,Z,T: std_logic_vector(3 downto 0);

signal A,B,C: std_logic;

FSMD

design X <= (A,B,C,C); -- correspondence by position

VHDL Y <= (3 => A, 1 downto 0 => C, 2 => B);

Z <= (3 => A, 2 => B, others => C);

T <= (others => ‘0’); -- initialization irrespective of width of T

5/49

- 50. Signals and Data Types:

©

R.Lauwereins

Imec 2001

Generic constants

Digital • Allows to parameterize behavior

design

• Enables re-use of entities in slightly

Combina-

torial

changing environments

circuits

• Makes VHDL much more powerful than

Sequential schematic entry

circuits

• Generic constants need to have a value at

FSMD

design

synthesis time!

entity General_mux is

VHDL

generic (width : integer);

port ( Input : in std_logic_vector (width - 1 downto 0);

Select : in integer range 0 to width - 1;

Output : out std_logic);

end entity General_mux;

5/50

- 51. ©

R.Lauwereins

Imec 2001

Generic constants

entity General_mux is

generic (width : integer);

port ( Input : in std_logic_vector (width - 1 downto 0);

Digital Select : in integer range 0 to width - 1;

design Output : out std_logic);

end entity General_mux; This is not valid VHDL:

Combina-

index is not known at

torial architecture Behav of General_mux is design time! We will

circuits

begin replace this by valid

Output <= Input(Select); code later!

Sequential

circuits

end architecture Behav;

entity Testbench is

FSMD

design

end entity Testbench;

architecture Build1 of Testbench is

VHDL

constant Input_size : integer := 8;

signal A : std_logic_vector (Input_size-1 downto 0);

signal S : integer range 0 to Input_size - 1;

signal B : std_logic;

begin

DUT: entity General_mux(Behav)

generic map (width => Input_size)

port map (Input => A, Select => S, Output => B);

...

5/51 end architecture Build1;

- 52. Language based HW design:

©

R.Lauwereins

Imec 2001

a VHDL primer

Digital

• Introduction

design

• A first look at VHDL

Combina-

torial • Signals and data types

circuits

VHDL operators

Sequential

circuits • Concurrent versus sequential

statements

FSMD

design • Sequential construction statements

VHDL • Higher performance, less portability:

e.g. synthesis issues for Xilinx

5/52

- 53. ©

R.Lauwereins

Imec 2001

Logical Operators

Digital

• List of logical operators: not, and, or, xor,

design

nand, nor

Combina-

torial

• Precedence:

circuits ‘not’ has highest precedence

Sequential

all others have equal precedence, lower than

circuits ‘not’

FSMD • Logical operators are predefined for

design

following data types: bit, bit_vector,

VHDL boolean, std_logic, std_logic_vector,

std_ulogic, std_ulogic_vector

• A logical operator may work on an array:

arrays should have same size

elements are matched by position

5/53

- 54. ©

R.Lauwereins

Imec 2001

Logical Operators

Digital

design

library IEEE;

Combina- use IEEE.Std_Logic_1164.All;

torial

circuits

entity Gate is

Sequential

port( A,B,C: in std_logic;

circuits Z: out std_logic);

end entity Gate;

FSMD

design architecture Logical of Gate is

begin

VHDL Z <= A and not(B or C);

end architecture Logical;

5/54

- 55. ©

R.Lauwereins

Imec 2001

Logical Operators

Digital

design

library IEEE;

Combina- use IEEE.Std_Logic_1164.All;

torial

circuits entity Gate is

generic(width : integer range 0 to 31);

Sequential port( A,B,C: in std_logic_vector(width-1 downto 0);

circuits

Z: out std_logic_vector(width-1 downto 0));

end entity Gate;

FSMD

design

architecture Logical of Gate is

begin

VHDL

Z <= A and not(B or C);

end architecture Logical;

5/55

- 56. ©

R.Lauwereins

Imec 2001

Relational Operators

Digital

• List of relational operators: <, <=, =>, >, =,

design

/=

Combina-

torial

• Relational operators return a boolean

circuits

• Both operands need to be of the same

Sequential type

circuits

• A relational operator may work on an

FSMD

design

array:

arrays may have different size!!

VHDL

They are left alligned and the number of bits

equal to the smallest array are compared; the

comparison is done bit by bit, from left to right

Remember: vectors of bits do not have a

numerical meaning!! However, this comparison

works on vectors of bits with the meaning of

an unsigned integer when both vectors have

5/56 equal length

- 57. Relational Operators

©

R.Lauwereins

Imec 2001

library IEEE

use IEEE.Std_Logic_1164.All;

Digital

What is the

design entity Compare is value of Z?

port( A: in std_logic_vector(3 downto 0);

B: in std_logic_vector(0 to 4); TRUE?

Combina-

torial Z: out boolean); FALSE?

circuits end entity Compare;

Sequential architecture Relational of Compare is 1110

circuits

begin is compared to

Z <= TRUE when A<B else FALSE; 1011

FSMD

design

end architecture Relational; by bit position

from left to

entity Testbench right;

VHDL

end entity Testbench; in the 2nd

position

architecture Build1 of Testbench is A(2) > B(1)

signal A: std_logic_vector(3 downto 0) := “1110”; hence (A<B)

signal B: std_logic_vector(0 to 4) := “10111”; is FALSE

signal Z: boolean;

begin

DUT: entity Compare(Relational)

port map (A => A, B => B, Z => Z);

5/57 end architecture Build1;

- 58. ©

R.Lauwereins

Imec 2001

Arithmetic Operators

Digital

• List of arithmetic operators: +, -, *, /, **

design

(exponential), abs (absolute value), mod

Combina- (modulus), rem (remainder)

torial

circuits • They are defined on types integer and

Sequential

real (except mod and rem) and not on

circuits

vectors of bits; use overloading package

FSMD for the latter (vendor dependent)

design

• Both operands have to be of same type;

VHDL different ranges are allowed

• A variable of physical type (e.g. time) may

be multiplied by an integer or real and will

still return a variable of the physical type

5/58

- 59. ©

R.Lauwereins

Imec 2001

Arithmetic Operators

Digital entity Add is

design port ( A,B: in integer range 0 to 7;

Z: out integer range 0 to 14);

Combina- end entity Add;

torial

circuits

architecture Behav of Add is

begin

Sequential

circuits Z <= A + B;

end architecture Behav;

FSMD

design

VHDL

5/59

- 60. Language based HW design:

©

R.Lauwereins

Imec 2001

a VHDL primer

Digital

• Introduction

design

• A first look at VHDL

Combina-

torial • Signals and data types

circuits

• VHDL operators

Sequential

circuits Concurrent versus sequential

statements

FSMD

design • Sequential construction statements

VHDL • Higher performance, less portability:

e.g. synthesis issues for Xilinx

5/60

- 61. ©

R.Lauwereins

Imec 2001

Concurrent Statements

Digital

• All statements are concurrent and are

design

continuously valid: this mimics the

Combina- behavior of hardware, where all gates

torial

circuits operate concurrently

Sequential

circuits entity Concurrent is

port ( A,B,C,D: in std_logic; Schematic:

FSMD Y,Z: out std_logic);

design

end entity Concurrent;

A

VHDL

architecture Struct of Concurrent is Y

B

begin

NAND1: entity NAND2 port map (A,B,Y); C

Z

NAND2: entity NAND2 port map (C,D,Z); D

end architecture Struct;

What is the difference in behavior when NAND1 is specified

after NAND2?

5/61

- 62. ©

R.Lauwereins

Imec 2001

Concurrent Statements

Digital

• All statements are concurrent and are

design

continuously valid: this mimics the

Combina- behavior of hardware, where all gates

torial

circuits operate concurrently

Sequential

circuits entity Concurrent is

port ( A,B,C,D: in std_logic; Schematic:

FSMD Y,Z: out std_logic);

design

end entity Concurrent;

A

VHDL

architecture Struct of Concurrent is Y

B

begin

NAND2: entity NAND2 port map (C,D,Z); C

Z

NAND1: entity NAND2 port map (A,B,Y); D

end architecture Struct;

Behavior is exactly the same!!!

5/62

- 63. ©

R.Lauwereins

Imec 2001

Concurrent Statements

Does this schematic specify sequential Behavior?

Digital

design

Yes Schematic:

Combina- No

torial

circuits

A

entity Concurrent is B T1

Sequential

port ( A,B, D: in std_logic;

circuits Z: out std_logic); Z

end entity Concurrent; D

FSMD

design architecture Struct of Concurrent is

signal T1: std_logic;

VHDL begin

NAND2: entity NAND2 port map (T1,D,Z);

NAND1: entity NAND2 port map (A,B,T1);

end architecture Struct;

Both gates continuously update their outputs

5/63

- 64. ©

R.Lauwereins

Imec 2001

Simulation

Digital

• This continuously updating of outputs

design

poses problems to the simulator: even if

Combina- nothing in the circuit changes, the

torial

circuits simulator has to compute continuously

the ‘new’ outputs of all gates

Sequential

circuits

• Solution: event-driven simulation

FSMD a statement is only re-evaluated when one or

design more of its input signals changes (i.e. when an

event occurs at one of its inputs)

VHDL

we say that a statement is sensitive to all its

input signals, because an event at any input

signals triggers a re-evaluation

keep in mind that this mechanism is only for

making simulation fast while maintaining the

same behavior as in reality, where all gates

work continuously!!

5/64

- 65. ©

R.Lauwereins

Imec 2001

Simulation

Digital

• How is an event-driven simulator

design

practically implemented?

Combina- 1. Put all statements with at least one changed input in the

torial

circuits ‘process execution queue’

2. Execute all statements in the process execution queue

Sequential one by one (or concurrently if the simulator is executed

circuits

on a parallel computer) without updating the output signals

FSMD 3. After all statements in the process execution queue are

design processed, update the output signals

4. Add all statements to the process execution queue that

VHDL

have an event because of the updated output signals

5. Repeat until the process execution queue is empty

6. Advance system time to the next time where a timed

event is planned (e.g. testbench: waitfor 20 ns)

Delta cycle

Delta cycle convergence

5/65

- 66. ©

R.Lauwereins

Imec 2001

Simulation

entity Flipflop is A

Q’

Digital port ( A,B: in std_logic;

design Q,Q’: out std_logic);

end entity Flipflop; Q

Combina- B

torial architecture Struct of FlipFlop is

circuits

begin

NAND2: entity NAND2 port map (Q’,B,Q);

Sequential

circuits

NAND1: entity NAND2 port map (A,Q,Q’);

end architecture Struct;

FSMD

design Process Process

Execution Execution

VHDL Queue Queue

A T1 T2

B NAND1 NAND1

NAND2

Q

Q’

Step 1: Put statements with input

T1 T2 event in PEQ

5/66

- 67. ©

R.Lauwereins

Imec 2001

Simulation

entity Flipflop is A

Q’

Digital port ( A,B: in std_logic;

design Q,Q’: out std_logic);

end entity Flipflop; Q

Combina- B

torial architecture Struct of FlipFlop is

circuits

begin

NAND2: entity NAND2 port map (Q’,B,Q);

Sequential

circuits

NAND1: entity NAND2 port map (A,Q,Q’);

end architecture Struct;

FSMD

design Process Process

Remembered Execution Execution

VHDL Outputs Queue Queue

A T1 T2

Q’ <= 1

B NAND1 NAND1

NAND2

Q

Q’

Step 2: Execute statements in PEQ

T1 T2 and remember output

5/67

- 68. ©

R.Lauwereins

Imec 2001

Simulation

entity Flipflop is A

Q’

Digital port ( A,B: in std_logic;

design Q,Q’: out std_logic);

end entity Flipflop; Q

Combina- B

torial architecture Struct of FlipFlop is

circuits

begin

NAND2: entity NAND2 port map (Q’,B,Q);

Sequential

circuits

NAND1: entity NAND2 port map (A,Q,Q’);

end architecture Struct;

FSMD

design Process Process

Remembered Execution Execution

VHDL Outputs Queue Queue

A T1 T2

Q’ <= 1

B NAND2

NAND1 NAND1

NAND2

Q

Q’

Step 3: Update outputs

T1 T2

5/68

- 69. ©

R.Lauwereins

Imec 2001

Simulation

entity Flipflop is A

Q’

Digital port ( A,B: in std_logic;

design Q,Q’: out std_logic);

end entity Flipflop; Q

Combina- B

torial architecture Struct of FlipFlop is

circuits

begin

NAND2: entity NAND2 port map (Q’,B,Q);

Sequential

circuits

NAND1: entity NAND2 port map (A,Q,Q’);

end architecture Struct;

FSMD

design Process Process

Execution Execution

VHDL Queue Queue

A T1 T2

B NAND2 NAND1

NAND2

Q

Q’

Step 4: Add statements with event

T1 T2 to PEQ

5/69 End Delta cycle 1 of T1

- 70. ©

R.Lauwereins

Imec 2001

Simulation

entity Flipflop is A

Q’

Digital port ( A,B: in std_logic;

design Q,Q’: out std_logic);

end entity Flipflop; Q

Combina- B

torial architecture Struct of FlipFlop is

circuits

begin

NAND2: entity NAND2 port map (Q’,B,Q);

Sequential

circuits

NAND1: entity NAND2 port map (A,Q,Q’);

end architecture Struct;

FSMD

design Process Process

Remembered Execution Execution

VHDL Outputs Queue Queue

A T1 T2

Q <= 0

B NAND2 NAND1

NAND2

Q

Q’

Step 2: Execute statements in PEQ

T1 T2 and remember output

5/70

- 71. ©

R.Lauwereins

Imec 2001

Simulation

entity Flipflop is A

Q’

Digital port ( A,B: in std_logic;

design Q,Q’: out std_logic);

end entity Flipflop; Q

Combina- B

torial architecture Struct of FlipFlop is

circuits

begin

NAND2: entity NAND2 port map (Q’,B,Q);

Sequential

circuits

NAND1: entity NAND2 port map (A,Q,Q’);

end architecture Struct;

FSMD

design Process Process

Remembered Execution Execution

VHDL Outputs Queue Queue

A T1 T2

Q <= 0

B NAND2 NAND1

NAND2

Q

Q’

Step 3: Update outputs

T1 T2

5/71

- 72. ©

R.Lauwereins

Imec 2001

Simulation

entity Flipflop is A

Q’

Digital port ( A,B: in std_logic;

design Q,Q’: out std_logic);

end entity Flipflop; Q

Combina- B

torial architecture Struct of FlipFlop is

circuits

begin

NAND2: entity NAND2 port map (Q’,B,Q);

Sequential

circuits

NAND1: entity NAND2 port map (A,Q,Q’);

end architecture Struct;

FSMD

design Process Process

Execution Execution

VHDL Queue Queue

A T1 T2

B NAND1 NAND1

NAND2

Q

Q’

Step 4: Add statements with event

T1 T2 to PEQ

5/72 End Delta cycle 2 of T1

- 73. ©

R.Lauwereins

Imec 2001

Simulation

entity Flipflop is A

Q’

Digital port ( A,B: in std_logic;

design Q,Q’: out std_logic);

end entity Flipflop; Q

Combina- B

torial architecture Struct of FlipFlop is

circuits

begin

NAND2: entity NAND2 port map (Q’,B,Q);

Sequential

circuits

NAND1: entity NAND2 port map (A,Q,Q’);

end architecture Struct;

FSMD

design Process Process

Remembered Execution Execution

VHDL Outputs Queue Queue

A T1 T2

Q’ <= 1

B NAND1 NAND1

NAND2

Q

Q’

Step 2: Execute statements in PEQ

T1 T2 and remember output

5/73

- 74. ©

R.Lauwereins

Imec 2001

Simulation

entity Flipflop is A

Q’

Digital port ( A,B: in std_logic;

design Q,Q’: out std_logic);

end entity Flipflop; Q

Combina- B

torial architecture Struct of FlipFlop is

circuits

begin

NAND2: entity NAND2 port map (Q’,B,Q);

Sequential

circuits

NAND1: entity NAND2 port map (A,Q,Q’);

end architecture Struct;

FSMD

design Process Process

Remembered Execution Execution

VHDL Outputs Queue Queue

A T1 T2

Q’ <= 1

B NAND1 NAND1

NAND2

Q

Q’

Step 3: Update outputs

T1 T2

5/74 Output does not change

- 75. ©

R.Lauwereins

Imec 2001

Simulation

entity Flipflop is A

Q’

Digital port ( A,B: in std_logic;

design Q,Q’: out std_logic);

end entity Flipflop; Q

Combina- B

torial architecture Struct of FlipFlop is

circuits

begin

NAND2: entity NAND2 port map (Q’,B,Q);

Sequential

circuits

NAND1: entity NAND2 port map (A,Q,Q’);

end architecture Struct;

FSMD

design Process Process

Execution Execution

VHDL Queue Queue

A T1 T2

B NAND1

NAND2

Q

Q’

Step 4: Add statements with event

T1 T2 to PEQ

5/75 End Delta cycle 3 of T1: convergence

- 76. ©

R.Lauwereins

Imec 2001

Simulation

entity Flipflop is A

Q’

Digital port ( A,B: in std_logic;

design Q,Q’: out std_logic);

end entity Flipflop; Q

Combina- B

torial architecture Struct of FlipFlop is

circuits

begin

NAND2: entity NAND2 port map (Q’,B,Q);

Sequential

circuits

NAND1: entity NAND2 port map (A,Q,Q’);

end architecture Struct;

FSMD

design Process Process

Execution Execution

VHDL Queue Queue

A T1 T2

B NAND1

NAND2

Q

Q’

Step 6: Advance system time

T1 T2

5/76

- 77. ©

R.Lauwereins

Imec 2001

Simulation

entity Flipflop is A

Q’

Digital port ( A,B: in std_logic;

design Q,Q’: out std_logic);

end entity Flipflop; Q

Combina- B

torial architecture Struct of FlipFlop is

circuits

begin

NAND2: entity NAND2 port map (Q’,B,Q);

Sequential

circuits

NAND1: entity NAND2 port map (A,Q,Q’);

end architecture Struct;

FSMD

design Process Process

Remembered Execution Execution

VHDL Outputs Queue Queue

A T1 T2

Q’ <= 1

B NAND2

NAND1

Q <= 1

NAND2

Q

Q’

Step 2: Execute statements in PEQ

T1 T2 and remember output

5/77 NAND2 computed using this Q’, not the remembered

- 78. ©

R.Lauwereins

Imec 2001

Simulation

entity Flipflop is A

Q’

Digital port ( A,B: in std_logic;

design Q,Q’: out std_logic);

end entity Flipflop; Q

Combina- B

torial architecture Struct of FlipFlop is

circuits

begin

NAND2: entity NAND2 port map (Q’,B,Q);

Sequential

circuits

NAND1: entity NAND2 port map (A,Q,Q’);

end architecture Struct;

FSMD

design Process Process

Remembered Execution Execution

VHDL Outputs Queue Queue

A T1 T2

Q’ <= 1

B NAND2

NAND1

Q <= 1

NAND2

Q

Q’

Step 3: Update outputs

T1 T2

5/78

- 79. ©

R.Lauwereins

Imec 2001

Simulation

entity Flipflop is A

Q’

Digital port ( A,B: in std_logic;

design Q,Q’: out std_logic);

end entity Flipflop; Q

Combina- B

torial architecture Struct of FlipFlop is

circuits

begin

NAND2: entity NAND2 port map (Q’,B,Q);

Sequential

circuits

NAND1: entity NAND2 port map (A,Q,Q’);

end architecture Struct;

FSMD

design Process Process

Execution Execution

VHDL Queue Queue

A T1 T2

B NAND1

Q

Q’

Step 4: Add statements with event

T1 T2 to PEQ

5/79 End Delta cycle 1 of T2

- 80. ©

R.Lauwereins

Imec 2001

Simulation

entity Flipflop is A

Q’

Digital port ( A,B: in std_logic;

design Q,Q’: out std_logic);

end entity Flipflop; Q

Combina- B

torial architecture Struct of FlipFlop is

circuits

begin

NAND2: entity NAND2 port map (Q’,B,Q);

Sequential

circuits

NAND1: entity NAND2 port map (A,Q,Q’);

end architecture Struct;

FSMD

design Process Process

Remembered Execution Execution

VHDL Outputs Queue Queue

A T1 T2

Q’ <= 0

B NAND1

Q

Q’

Step 2: Execute statements in PEQ

T1 T2 and remember output

5/80

- 81. ©

R.Lauwereins

Imec 2001

Simulation

entity Flipflop is A

Q’

Digital port ( A,B: in std_logic;

design Q,Q’: out std_logic);

end entity Flipflop; Q

Combina- B

torial architecture Struct of FlipFlop is

circuits

begin

NAND2: entity NAND2 port map (Q’,B,Q);

Sequential

circuits

NAND1: entity NAND2 port map (A,Q,Q’);

end architecture Struct;

FSMD

design Process Process

Remembered Execution Execution

VHDL Outputs Queue Queue

A T1 T2

Q’ <= 0

B NAND1

Q

Q’

Step 3: Update outputs

T1 T2

5/81

- 82. ©

R.Lauwereins

Imec 2001

Simulation

entity Flipflop is A

Q’

Digital port ( A,B: in std_logic;

design Q,Q’: out std_logic);

end entity Flipflop; Q

Combina- B

torial architecture Struct of FlipFlop is

circuits

begin

NAND2: entity NAND2 port map (Q’,B,Q);

Sequential

circuits

NAND1: entity NAND2 port map (A,Q,Q’);

end architecture Struct;

FSMD

design Process Process

Execution Execution

VHDL Queue Queue

A T1 T2

B NAND2

Q

Q’

Step 4: Add statements with event

T1 T2 to PEQ

5/82 End Delta cycle 2 of T2

- 83. ©

R.Lauwereins

Imec 2001

Simulation

entity Flipflop is A

Q’

Digital port ( A,B: in std_logic;

design Q,Q’: out std_logic);

end entity Flipflop; Q

Combina- B

torial architecture Struct of FlipFlop is

circuits

begin

NAND2: entity NAND2 port map (Q’,B,Q);

Sequential

circuits

NAND1: entity NAND2 port map (A,Q,Q’);

end architecture Struct;

FSMD

design Process Process

Remembered Execution Execution

VHDL Outputs Queue Queue

A T1 T2

Q <= 1

B NAND2

Q

Q’

Step 2: Execute statements in PEQ

T1 T2 and remember output

5/83

- 84. ©

R.Lauwereins

Imec 2001

Simulation

entity Flipflop is A

Q’

Digital port ( A,B: in std_logic;

design Q,Q’: out std_logic);

end entity Flipflop; Q

Combina- B

torial architecture Struct of FlipFlop is

circuits

begin

NAND2: entity NAND2 port map (Q’,B,Q);

Sequential

circuits

NAND1: entity NAND2 port map (A,Q,Q’);

end architecture Struct;

FSMD

design Process Process

Remembered Execution Execution

VHDL Outputs Queue Queue

A T1 T2

Q <= 1

B NAND2

Q

Q’

Step 3: Update outputs

T1 T2

5/84 Output does not change

- 85. ©

R.Lauwereins

Imec 2001

Simulation

entity Flipflop is A

Q’

Digital port ( A,B: in std_logic;

design Q,Q’: out std_logic);

end entity Flipflop; Q

Combina- B

torial architecture Struct of FlipFlop is

circuits

begin

NAND2: entity NAND2 port map (Q’,B,Q);

Sequential

circuits

NAND1: entity NAND2 port map (A,Q,Q’);

end architecture Struct;

FSMD

design Process Process

Execution Execution

VHDL Queue Queue

A T1 T2

B

Q

Q’

Step 4: Add statements with event

T1 T2 to PEQ

5/85 End Delta cycle 3 of T2: convergence

- 86. ©

R.Lauwereins

Imec 2001

Simulation

entity Flipflop is A

Q’

Digital port ( A,B: in std_logic;

design Q,Q’: out std_logic);

end entity Flipflop; Q

Combina- B

torial architecture Struct of FlipFlop is

circuits

begin

NAND2: entity NAND2 port map (Q’,B,Q);

Sequential

circuits

NAND1: entity NAND2 port map (A,Q,Q’);

end architecture Struct;

FSMD

design Process Process

Execution Execution

VHDL Queue Queue

A T1 T2

B

Q

Q’

Step 6: Advance system time

T1 T2

5/86

- 87. ©

R.Lauwereins

Imec 2001

Process

Digital

• Sometimes, the combinatorial equation in

design

a single statement becomes very

Combina- complicated:

torial A

circuits B

C

Sequential

circuits D Y

entity Complex is E

FSMD

port( A,B,C,D,E,F,G,H,I,J: F S

design

in std_logic; G

Y,Z: out std_logic);

VHDL H

end entity Complex;

I Z

architecture Struct of Complex is J

begin

Y <= ((A nand B) nand (C nand D))

when (S = ‘1’) else

((E nand F) nand (G nand H));

Z <= I nand J;

end architecture Struct;

5/87

- 88. ©

R.Lauwereins Unfortunately, in VHDL

Imec 2001

Process terminology they are

also called ‘Statements’

Digital

• Therefore a process has been defined:

design

a process acts as a single statement that is

Combina-

executed concurrently with all other

torial statements

circuits

inside a process, commands are executed

Sequential sequentially in the order they are listed. This

circuits makes it easy to break down a very

complicated statement into a list of smaller

FSMD

design

commands

to pass data from one command to the other,

VHDL we may declare temporary variables; they do

not have necessarily a physical realization

a statement, and hence also a process, is

sensitive to all its input signals; to facilitate

finding out what the input signals of a process

are, since they can occur in any command, we

have to explicitly add them to a sensitivity list.

A process is recalculated when a signal in the

5/88 sensitivity list has an event.

- 89. ©

R.Lauwereins

Imec 2001

Process

Digital

Syntax of process:

design

Process_name: process (sensitivity_list) is

Combina- -- variable declarations;

torial begin

circuits -- sequential commands

end process Process_name;

Sequential

circuits

FSMD Syntax of variable declaration:

design

variable Variable_name: type;

VHDL

Syntax of variable assignment:

Variable_name := expression;

When assigning to variable → :=

When assigning to signal → <=

5/89

- 90. ©

R.Lauwereins

Imec 2001 Process

• Rewrite the example using a process:

Digital

design entity Complex is T1 and T2 have no

port( A,B,C,D,E,F,G,H,I,J: physical meaning since

Combina- in std_logic; each refers to 2 different

torial Y,Z: out std_logic); physical wires

circuits end entity Complex;

T1 T2

Sequential architecture Struct of Complex is

circuits Sensitivity list

begin

Y_process: process (A,B,C,D,E,F,G,H,S) is

FSMD

design

variable T1,T2: std_logic;

begin A

if (S=‘1’) then B

VHDL

T1 := A nand B; C

T2 := C nand D; Y

D

else

T1 := E nand F; E

T2 := G nand H; F S

end if; G

Y <= T1 nand T2;

H

end process Y_process;

Z <= I nand J; I Z

5/90 end architecture Struct; J

- 91. ©

R.Lauwereins

Imec 2001

Process

Digital

• Processes and delta cycle convergence.

design

What is the behavior of following process:

Combina- Example: process (A,B,M) is

torial

circuits begin

Y <= A; Old M!!! M gets

M <= B; only new value

Sequential at end of process

circuits Z <= M;

end process Example;

FSMD

design 1. Assume event at B with new value B’

2. Process Example is executed once sequentially. Following

VHDL outputs are remembered: Y’ <= A; M’ <= B’; Z’ <= M;

3. Process Example suspends (i.e. is executed once completely).

Y, M and Z get their new values Y’, M’, Z’.

4. Since M is in the sensitivity list, the Example process is

placed again in the Process Execution Queue.

5. Process Example is executed: Y” <= A; M” <= B’; Z” <= M’;

6. Outputs Y, M and Z get their new values Y”, M”, Z”.

7. No signals of the sensitivity list changed => delta cycle

5/91 convergence

- 92. ©

R.Lauwereins

Imec 2001

Process

Digital

• Processes and delta cycle convergence.

design

What is the behavior of following process:

Combina-

torial Example: process (A,B,C,D) is

circuits begin

Z <= A + B;

Sequential Z <= C + D;

circuits

end process Example;

FSMD

design 1. Assume event at B with new value B’

2. The commands of Process Example are executed

VHDL sequentially. First following output is remembered:

Z’ <= A + B’;

3. Next, the second command is executed and following output

is remembered: Z’ <= C + D. This overwrites the previously

remembered Z’

4. Process Example suspends and hence signal Z is updated

with its new value C + D

When the same two statements would have occurred outside a

process, both would drive signal Z and a resolver would be

necessary

5/92

- 93. Language based HW design:

©

R.Lauwereins

Imec 2001

a VHDL primer

Digital

• Introduction

design

• A first look at VHDL

Combina-

torial • Signals and data types

circuits

• VHDL operators

Sequential

circuits • Concurrent versus sequential

statements

FSMD

design Sequential construction statements

VHDL • Higher performance, less portability:

e.g. synthesis issues for Xilinx

5/93

- 94. Sequential construction

©

R.Lauwereins

Imec 2001

statements

Digital

• Sequential construction statements are

design

only allowed within a process!!!

Combina-

torial

• There are 3 sequential construction

circuits statements: IF, CASE, FOR

Sequential IF statement:

circuits

if condition then

FSMD -- sequential statements

design multiple IF statements:

else

-- sequential statements

VHDL

end if; if condition1 then

-- sequential statements

elseif condition2 then

-- sequential statements

The first condition which elseif condition3 then

turns out to be TRUE -- sequential statements

determines which else

sequential statements are -- sequential statements

executed: built-in priority end if;

5/94