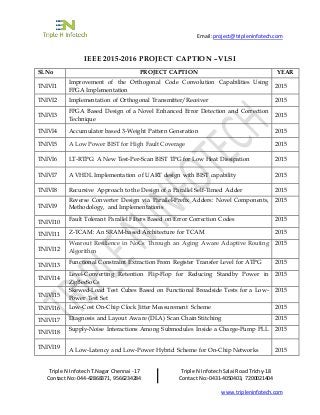

Ieee 2015 16 vlsi titles for me-mtech @triple n infotec-trichy

- 1. Email:project@tripleninfotech.com Triple N Infotech T.Nagar Chennai -17 Triple N Infotech Salai Road Trichy-18 Contact No:-044-42868371, 9566234284 Contact No:-0431-4050403, 7200021404 www.tripleninfotech.com IEEE 2015-2016 PROJECT CAPTION –VLSI Sl.No PROJECT CAPTION YEAR TNIVI1 Improvement of the Orthogonal Code Convolution Capabilities Using FPGA Implementation 2015 TNIVI2 Implementation of Orthogonal Transmitter/Receiver 2015 TNIVI3 FPGA Based Design of a Novel Enhanced Error Detection and Correction Technique 2015 TNIVI4 Accumulator based 3-Weight Pattern Generation 2015 TNIVI5 A Low Power BIST for High Fault Coverage 2015 TNIVI6 LT-RTPG: A New Test-Per-Scan BIST TPG for Low Heat Dissipation 2015 TNIVI7 A VHDL Implementation of UART design with BIST capability 2015 TNIVI8 Recursive Approach to the Design of a Parallel Self-Timed Adder 2015 TNIVI9 Reverse Converter Design via Parallel-Prefix Adders: Novel Components, Methodology, and Implementations 2015 TNIVI10 Fault Tolerant Parallel Filters Based on Error Correction Codes 2015 TNIVI11 Z-TCAM: An SRAM-based Architecture for TCAM 2015 TNIVI12 Wearout Resilience in NoCs Through an Aging Aware Adaptive Routing Algorithm 2015 TNIVI13 Functional Constraint Extraction From Register Transfer Level for ATPG 2015 TNIVI14 Level-Converting Retention Flip-Flop for Reducing Standby Power in ZigBeeSoCs 2015 TNIVI15 Skewed-Load Test Cubes Based on Functional Broadside Tests for a Low- Power Test Set 2015 TNIVI16 Low-Cost On-Chip Clock Jitter Measurement Scheme 2015 TNIVI17 Diagnosis and Layout Aware (DLA) Scan Chain Stitching 2015 TNIVI18 Supply-Noise Interactions Among Submodules Inside a Charge-Pump PLL 2015 TNIVI19 A Low-Latency and Low-Power Hybrid Scheme for On-Chip Networks 2015

- 2. Email:project@tripleninfotech.com Triple N Infotech T.Nagar Chennai -17 Triple N Infotech Salai Road Trichy-18 Contact No:-044-42868371, 9566234284 Contact No:-0431-4050403, 7200021404 www.tripleninfotech.com TNIVI20 An Inter/Intra-Chip Optical Network for Manycore Processors 2015 TNIVI21 An I/O Efficient Model Checking Algorithm for Large-Scale Systems 2015 TNIVI22 Design of Efficient Content Addressable Memories in High-Performance FinFET Technology 2015 TNIVI23 Characterization of the Proximity Effect from Tungsten TSVs on 130-nm CMOS Devices in 3-D ICs 2015 TNIVI24 Area–Delay–Power Efficient Carry-Select Adder 2015 TNIVI25 Area-Delay-Power Efficient Fixed-Point LMS Adaptive Filter With Low Adaptation-Delay 2015 TNIVI26 Constructions of Memoryless Crosstalk Avoidance Codes via C-Transform 2015 TNIVI27 Dynamic Thermal Estimation Methodology for High Performance 3-D MPSoC 2015 TNIVI28 The Impact of Aging on a Physical Unclonable Function 2015 TNIVI29 Partial Access Mode: New Method for Reducing Power Consumption of Dynamic Random Access Memory 2015 TNIVI30 VLSI Design of a Large-Number Multiplier for Fully Homomorphic Encryption 2015 TNIVI31 An Offset-Canceling Triple-Stage Sensing Circuit for Deep Submicrometer STT-RAM 2015 TNIVI32 Critical-path analysis and low-complexity implementation of the LMS Adaptive algorithm 2015 TNIVI33 A 28-nm CMOS 1 V 3.5 GS/s 6-bit DAC With Signal-Independent Delta-I Noise DfT Scheme 2015 TNIVI34 An 8 bit 0.3–0.8 V 0.2–40 MS/s 2-bit/Step SAR ADC With Successively Activated Threshold Configuring Comparators in 40 nm CMOS 2015 TNIVI35 Design of Self-Timed Reconfigurable Controllers for Parallel Synchronization via Wagging 2015 TNIVI36 Design Techniques to Improve Blocker Tolerance of Continuous-Time __ ADCs 2015 TNIVI37 Z-TCAM: An SRAM-based Architecture for TCAM 2015 TNIVI38 Quaternary Logic Lookup Table in Standard CMOS 2015 TNIVI39 A Low-Jitter Cell-Based Digitally Controlled Oscillator With Differential Multiphase Outputs 2015

- 3. Email:project@tripleninfotech.com Triple N Infotech T.Nagar Chennai -17 Triple N Infotech Salai Road Trichy-18 Contact No:-044-42868371, 9566234284 Contact No:-0431-4050403, 7200021404 www.tripleninfotech.com TNIVI40 Asynchronous Domino Logic Pipeline Design Based on Constructed Critical Data Path 2015 TNIVI41 A Low-Latency and Low-Power Hybrid Scheme for On-Chip Networks 2015 TNIVI42 A Low-Cost Low-Power All-Digital Spread-Spectrum Clock Generator 2015 TNIVI43 All Digital Energy Sensing for Minimum Energy Tracking 2015 TNIVI44 Built-in Self-Calibration and Digital-Trim Technique for 14-Bit SAR ADCs Achieving ±1 LSB INL 2015 TNIVI45 A CMOS PWM Transceiver Using Self-Referenced Edge Detection 2015 TNIVI46 Obfuscating DSP Circuits via High-Leve5 Transformations 2015 TNIVI47 Revisiting Central Limit Theorem: Accurate Gaussian Random Number Generation in VLSI 2015 TNIVI48 Watermarking in Hard Intellectual Property for Pre-Fab and Post-Fab Verification 2015 TNIVI49 A 0.25-V 28-nW 58-dB Dynamic Range Asynchronous Delta Sigma Modulator in 130-nm Digital CMOS Process 2015 TNIVI50 Power and Bandwidth Scalable 10-b 30-MS/s SAR ADC 2015