Understanding How Switching Activity Affects Logic Levels in Digital Circuits

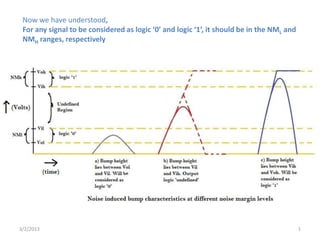

- 1. Now we have understood, For any signal to be considered as logic ‘0’ and logic ‘1’, it should be in the NML and NMH ranges, respectively 3/2/2013 1

- 2. Now we have understood, For any signal to be considered as logic ‘0’ and logic ‘1’, it should be in the NML and NMH ranges, respectively Now, let us understand the factors affecting the voltage levels to vary from this range 3/2/2013 2

- 3. Ideal Switching Activity Actual Switching Activity Switching Activity of a Device is one of the factors which affects the voltage levels of Input/Output signals

- 4. Vdd Poly Gate PMOS – P Diff In Out NMOS – N Diff Vss Lets understand the internal process while Switching Activity happens in a Device

- 5. Vdd Poly Gate PMOS – P Diff In Out NMOS – N Diff Vss PMOS NMOS Consider the MOS device, to understand the actual scenario

- 6. PMOS NMOS Let’s revise MOS device characteristics

- 17. MOS device characteristics G Vgs S D NMOS Vgs is the Voltage between gate and source

- 18. MOS device characteristics G Vgs S D NMOS

- 19. MOS device characteristics G Vgs Vgs < VT (Threshold Voltage) S D S D NMOS If Vgs is less then VT , the NMOS will act as Open Switch

- 20. MOS device characteristics G Vgs Vgs > VT (Threshold Voltage) S D S D NMOS If Vgs is greater then VT , the NMOS will act as Closed Switch

- 21. MOS device characteristics G Vgs Vgs > VT S D S D NMOS

- 22. MOS device characteristics G Vgs Vgs > VT S D S D NMOS When MOSFET is ‘ON’, it can be modeled as a ‘Resistor’ with switch closed

- 23. MOS device characteristics G Vgs Vgs > VT S D S D NMOS When MOSFET is ‘ON’, it can be modeled as a ‘Resistor’ with switch closed When MOSFET is ‘OFF’, it can be modeled as an ‘open switch’

- 24. When MOSFET is ‘ON’, it can be modeled as a ‘Resistor’ with closed switch

- 25. When MOSFET is ‘ON’, it can be modeled as a ‘Resistor’ with switch closed PMOS acts as Logic ‘0’ NMOS acts as Logic ‘1’

- 26. When MOSFET is ‘ON’, it can be modeled as a ‘Resistor’ with switch closed PMOS acts as Logic ‘0’ NMOS acts as Logic ‘1’ When MOSFET is ‘OFF’, it can be modeled as an ‘open switch’

- 27. When MOSFET is ‘ON’, it can be modeled as a ‘Resistor’ with switch closed PMOS acts as Logic ‘0’ NMOS acts as Logic ‘1’ When MOSFET is ‘OFF’, it can be modeled as an ‘open switch’ PMOS NMOS PMOS acts as Logic ‘1’ NMOS acts as Logic ‘0’

- 28. Vdd In Out Vss Input Switching from logic ‘1’ to logic ‘0’

- 29. Vdd In Out Vss Input Switching from logic ‘1’ to logic ‘0’ NMOS is turning ‘OFF’

- 30. Vdd In Out Vss Input Switching from logic ‘1’ to logic ‘0’ NMOS is turning ‘OFF’ PMOS is turning ‘ON’

- 31. Input Switching from logic ‘1’ to logic ‘0’

- 32. Input Switching from logic ‘1’ to logic ‘0’ NMOS is turning ‘OFF’

- 33. Input Switching from logic ‘1’ to logic ‘0’ NMOS is turning ‘OFF’ PMOS is turning ‘ON’

- 34. Input Switching from logic ‘1’ to logic ‘0’ NMOS is turning ‘OFF’ PMOS is turning ‘ON’ Vdd In Out Vss

- 35. Input Switching from logic ‘1’ to logic ‘0’ NMOS is turning ‘OFF’ PMOS is turning ‘ON’ Vdd Vdd R In Out Out Vss Vss Replace PMOS as resistor and NMOS by open switch.

- 36. Input Switching from logic ‘1’ to logic ‘0’ NMOS is turning ‘OFF’ PMOS is turning ‘ON’ Vdd Vdd R R Out Out CL Vss Vss Connect Capacitor on output end.

- 37. Input Switching from logic ‘1’ to logic ‘0’ NMOS is turning ‘OFF’ PMOS is turning ‘ON’ Vdd R Out CL Vss Consider Capacitor is charged when Vdd is applied.

- 38. Input Switching from logic ‘1’ to logic ‘0’ NMOS is turning ‘OFF’ PMOS is turning ‘ON’ Vdd R Out CL Vss Consider Capacitor is charged up to Vdd

- 39. Input Switching from logic ‘1’ to logic ‘0’ NMOS is turning ‘OFF’ PMOS is turning ‘ON’ Vdd R Out CL Vss

- 40. Summary Vdd Vdd R In Out Out CL Vss Vss

- 41. Summary Vdd R Out CL Vss Lets convert the area within dotted lines into closed loop circuit.

- 42. Summary Vdd R R Out Vdd CL CL Vss Lets convert into closed loop circuit.

- 43. Summary Vdd R R Out Vdd CL CL Vss Lets convert into closed loop circuit.

- 44. Summary Capacitor Models R Vdd CL

- 45. Summary Capacitor Models R Uncharged Cap + 0V short - Vdd CL + + Charged Cap V VO - O - + Fully Charged Cap Open circuit -

- 46. Summary Waveforms R Vdd CL

- 47. Summary Waveforms Vdd R Vdd CL

- 48. Summary Waveforms Vdd R VCL Vdd CL

- 49. Summary Waveforms Vdd R VCL Vdd CL VR

- 50. Summary Waveforms Vdd R VCL Vdd CL VR I = V/R

- 51. Summary Waveforms Vdd R VCL Vdd CL VR I = V/R IR

- 52. Summary Waveforms Vdd R VCL Vdd CL VR I = V/R Ipeak IR

- 53. So what can we conclude!!!

- 54. So what can we conclude!!! A capacitor needs at least Ipeak amount of current

- 55. So what can we conclude!!! A capacitor needs at least Ipeak amount of current Ipeak IR

- 56. So what can we conclude!!! A capacitor needs at least Ipeak amount of current Ipeak IR To get charged upto Vdd voltage

- 57. So what can we conclude!!! A capacitor needs at least Ipeak amount of current Ipeak IR To get charged upto Vdd voltage VCL

- 58. So what can we conclude!!! A capacitor needs at least Ipeak amount of current Ipeak IR To get charged upto Vdd voltage VCL And, the output of inverter, is recognized as logic ‘1’

- 59. So what can we conclude!!! A capacitor needs at least Ipeak amount of current Ipeak IR To get charged upto Vdd voltage VCL And, the output of inverter, is recognized as logic ‘1’

- 60. And, the output of inverter, is recognized as logic ‘1’

- 61. And, the output of inverter, is recognised as logic ‘1’ What does this mean????

- 62. And, the output of inverter, is recognised as logic ‘1’ What does this mean???? It means that the voltage across capacitor Vpeak VCL

- 63. And, the output of inverter, is recognised as logic ‘1’ What does this mean???? It means that the voltage across capacitor Vpeak VCL Lies in NMH level of noise margin graph

- 64. Vdd VOH NMH VIH Noise Margin High NMH = VOH - VIH NML = VIL - VOL VIL NML Noise Margin High VOL 0

- 65. Why to do? 3/2/2013 65