Alu description[1]

•Télécharger en tant que DOCX, PDF•

1 j'aime•1,211 vues

Signaler

Partager

Signaler

Partager

Recommandé

Recommandé

Switch designLec3 Intro to Computer Engineering by Hsien-Hsin Sean Lee Georgia Tech -- CMO...

Lec3 Intro to Computer Engineering by Hsien-Hsin Sean Lee Georgia Tech -- CMO...Hsien-Hsin Sean Lee, Ph.D.

Contenu connexe

Tendances

Switch designLec3 Intro to Computer Engineering by Hsien-Hsin Sean Lee Georgia Tech -- CMO...

Lec3 Intro to Computer Engineering by Hsien-Hsin Sean Lee Georgia Tech -- CMO...Hsien-Hsin Sean Lee, Ph.D.

Tendances (20)

Temperature Sensor with LED matrix Display BY ►iRFAN QADOOS◄ 9

Temperature Sensor with LED matrix Display BY ►iRFAN QADOOS◄ 9

Experiment write-vhdl-code-for-realize-all-logic-gates

Experiment write-vhdl-code-for-realize-all-logic-gates

Temperature sensor with a led matrix display (arduino controlled)

Temperature sensor with a led matrix display (arduino controlled)

Verilog full adder in dataflow & gate level modelling style.

Verilog full adder in dataflow & gate level modelling style.

Lec3 Intro to Computer Engineering by Hsien-Hsin Sean Lee Georgia Tech -- CMO...

Lec3 Intro to Computer Engineering by Hsien-Hsin Sean Lee Georgia Tech -- CMO...

Eceg 3201-dld-lec 11-registers_and_asynchoronous_counters

Eceg 3201-dld-lec 11-registers_and_asynchoronous_counters

En vedette

En vedette (10)

Designing of 8 BIT Arithmetic and Logical Unit and implementing on Xilinx Ver...

Designing of 8 BIT Arithmetic and Logical Unit and implementing on Xilinx Ver...

Verilog codes and testbench codes for basic digital electronic circuits.

Verilog codes and testbench codes for basic digital electronic circuits.

Design and implementation of 32 bit alu using verilog

Design and implementation of 32 bit alu using verilog

Similaire à Alu description[1]

Similaire à Alu description[1] (20)

Implementing of classical synchronization problem by using semaphores

Implementing of classical synchronization problem by using semaphores

Unit testing in iOS featuring OCUnit, GHUnit & OCMock

Unit testing in iOS featuring OCUnit, GHUnit & OCMock

Dernier

Dernier (20)

bhachau Escort💋 Call Girl (Ramya) Service #bhachau Call Girl @Independent Girls

bhachau Escort💋 Call Girl (Ramya) Service #bhachau Call Girl @Independent Girls

Overview of Lesotho 's natural beauty tourist attractions

Overview of Lesotho 's natural beauty tourist attractions

ITALY - Visa Options for expats and digital nomads

ITALY - Visa Options for expats and digital nomads

Discover Mathura And Vrindavan A Spritual Journey.pdf

Discover Mathura And Vrindavan A Spritual Journey.pdf

Udhampur Call Girls 🥰 8617370543 Service Offer VIP Hot Model

Udhampur Call Girls 🥰 8617370543 Service Offer VIP Hot Model

Vadodara Escort💋 Call Girl (Bindu) Service #Vadodara Call Girl @Independent G...

Vadodara Escort💋 Call Girl (Bindu) Service #Vadodara Call Girl @Independent G...

Birbhum Call Girls 🥰 8617370543 Service Offer VIP Hot Model

Birbhum Call Girls 🥰 8617370543 Service Offer VIP Hot Model

abortion pills in Riyadh+966572737505 Cytotec Riyadh

abortion pills in Riyadh+966572737505 Cytotec Riyadh

Abortion pills in Jeddah +966572737505 <> buy cytotec <> unwanted kit Saudi A...

Abortion pills in Jeddah +966572737505 <> buy cytotec <> unwanted kit Saudi A...

Tehri Garhwal Call Girls 🥰 8617370543 Service Offer VIP Hot Model

Tehri Garhwal Call Girls 🥰 8617370543 Service Offer VIP Hot Model

Kashipur Call Girls 🥰 8617370543 Service Offer VIP Hot Model

Kashipur Call Girls 🥰 8617370543 Service Offer VIP Hot Model

Dimapur Call Girls 🥰 8617370543 Service Offer VIP Hot Model

Dimapur Call Girls 🥰 8617370543 Service Offer VIP Hot Model

Siliguri Call Girls 🥰 8617370543 Service Offer VIP Hot Model

Siliguri Call Girls 🥰 8617370543 Service Offer VIP Hot Model

Sun World Bana Hills, Vienam Part 2 (越南 巴拿山太陽世界 下集).ppsx

Sun World Bana Hills, Vienam Part 2 (越南 巴拿山太陽世界 下集).ppsx

Howrah Call Girls 🥰 8617370543 Service Offer VIP Hot Model

Howrah Call Girls 🥰 8617370543 Service Offer VIP Hot Model

Nainital Call Girls 🥰 8617370543 Service Offer VIP Hot Model

Nainital Call Girls 🥰 8617370543 Service Offer VIP Hot Model

Alu description[1]

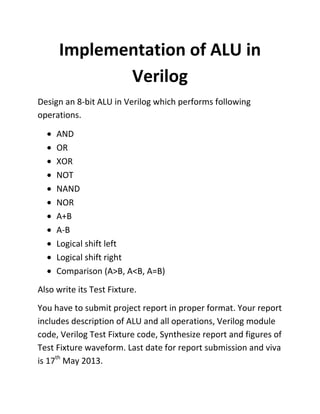

- 1. Implementation of ALU in Verilog Design an 8-bit ALU in Verilog which performs following operations. AND OR XOR NOT NAND NOR A+B A-B Logical shift left Logical shift right Comparison (A>B, A<B, A=B) Also write its Test Fixture. You have to submit project report in proper format. Your report includes description of ALU and all operations, Verilog module code, Verilog Test Fixture code, Synthesize report and figures of Test Fixture waveform. Last date for report submission and viva is 17th May 2013.

- 2. Good Luck Verilog module code `timescale 1ns / 1ps ////////////////////////////////////////////////////////////////////////////////// // Company: // Engineer: // // Create Date: 23:18:01 05/12/2013 // Design Name: // Module Name: Eight_bit_alu // Project Name: // Target Devices: // Tool versions: // Description: //

- 3. // Dependencies: // // Revision: // Revision 0.01 - File Created // Additional Comments: // ////////////////////////////////////////////////////////////////////////////////// module Eight_bit_alu(A,B,operation,out,flag_greater,flag_less,flag_equal); output [7:0]out; input[7:0]A,B; input[3:0]operation; output flag_greater,flag_less,flag_equal; reg flag_greater,flag_less,flag_equal; reg [7:0] out; always @(operation or A or B) begin if(operation==4'b0000) out=A+B; else if(operation==4'b0001) out=A-B; else if(operation==4'b0010) out=A&B; else if(operation==4'b0011) out=A|B; else if(operation==4'b0100) out=A^B; else if(operation==4'b0101) out=~A;

- 4. else if(operation==4'b0110) out=~(A&B); else if(operation==4'b0111) out=~(A|B); else if(operation==4'b1000) out=A>>B; else if(operation==4'b1001) out=A<<B; if(A==B) flag_equal=1; else flag_equal=0; if(A<B) flag_less=1; else flag_less=0; if(A>B) flag_greater=1; else flag_greater=0; end endmodule

- 5. Text fixture code: ` `timescale 1ns / 1ps //////////////////////////////////////////////////////////////////////////////// // Company: // Engineer: // // Create Date: 02:03:52 05/16/2013 // Design Name: Eight_bit_alu // Module Name: D:/ayeen/Eight_bit.v // Project Name: ayeen // Target Device: // Tool versions: // Description: // // Verilog Test Fixture created by ISE for module: Eight_bit_alu // // Dependencies: // // Revision: // Revision 0.01 - File Created // Additional Comments: // //////////////////////////////////////////////////////////////////////////////// module Eight_bit; // Inputs

- 6. reg [7:0] A; reg [7:0] B; reg [3:0] operation; // Outputs wire [7:0] out; wire flag_greater; wire flag_less; wire flag_equal; // Instantiate the Unit Under Test (UUT) Eight_bit_alu uut ( .A(A), .B(B), .operation(operation), .out(out), .flag_greater(flag_greater), .flag_less(flag_less), .flag_equal(flag_equal) ); initial begin // Initialize Inputs A = 1; B = 0; operation = 0; // Wait 100 ns for global reset to finish #100;

- 7. A = 1; B = 0; operation = 1; // Wait 100 ns for global reset to finish #100; A = 1; B = 0; operation = 2; // Wait 100 ns for global reset to finish #100; A = 1; B = 0; operation = 3; // Wait 100 ns for global reset to finish #100; A = 1; B = 0; operation = 4; // Wait 100 ns for global reset to finish #100; // Add stimulus here A = 1; B = 0;

- 8. operation = 5; // Wait 100 ns for global reset to finish #100; A = 1; B = 0; operation = 6; // Wait 100 ns for global reset to finish #100; A = 1; B = 0; operation = 6; // Wait 100 ns for global reset to finish #100; A = 1; B = 0; operation = 7; // Wait 100 ns for global reset to finish #100; A = 1; B = 0; operation = 8; // Wait 100 ns for global reset to finish #100;

- 9. A = 1; B = 0; operation = 9; // Wait 100 ns for global reset to finish #100; end endmodule

- 11. simulation