CV_jcrannou_fr_2017-01-09

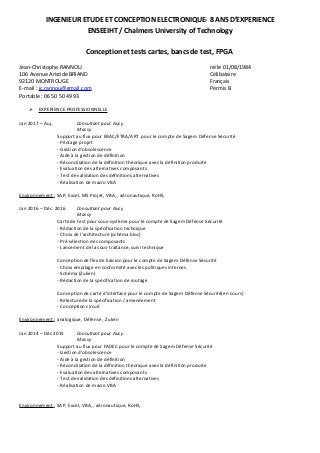

- 1. INGENIEUR ETUDE ET CONCEPTION ELECTRONIQUE- 8 ANS D’EXPERIENCE ENSEEIHT / Chalmers University of Technology Conception et tests cartes, bancs de test, FPGA Jean-Christophe RANNOU né le 01/08/1984 106 Avenue Aristide BRIAND Célibataire 92120 MONTROUGE Français E-mail : jc.rannou@gmail.com Permis B Portable : 06 50 50 49 93 EXPERIENCE PROFESSIONNELLE Jan 2017 – Auj. Consultant pour Ausy Massy Support au flux pour EBAC/ETRA/ART pour le compte de Sagem Défense Sécurité - Pilotage projet - Gestion d'obsolescence - Aide à la gestion de définition - Réconciliation de la définition théorique avec la définition produite - Evaluation des alternatives composants - Test de validation des définitions alternatives - Réalisation de macro VBA Environnement : SAP, Excel, MS Projet, VBA, , aéronautique, RoHS, Jan 2016 – Déc. 2016 Consultant pour Ausy Massy Carte de test pour sous-système pour le compte de Sagem Défense Sécurité - Rédaction de la spécification technique - Choix de l'architecture (schéma bloc) - Pré-sélection des composants - Lancement de la sous-traitance, suivi technique Conception de flex de liaision pour le compte de Sagem Défense Sécurité - Choix empilage en conformité avec les politiques internes - Schéma (Zuken) - Rédaction de la spécification de routage Conception de carte d'interface pour le compte de Sagem Défense Sécurité(en cours) - Relecture de la spécification / amendement - Conception circuit Environnement : analogique, Défense, Zuken Jan 2014 – Déc 2015 Consultant pour Ausy Massy Support au flux pour FADEC pour le compte de Sagem Défense Sécurité - Gestion d'obsolescence - Aide à la gestion de définition - Réconciliation de la définition théorique avec la définition produite - Evaluation des alternatives composants - Test de validation des définitions alternatives - Réalisation de macro VBA Environnement : SAP, Excel, VBA, , aéronautique, RoHS,

- 2. Avr 2013 – Aout 2013 Ingénieur pour IVSYS, Argenteuil Sous-traitance électronique : - Spécifications du système et des test - Etudes et conception - Supervision de la réalisation - Intégration - Acceptation Projets réalisés - Firmware FPGA pour une carte de commande de d'essuie-glace de train - Boîtier d'éclatement pour l'intégration d'un calculateur aéronautique - Re-engineering documentaire de la spécification du « système Interlock SPC » (DO 254 DAL A) Environnement : Cycle en V, VHDL, FPGA, Xilinx, Altera, Actel, ISE,aéronautique Oct 2011 – Avril 2013 Responsable Banc de production XMA pour Zodiac Data Systems, Les Ulis (équipe de 2 personnes). Spécification et débug des procédures de test unitaires des modules XMA Spécification et débug des procédures de test unitaires de codeur XMA Caractérisation et débug du prototype du banc Pré-étude du design - Architecture système - Augmentation de la cadence de calibration des modules analogiques - Industrialisation des environnements de mesure Spécification du banc (HW, SW, FPGA) Choix des sous-systèmes du commerce (calibrateur, multimètre…) Conception d’une matrice de brassage - Architecture - Schéma - Suivi de la sous-traitance Test d’intégration du banc Environnement : Cycle en V, FPGA, VHDL, Xilinx, ISE, télémesure, aéronautique, production Jui 2010 – Oct 2011 Responsable module analogique XMA pour Zodiac Data Systems, Les Ulis (équipe de 3 personnes). Mise au point module d’acquisition analogique pour un codeur de télémesure - Aide à la mise au point de l’interfaçage avec le progiciel de commande, de contrôle et de restitution - Supervision de la mise point analogique - Mise au point numérique (débug FPGA) - Spécification de la procédure de calibration du module - Supervision de la vérification du module - Aide à l’intégration système du module - Débug des premiers produits de série - Spécification, conception et vérification du système d’acquisition de capteur thermocouple type K. Analyses, spécification, conception et vérification d’une évolution du module Recrutement de prestataires Environnement : Cycle en V, FPGA, VHDL, Xilinx, Actel,ISE, Libero télémesure, aéronautique Oct 2008 – Jul 2010 Ingénieur Etudes et Conception électronique (projet XMA) pour Zodiac Data Systems, Les Ulis Conception d’un module d’acquisition analogique pour un codeur de télémesure : Ce module est une carte de 2'' par 3'' qui permet d'acquérir des tension sur 8 voies sur des étendues de mesures configurable logiciellement comprises entre +/- 16 mV (précision 0,5%) et +/- 10,24V (précision 0,05%) sur la bande [0 Hz ; 20kHz]. Repliement de spectre dans la bande -70 dB . Il permet de plus de conditionner 8 capteurs avec un courant configurable entre 0 et 20 mA (2 µA de précision). Ces performances sont garanties pour une utilisation entre -55°C et 105°C. - Spécification technique du module - Etude de la voie analogique d’acquisition et de conditionnement - Etude de la solution numérique de traitement de données et configuration - Supervision du placement routage - Conception, réalisation et vérification du firmware FPGA - Conception et réalisation du banc de test (supervision de sous-traitant) Recrutement de prestataires Environnement : Cycle en V, OrCAD, FPGA, VHDL, , Xilinx, Actel,ISE, Libero, aéronautique, télémesure

- 3. Jui – Aout 2008 IT assistant pour Service Pétrolier Transocean, Montrouge et La Défense - Responsable du déménagement du parc informatique (dont réseau) des bureaux de Montrouge à ceux de la Défense - Evaluer l’obsolescence du stock informatique et supervision de l’élimination des matériels obsolètes - Support informatique et réseaux 2007-2008 Master Thesis / Projet de fin d’étude pour la DLR (Munich, Allemagne) Design of an active patch antenna array in LTTC (Conception d’un réseau d’antennes actives patches en LTTC) - Mise à jour de l’antenne constitutive du réseau - Conception de la partie active (choix de l’amplificateur de puissance et du déphaseur, placement-routage) - Conception d’un circuit expérimental Environnement : Hyperfréquence, Ansoft designer, HFSS, projet ATENAA, communication satellitaire FORMATIONS 2012 Implémentation de FPGA - Techniques avancées MVD training à Sèvres 2011 Convaincre pour agir sans pouvoir hiérarchique DEMOS à Paris 2010 Expert VHDL Amblot à Paris 2010 Synthèse logique et simulation VHDL pour Conception de FPGA Xilinx chez MVD training à Sèvres ETUDES 2006 – 2008 Chalmers University of technology, Göteborg, Suède International Master in Hardware for Wireless Communication 2004-2008 ENSEEIHT, Toulouse Diplôme d’ingénieur en électronique ENSEEIHT 2002-2004 Classes préparatoires aux Grandes Ecoles, Lycée Carnot, Dijon MPSI, MP 2001-2002 Baccalauréat Scientifique spécialité mathématique Mention AB LANGUES ET COMPETENCES INFORMATIQUES Langues : - Français : langue natale - Anglais : courant - Allemand : bases - Russe : débutant Informatique : Connaissance de C++, Matlab, Scilab, Mapple, CamL, VHDL, ISE, ADS, HFSS, Ansoft designer, Microsoft office ACTIVITES EXTRA-PROFESSIONNELLES 2008 Professeur de Mathématiques, Physique et Chimie niveau Bac S 2005-2006 Délégué de promotion 2003-2013 Membre actif (Vice-Président en 2011-2012) d’une association organisant des activités extra-scolaires pour des adolescents HOBBIES Géopolitique, Histoire, lecture, musique VOYAGES ET SEJOURS A L'ETRANGER Voyages réguliers en Europe et aux Etats-Unis, 1 mois en Grande-Bretagne, 8 mois en Allemagne, 1 an en Suède, 2 ans au Congo