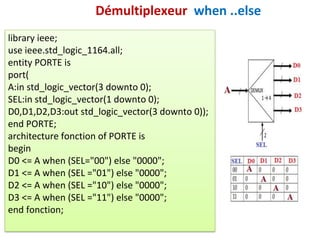

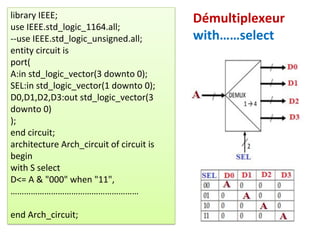

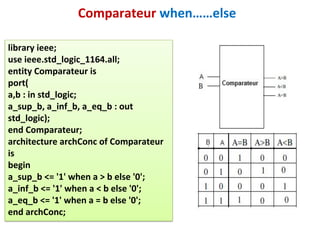

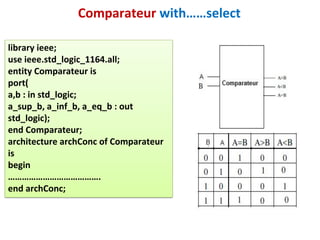

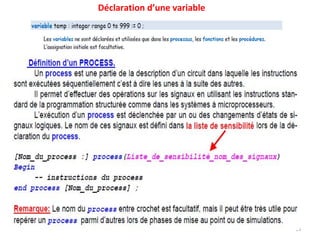

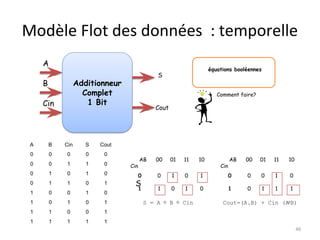

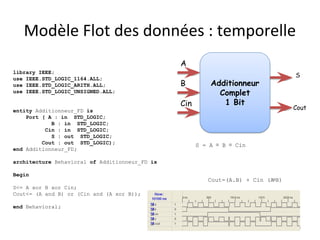

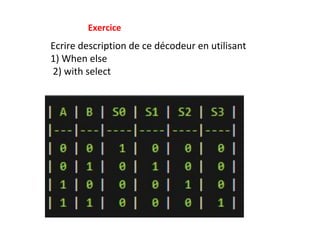

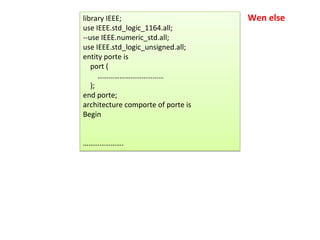

Le document traite des opérateurs relationnels dans la programmation avancée et leur utilisation pour modifier l'état des signaux en fonction de conditions logiques. Il explique les instructions de type « when ... else ... » et « with ... select ... » pour effectuer des affectations conditionnelles et sélectives, accompagner des exemples de code VHDL. Des structures comme les multiplexeurs et décodeurs sont présentées, mettant en avant l'importance d'une définition complète pour tous les cas possibles des signaux de sélection.

![Entré

A2 A1 A0 S1 S0

0 0 1 1 1

1 0 0 0 1

1 0 1 1 0

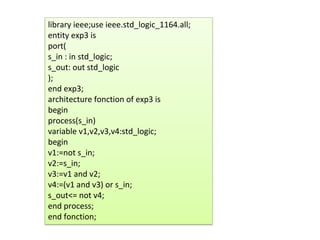

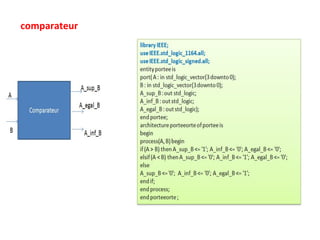

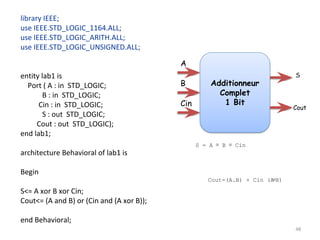

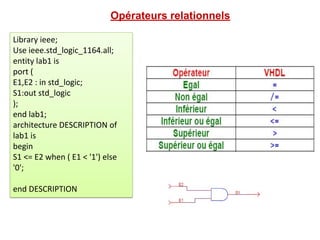

library IEEE;

use IEEE.std_logic_1164.all;

use IEEE.std_logic_unsigned.all;

entity table is

port(

A:in std_logic_vector(2 downto 0);

S: out std_logic_vector(1 downto 0)

);

End table;

architecture comporte of table is

Begin

with A select

S <= "11" when "001",

"01" when "100",

"10" when "101",

"00" when others;

end comporte ;

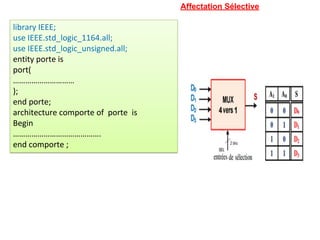

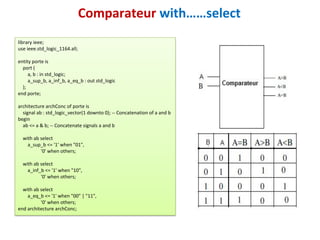

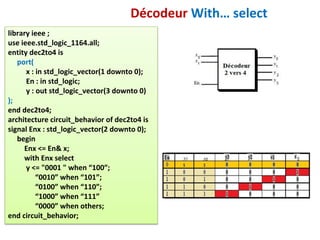

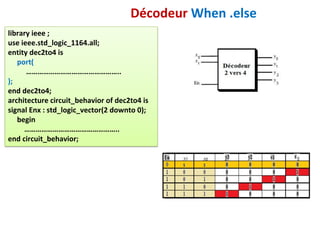

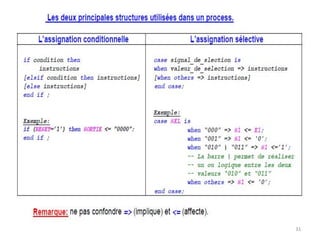

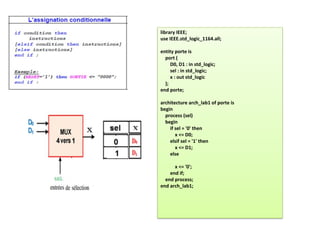

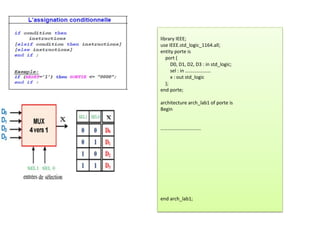

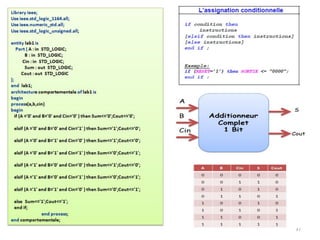

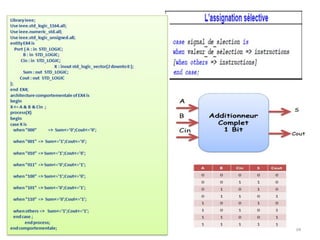

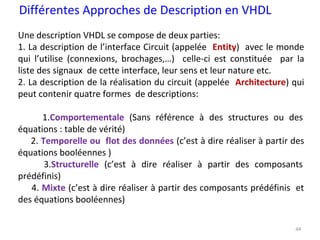

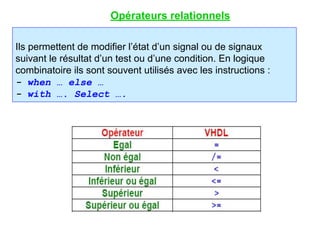

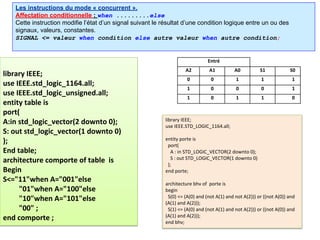

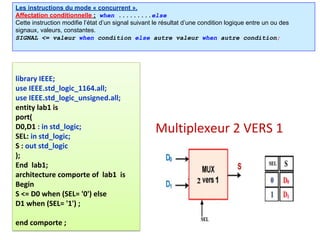

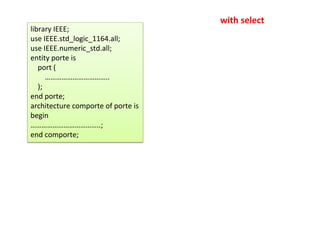

Les instructions du mode « concurrent ».

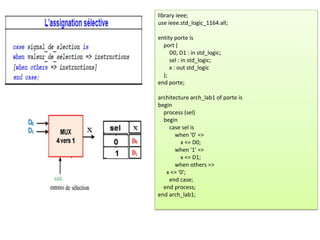

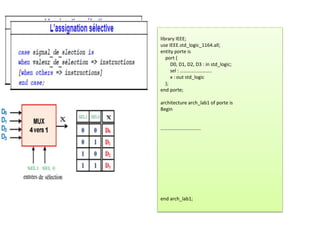

Affectation Sélective : with ……. select

Cette instruction permet d’affecter différentes valeurs à un signal, selon les valeurs prises par un signal dit de

sélection

.with SIGNAL_DE_SELECTION select SIGNAL <= expression when valeur_de_selection,

[expression when valeur_de_selection,]

[expression when others];

library IEEE;

use IEEE.std_logic_1164.all;

use IEEE.std_logic_unsigned.all;

entity table is

port(

A:in std_logic_vector(2 downto 0);

S: out std_logic_vector(1 downto 0)

);

End table;

architecture comporte of table is

Begin

S<="11"when A="001"else

"01"when A="100"else

"10"when A="101"else

"00" ;

end comporte ;](https://image.slidesharecdn.com/ch2vhdl-240313192925-7c1c35d8/85/ch2-vhkwvdvddkwbdndbw-x-ffbxbbfbfbfdl-pdf-9-320.jpg)

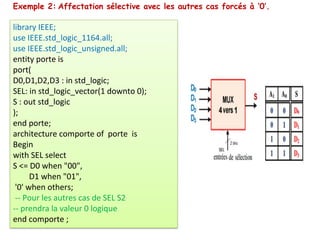

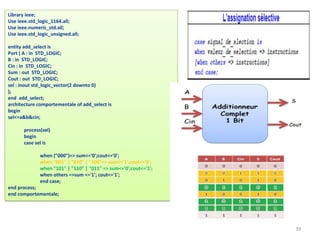

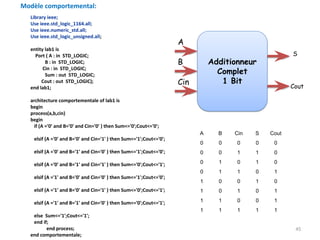

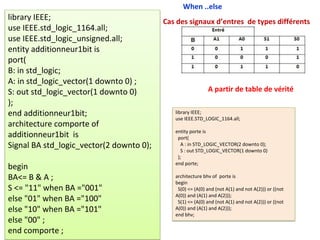

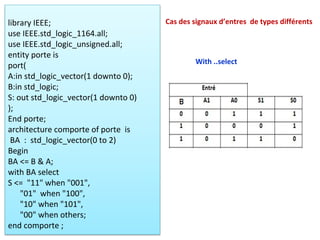

![Multiplexeur 2 VERS 1

library IEEE;

use IEEE.std_logic_1164.all;

use IEEE.std_logic_unsigned.all;

entity MUX is

port( D0,D1 , SEL : in std_logic;

S : out std_logic );

end MUX;

architecture comporte of MUX is

Begin

with SEL select

S <= D0 when '0',

D1 when '1',

'0' when others;

end comporte ;

Remarque: when others est nécessaire

car il faut toujours définir les autres cas du signal de

sélection pour prendre en compte toutes les valeurs

possibles de celui-ci. Schéma correspondant après

synthèse:

Les instructions du mode « concurrent ».

Affectation Sélective :

with SIGNAL_DE_SELECTION select SIGNAL <= expression when

valeur_de_selection, [expression when valeur_de_selection,]

[expression when others];](https://image.slidesharecdn.com/ch2vhdl-240313192925-7c1c35d8/85/ch2-vhkwvdvddkwbdndbw-x-ffbxbbfbfbfdl-pdf-14-320.jpg)