⭐⭐⭐⭐⭐ DISEÑO DE SISTEMAS DIGITALES, EXAMEN B RESUELTO 1er PARCIAL (2019 1er Término)

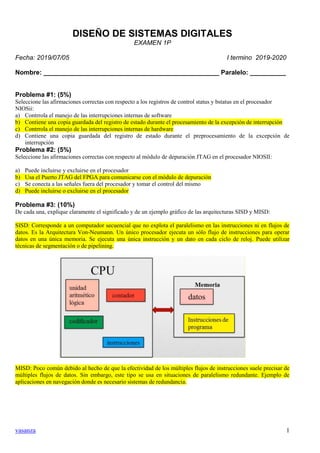

- 1. vasanza 1 DISEÑO DE SISTEMAS DIGITALES EXAMEN 1P Fecha: 2019/07/05 I termino 2019-2020 Nombre: _________________________________________________ Paralelo: __________ Problema #1: (5%) Seleccione las afirmaciones correctas con respecto a los registros de control status y bstatus en el procesador NIOSii: a) Contrrola el manejo de las interrupciones internas de software b) Contiene una copia guardada del registro de estado durante el procesamiento de la excepción de interrupción c) Contrrola el manejo de las interrupciones internas de hardware d) Contiene una copia guardada del registro de estado durante el preprocesamiento de la excepción de interrupción Problema #2: (5%) Seleccione las afirmaciones correctas con respecto al módulo de depuración JTAG en el procesador NIOSII: a) Puede incluirse y excluirse en el procesador b) Usa el Puerto JTAG del FPGA para comunicarse con el módulo de depuración c) Se conecta a las señales fuera del procesador y tomar el control del mismo d) Puede incluirse o excluirse en el procesador Problema #3: (10%) De cada una, explique claramente el significado y de un ejemplo gráfico de las arquitecturas SISD y MISD: SISD: Corresponde a un computador secuencial que no explota el paralelismo en las instrucciones ni en flujos de datos. Es la Arquitectura Von-Neumann. Un único procesador ejecuta un sólo flujo de instrucciones para operar datos en una única memoria. Se ejecuta una única instrucción y un dato en cada ciclo de reloj. Puede utilizar técnicas de segmentación o de pipelining. MISD: Poco común debido al hecho de que la efectividad de los múltiples flujos de instrucciones suele precisar de múltiples flujos de datos. Sin embargo, este tipo se usa en situaciones de paralelismo redundante. Ejemplo de aplicaciones en navegación donde es necesario sistemas de redundancia.

- 2. vasanza 2 Problema #4: (5%) Completar el siguiente cuadro: Taxonomía de Flynn Múltiples instrucciones Una instrucción Múltiples datos MIMD SIMD Un Dato MISD SISD Problema #5: (5%) ¿Cuál es la principal diferencia entre ASB y AHB? • Advanced System Bus (ASB) fue la primera versión de la especificación AMBA en el procesador ARM. • Advances High Performance Bus (AHB) es una versión de la especificación AMBA bastante costosa para un sistema integrado y otro sistema sensible al costo. Problema #6: (5%) De acuerdo con la siguiente figura, ¿qué resultado debería imprimirse?

- 3. vasanza 3 a) Value of i:10 Value of i reference:5 Value of d: 11.7 Value of d reference:5 b) Value of i:5 Value of i reference:5 Value of d: 11.7 Value of d reference:11.7 c) Value of i:10 Value of i reference:5 Value of d:1.7 Value of d reference:11.7 d) Value of i:5 Value of i reference:5 Value of d:1.7 Value of d reference:11.7 Problema #7: (5%) Seleccione las opciones correctas con respecto a los registros de control pteaddr y tlbacc en el procesador: a) Es usado para acceder a las entradas TLB y está disponible en sistemas con una MMU. b) Guarda valores que el software leerá en una entrada TLB. c) Es usado para acceder a las entradas ACC y está disponible en sistemas con una MMU. d) Guarda la dirección virtual de la tabla de las páginas del Sistema operative. Problema #8: (5%) Indique, cual es la diferencia entre los registros de control ipending, cpuid, exception: a) Ipending: indica el valor de las señales de interrupción habilitadas dirigidas al procesador. b) Cpuid: contiene un valor constante que usted define en el editor de parámetros del Procesador Nios II para identificar de manera única cada procesador en un sistema multiprocesador. c) Exception: El procesador Nios II / f proporciona información útil para el software del sistema para el procesamiento de excepciones en los registros de excepción y badaddr cuando se produce una excepción. Problema #9: (5%) Una con líneas según corresponda la combinación de procesadores: Xilinx o Altera Open CL Altera o Xilinx Vivado High Level Synthesis Otras Herramientas o ARM SoC / Cyclone V o ARM SoC / Arria V o Zynq – 7000 o ZedBoard Problema #10: (10%) Demostrar gráficamente (poner nombras claros a cada bloque) la diferencia entre: • MPSoC de procesadores no interconectados

- 4. vasanza 4 • MPSoC interconectados mediante bus de propósito general • MPSoC de memoria compartida Problema #11: (10%) Demostrar gráficamente (poner nombras claros a cada bloque) la diferencia entre las arquitecturas: • MPSoC en configuración Maestro – Esclavo

- 5. vasanza 5 • MPSoC Segmentada Problema #12: (5%) Complete utilizando las opciones el siguiente cuadro comparativo entre Proccessor y FPGA: • Opciones o DMA controller o DMA, interrupt, and bus control drivers o Networking and peripheral I/O drivers o Specialized I/O drivers and interface o Application software o Application IP o Real-time OS o DSP IP o Control IP o Specialized I/O

- 6. vasanza 6 Problema #13: (5%) De acuerdo con la siguiente figura, colocar los nombres a los bloques que conforman la arquitectura del bus AVALON: • Opciones o Avalon Switch Fabric o UART o LCD Display Driver o Buttons, LEDs, etc. o CompactFlash Interface o Compact Flash o Ethernet MAC/PHY o SDRAM Controller o JTAG Debug Module o JTAG connection to software debugger o Flash Memory o SRAM Memory

- 7. vasanza 7 Problema #14: (20%) Shen et Al., escribió el paper titulado “An FPGA-based Distributed Computing System with Power and Thermal Management Capabilities” en donde desarrolla una plataforma computacional distribuida compuesta de múltiples FPGAs conectadas via Ethernet y cada FPGA está configurada como un sistema multi-core. Los núcleos en el mismo FPGA se comunican a través de la memoria compartida, mientras que diferentes FPGA se comunican a través de enlaces Ethernet, como se muestra en la siguiente gráfica: Fig. Arquitectura del sistema distribuido Las FPGAs están en las tarjetas de desarrollo Altera Nios II Embedded Evaluation Kit (NEEK), la edición de Altera NEEK Cyclone III tiene un Cyclone III EP3C25F324 FPGA con 25,000 elementos lógicos y 594 Kbits Memoria incorporada, 32 MB DDR SDRAM, 1 MB SRAM, 16 MB Flash Intel P30 / P33, pantalla táctil de 800 X 480, Ethernet 10/100 Mbps, y conector PS2 y RS-232. Desarrollar el diagrama de bloques basado en el NIOSii processor que considere debió utilizar Shen et Al. en cada una de las FPGA, basado en las siguientes especificaciones: • El JTAG UART proporciona la interfaz de puerto de depuración. • Se incluye un temporizador de alta resolución para medir el tiempo de ejecución del programa. • La E / S paralela (PIO) proporciona control y monitoreo al reloj. • Una o varias memorias compartidas están conectadas a cada subsistema Nios II. Estas memorias compartidas se configuran como Mailbox de hardware para las comunicaciones entre los procesadores en el mismo FPGA. • Entre todos los subsistemas Nios II en el mismo FPGA, hay uno que tiene un módulo de interfaz Ethernet. • El módulo de interfaz Ethernet consta de un controlador Direct Memory Access (DMA), una memoria de descriptor y el MAC de Ethernet. • El subsistema Nios II que tiene la interfaz Ethernet que actúa como una puerta de enlace para las comunicaciones entre FPGA en el sistema informático distribuido. • Todos los periféricos están conectados al procesador Nios II a través de la interfaz mapeada en memoria de Avalon. • La interfaz de transmisión de Avalon se utiliza para conectar el DMA al controlador Ethernet. Fuente: Shen, H., & Qiu, Q. (2011, July). An FPGA-based distributed computing system with power and thermal management capabilities. In 2011 Proceedings of 20th International Conference on Computer Communications and Networks (ICCCN) (pp. 1-6). IEEE.

- 8. vasanza 8 Respuesta: Diseño SoPC en las FPGAs