9 d55201 testing & testability

•

1 j'aime•2,725 vues

Question papers for 2nd sem jntu anantapur students

Signaler

Partager

Signaler

Partager

Télécharger pour lire hors ligne

Recommandé

Recommandé

Contenu connexe

Tendances

Tendances (20)

Digital Signal Processing Tutorial: Chapt 4 design of digital filters (FIR)

Digital Signal Processing Tutorial: Chapt 4 design of digital filters (FIR)

System partitioning in VLSI and its considerations

System partitioning in VLSI and its considerations

Designing of 8 BIT Arithmetic and Logical Unit and implementing on Xilinx Ver...

Designing of 8 BIT Arithmetic and Logical Unit and implementing on Xilinx Ver...

Analog & Digital Integrated Circuits - Material (Short Answers)

Analog & Digital Integrated Circuits - Material (Short Answers)

Design of Synthesizable Asynchronous FIFO And Implementation on FPGA

Design of Synthesizable Asynchronous FIFO And Implementation on FPGA

En vedette

En vedette (6)

Similaire à 9 d55201 testing & testability

8th Semester Computer Science (2013-June) Question Papers

8th Semester Computer Science (2013-June) Question PapersBGS Institute of Technology, Adichunchanagiri University (ACU)

5th Semester CS / IS (2013-June) Question Papers

5th Semester CS / IS (2013-June) Question PapersBGS Institute of Technology, Adichunchanagiri University (ACU)

7th Semester (June; July-2015) Computer Science and Information Science Engineering Question Papers7th Semester (June; July-2015) Computer Science and Information Science Engin...

7th Semester (June; July-2015) Computer Science and Information Science Engin...BGS Institute of Technology, Adichunchanagiri University (ACU)

1st Semester M Tech Computer Science and Engg (Dec-2013) Question Papers

1st Semester M Tech Computer Science and Engg (Dec-2013) Question Papers BGS Institute of Technology, Adichunchanagiri University (ACU)

Similaire à 9 d55201 testing & testability (20)

8th Semester Computer Science (2013-June) Question Papers

8th Semester Computer Science (2013-June) Question Papers

7th Semester (June; July-2015) Computer Science and Information Science Engin...

7th Semester (June; July-2015) Computer Science and Information Science Engin...

Computer Networks Jntu Model Paper{Www.Studentyogi.Com}

Computer Networks Jntu Model Paper{Www.Studentyogi.Com}

C O M P U T E R N E T W O R K S J N T U M O D E L P A P E R{Www

C O M P U T E R N E T W O R K S J N T U M O D E L P A P E R{Www

1st Semester M Tech Computer Science and Engg (Dec-2013) Question Papers

1st Semester M Tech Computer Science and Engg (Dec-2013) Question Papers

Digital Ic Applications Jntu Model Paper{Www.Studentyogi.Com}

Digital Ic Applications Jntu Model Paper{Www.Studentyogi.Com}

D I G I T A L I C A P P L I C A T I O N S J N T U M O D E L P A P E R{Www

D I G I T A L I C A P P L I C A T I O N S J N T U M O D E L P A P E R{Www

Plus de Vinod Kumar Gorrepati

Plus de Vinod Kumar Gorrepati (20)

9 d55201 testing & testability

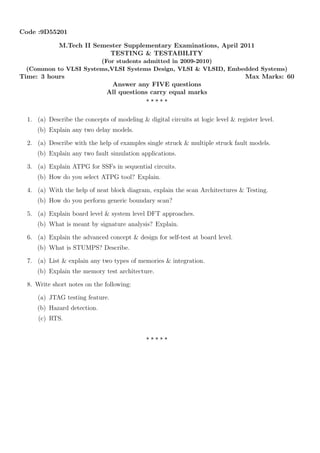

- 1. Code :9D55201 M.Tech II Semester Supplementary Examinations, April 2011 TESTING & TESTABILITY (For students admitted in 2009-2010) (Common to VLSI Systems,VLSI Systems Design, VLSI & VLSID, Embedded Systems) Time: 3 hours Max Marks: 60 Answer any FIVE questions All questions carry equal marks ⋆ ⋆ ⋆ ⋆ ⋆ 1. (a) Describe the concepts of modeling & digital circuits at logic level & register level. (b) Explain any two delay models. 2. (a) Describe with the help of examples single struck & multiple struck fault models. (b) Explain any two fault simulation applications. 3. (a) Explain ATPG for SSFs in sequential circuits. (b) How do you select ATPG tool? Explain. 4. (a) With the help of neat block diagram, explain the scan Architectures & Testing. (b) How do you perform generic boundary scan? 5. (a) Explain board level & system level DFT approaches. (b) What is meant by signature analysis? Explain. 6. (a) Explain the advanced concept & design for self-test at board level. (b) What is STUMPS? Describe. 7. (a) List & explain any two types of memories & integration. (b) Explain the memory test architecture. 8. Write short notes on the following: (a) JTAG testing feature. (b) Hazard detection. (c) RTS. ⋆ ⋆ ⋆ ⋆ ⋆