Lect 7: Verilog Behavioral model for Absolute Beginners

- 1. Digital Design Using Verilog - For Absolute Beginners LEC 7 :Verilog Behavioral Model

- 2. Introduction • This model is considered as the highest level of abstraction in the Verilog design modelling methods. •It is also popularly known as Procedural assignment. •Verilog behavioral model procedural statements control the simulation and manipulate variables of the data types . •This behavioral model provides a wide scope for the designer to build any complex design which can be properly simulated and synthesized.

- 3. contd • These statements are contained within procedures. Each procedure has an activity flow associated with it. •The procedural block of Verilog HDL is defined as “a region of code containing sequential statements. •There are two types of procedural blocks. (i).The always block & (ii).The initial block • Each initial construct and each always construct starts a separate activity flow. • All of the activity flows are concurrent to model the inherent concurrence of hardware.

- 4. Procedural assignments • Procedural assignments are used for updating reg, integer, time, real, realtime,and memory data types. • There is a significant difference between procedural assignments and continuous assignments: Continuous assignments drive nets and are evaluated and updated whenever an input operand changes its value. Procedural assignments update the value of variables under the control of the procedural flow constructs that surround them.

- 5. The always Block • The ‘always’ block is a continuous loop that never terminates. • A Verilog module can contain any number of ‘always’ blocks and all these blocks are executed concurrently. • The basic syntax of always block is always @ (sensitivity list) begin statement 1 ------------ statement n end

- 6. contd 23 June 2020 6yayavaram@yahoo.com • The sequential statements are executed if and if only ,the signals of the sensitivity list changes . • The LHS of the statements in ‘always ‘ block is reg type only. • Ex: let us consider an example code. module my-mux(A,B,S,Q,Q_b); input A,B,S; output Q,Q_b; reg Q,Q_b;

- 7. always @(A or B or S) begin if(S) Q = A; // procedural descriptions else Q = B; end assign Q = ~Q_b; // continuous assignment endmodule 23 June 2020 7yayavaram@yahoo.com contd

- 8. The Initial Block • The initial block is typically used to write test bench for simulation. • It specifies the stimulus to be applied to the DUT. • The initial block is executed only once at the beginning of the simulation used in the test bench. 23 June 2020 8yayavaram@yahoo.com

- 9. Illustration • module behave; [1:0] a, b; initial begin a = 1’b1; b = 1’b0; end always begin #50 a = ~a; end always begin #100 b = ~b; end endmodule 23 June 2020 9 yayavaram@yahoo.com

- 10. contd • In this model, the reg variables a and b initialize to 1 and 0 respectively at simulation time zero. • The initial construct is then complete and does not execute again during this simulation run. • This initial construct contains a begin-end block (also called a sequential block) of statements. In this begin-end block a is initialized first, followed by b. • The always constructs also start at time zero 23 June 2020 10yayavaram@yahoo.com

- 11. contd • But the values of the variables do not change until the times specified by the delay controls (introduced by #) have elapsed. • Thus, reg a inverts after 50 time units and reg b inverts after 100 time units. • Since the always constructs repeat, this model will produce two square waves. • The reg a toggles with a period of 100 time units, and reg b toggles with a period of 200 time units. • The two always constructs proceed concurrently throughout the entire simulation run. 23 June 2020 11yayavaram@yahoo.com

- 12. Different Sequential Statements (i).begin sequential statements end Note: If there is a single statement in the block ‘begin’ and ‘end ‘ not required (ii).if(expression) Sequential statement else Sequential statement 23 June 2020 12yayavaram@yahoo.com

- 13. contd • (iii).case(expression) expr1 : Sequential statement 1 ……….. expr n : Sequential statement n default : Sequential statement endcase • (iv).forever Sequential statemet 23 June 2020 13yayavaram@yahoo.com

- 14. • (v). Repeat(expression) Sequential statement • (vi). while(expression) Sequential statement • (vii). for (expr1:expr2:expr3) Sequential expression • (viii).@(event_expression) This makes a block of statements suspend until event expression triggers. 23 June 2020 14yayavaram@yahoo.com

- 15. Ex: Sequential Logic (D-F/F) • module ex_Dff(D,clk,Q,Qb); input D,clk ; output Q,Qb; reg Q, Qb ; always @(negedge clk) begin Q = D; Qb = ~D; end endmodule 23 June 2020 15yayavaram@yahoo.com

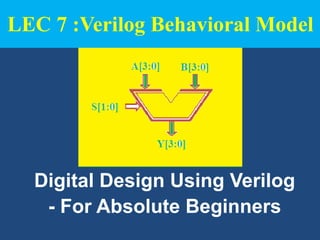

- 16. Ex: 4 Bit ALU • module ex_ALU4(Y,A,B,S); input [3:0]A,B; input [1:0] S ; output [3:0] Y; Parameter ADD=2’b00, SUB =2’b01, MUL = 2’10, DIV = 2’b11; always @(A or B or S) case (S) ADD : Y = A+B; 23 June 2020 16yayavaram@yahoo.com

- 17. contd SUB : Y = A-B ; MUL : Y=A * B ; DIV : Y = A/B; endcase endmodule 23 June 2020 17yayavaram@yahoo.com

- 18. 23 June 2020 18yayavaram@yahoo.com

Notes de l'éditeur

- If the value of S is 1 ,then Y= B other wise Y= A