Need of Decoupling Capacitor

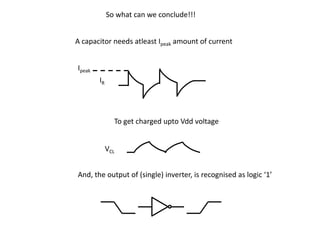

- 1. So what can we conclude!!! A capacitor needs atleast Ipeak amount of current Ipeak IR To get charged upto Vdd voltage VCL And, the output of (single) inverter, is recognised as logic ‘1’

- 2. Consider the amount of the switching current required For a complex block something like below

- 3. Consider the amount of the switching current required For a complex block something like below

- 4. Why to do? 1. If the wires were ideal, i.e. 'zero' resistance, 'zero' inductance and infinitely short, thus no issue of power distribution 3/2/2013 4

- 5. Why to do? 1. Consider capacitance to be zero for the discussion. Rdd, Rss, Ldd and Lss are well defined values. 2. During switching operation, the circuit demands switching current i.e. peak current (Ipeak). 3. Now, due to the presence of Rdd and Ldd, there will be a voltage drop across them and the voltage at Node 'A' would be Vdd' instead of Vdd. 3/2/2013 5

- 6. Why to do? 1. When input of the inverter switches from logic '1' to logic '0', output of inverter should switch from logic '0' to logic '1'. 2. This essentially means that the output capacitance of inverter should charge till the supply voltage Vdd'. 3. But if Vdd' goes below the noise margin, due to Rdd and Ldd, the logic '1' at the output of inverter wont be detected as logic '1' at the input of the Vdd - Vdd' = Ipeak*Rdd + Ldd * (dI/dt) circuit following the inverter. 3/2/2013 6

- 7. Why to do? Solution 1. Keep Rdd and Rss minimum by increasing width of wire. 2. Keep peak current Ipeak and change in current dI/dt as small as possible. Ipeak = CL * Vdd / tr dI/dt = CL * Vdd / tr2 3. Limit the rise time (tr). If a circuit could run at 500 ps, its unnecessary to run the circuit at 300 ps. The largest possible value of tr should be selected. Vdd - Vdd' = Ipeak*Rdd + Ldd * (dI/dt) 3/2/2013 7

- 8. Why to do? 1. Addition of Decoupling Capacitor in parallel with the circuit 2. Everytime the critical cell (in above daigram,an inverter) switches, it draws current from Cd , whereas, the RL network is used to replenish the charge into Cd 3/2/2013 8

- 9. We have taken care of local communication

- 10. We have taken care of local communication Now, Consider the below scenario

- 13. Driver

- 14. Driver Load

- 15. Driver Load

- 16. Driver Load

- 17. Driver Load

- 18. Driver Load

- 19. Driver Load

- 20. Driver Load

- 21. Driver Load

- 22. Driver Load

- 23. Driver Load Let us trace the path of current when Driver is ‘Switching’

- 24. Driver Load Let us trace the path of current when Driver is ‘Switching’

- 25. Driver Load Let us trace the path of current when Driver is ‘Switching’

- 26. Driver Load Let us trace the path of current when Driver is ‘Switching’

- 27. Driver Load Let us trace the path of current when Driver is ‘Switching’

- 28. Driver Load Let us trace the path of current when Driver is ‘Switching’

- 29. Driver Load No Decoupling Capacitors are involved in the path through ‘Blue’ line

- 30. Driver Load Hence, switching through ‘Blue’ line will need peak current, which has to supplied by Vdd

- 31. Driver Load And not through Decaps.

- 32. Driver Load This will lead to ‘voltage droop’ and ‘ground bounce’, i.e. disturbance in power supply network

- 33. Driver Load Assume, the ‘Blue’ path is a 16-bit bus

- 34. Also assume, the 16-bit bus is having present data as below 1110010111000110

- 35. Also assume, the 16-bit bus is having present data as below 1110010111000110

- 36. Also assume, the 16-bit bus is having present data as below 1110010111000110

- 37. Also assume, the 16-bit bus is having present data as below 1110010111000110 V V V V V V V V V

- 38. Also assume, the 16-bit bus is having present data as below 1110010111000110 V V V 0 0 V 0 V V V 0 0 0 V V 0

- 39. V V V 0 0 V 0 V V V 0 0 0 V V 0

- 40. V V V 0 0 V 0 V V V 0 0 0 V V 0

- 41. V V V 0 0 V 0 V V V 0 0 0 V V 0 Now, Lets the output of 16 – bit bus, is connected to an inverter

- 42. V V V 0 0 V 0 V V V 0 0 0 V V 0 Now, Lets the output of 16 – bit bus, is connected to an inverter 1110010111000110 16-bit bus 16-bit bus

- 43. V V V 0 0 V 0 V V V 0 0 0 V V 0 Now, Lets the output of 16 – bit bus, is connected to an inverter 1110010111000110 16-bit bus 16-bit bus 0001101000111001

- 44. V V V 0 0 V 0 V V V 0 0 0 V V 0 0001101000111001

- 45. V V V 0 0 V 0 V V V 0 0 0 V V 0 0001101000111001 What does this mean?

- 46. V V V 0 0 V 0 V V V 0 0 0 V V 0 0001101000111001 What does this mean? This means, all capacitors which were charged to ‘V’ volts will have to discharge to ‘0’ volts through single ‘Ground’ tap point. This will cause a bump in ‘Ground’ tap point.

- 47. V V V 0 0 V 0 V V V 0 0 0 V V 0 0001101000111001 What does this mean? This means, all capacitors which were charged to ‘V’ volts will have to discharge to ‘0’ volts through single ‘Ground’ tap point. This will cause a bump in ‘Ground’ tap point. V V V 0 0 V 0 V V V 0 0 0 V V 0

- 48. V V V 0 0 V 0 V V V 0 0 0 V V 0 0001101000111001 What does this mean? This means, all capacitors which were charged to ‘V’ volts will have to discharge to ‘0’ volts through single ‘Ground’ tap point. This will cause a bump in ‘Ground’ tap point. V V V 0 0 V 0 V V V 0 0 0 V V 0

- 49. V V V 0 0 V 0 V V V 0 0 0 V V 0 0001101000111001 What does this mean? This means, all capacitors which were charged to ‘V’ volts will have to discharge to ‘0’ volts through single ‘Ground’ tap point. This will cause a bump in ‘Ground’ tap point. V V V 0 0 V 0 V V V 0 0 0 V V 0 Ground Bounce

- 50. V V V 0 0 V 0 V V V 0 0 0 V V 0 0001101000111001 What does this mean?

- 51. V V V 0 0 V 0 V V V 0 0 0 V V 0 0001101000111001 What does this mean? Also, all capacitors which were ‘0’ volts will have to charge to ‘V’ volts through single ‘Vdd’ tap point. This will cause lowering of voltage at ‘Vdd’ tap point.

- 52. V V V 0 0 V 0 V V V 0 0 0 V V 0 0001101000111001 What does this mean? Also, all capacitors which were ‘0’ volts will have to charge to ‘V’ volts through single ‘Vdd’ tap point. This will cause lowering of voltage at ‘Vdd’ tap point. V V V 0 0 V 0 V V V 0 0 0 V V 0

- 53. V V V 0 0 V 0 V V V 0 0 0 V V 0 0001101000111001 What does this mean? Also, all capacitors which were ‘0’ volts will have to charge to ‘V’ volts through single ‘Vdd’ tap point. This will cause lowering of voltage at ‘Vdd’ tap point. V V V 0 0 V 0 V V V 0 0 0 V V 0

- 54. V V V 0 0 V 0 V V V 0 0 0 V V 0 0001101000111001 What does this mean? Also, all capacitors which were ‘0’ volts will have to charge to ‘V’ volts through single ‘Vdd’ tap point. This will cause lowering of voltage at ‘Vdd’ tap point. Voltage Droop V V V 0 0 V 0 V V V 0 0 0 V V 0

- 55. So what could be the solution ?

- 56. So what could be the solution ? Driver Load

- 57. So what could be the solution ? Driver Load How can ‘Driver’ and ‘Load’ can be brought close to each other in ‘L’ sense ?

- 58. If ‘Driver’ and ‘Load’ have a lot of communication between them, then the power supply network must be designed in such a way, that they are Inductively close to each other

- 59. If ‘Driver’ and ‘Load’ have a lot of communication between them, then the power supply network must be designed in such a way, that they are Inductively close to each other So, how do we design power supply distribution network?

- 60. If ‘Driver’ and ‘Load’ have a lot of communication between them, then the power supply network must be designed in such a way, that they are Inductively close to each other So, how do we design power supply distribution network? MESH!!!!

- 62. Vdd Vss Vdd Vss Vdd Vss Vss Vss Vdd Vdd Vss Vss Vdd Vdd Vss Vss Vdd Vdd Vdd Vss Vdd Vss Vdd Vss

- 63. Vdd Vss Vdd Vss Vdd Vss Vss Vss Vdd Vdd Vss Vss Vdd Vdd Vss Vss Vdd Vdd Vdd Vss Vdd Vss Vdd Vss

- 64. Vdd Vss Vdd Vss Vdd Vss Vss Vss Vdd Vdd Vss Vss Vdd Vdd Vss Vss Vdd Vdd Vdd Vss Vdd Vss Vdd Vss

- 65. Power should not be coming only from one place

- 66. Power should not be coming only from one place But from many places

- 67. Power should not be coming only from one place But from many places Assume that, the boundary power is available, now we have to get it inside the chip

- 68. Power should not be coming only from one place But from many places Assume that, the boundary power is available, now we have to get it inside the chip Thus, local communication is taken care by de-coupling capacitors

- 69. Power should not be coming only from one place But from many places Assume that, the boundary power is available, now we have to get it inside the chip Thus, local communication is taken care by de-coupling capacitors And, common rail inductance coupling issue is taken care by power mesh

- 70. DECAP1 D Block a Block b 4 DECAP2 Block c DECAP3 Die Vss Core Vdd