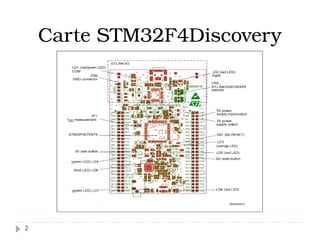

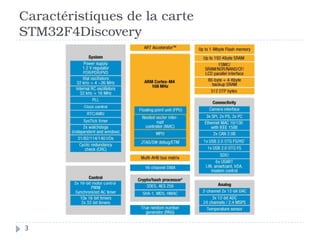

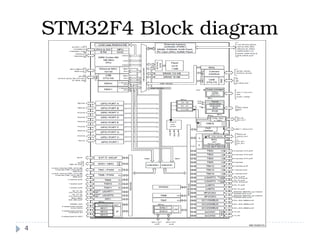

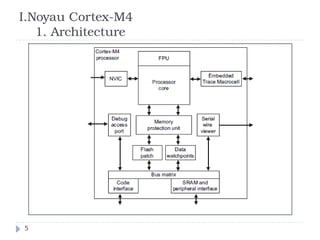

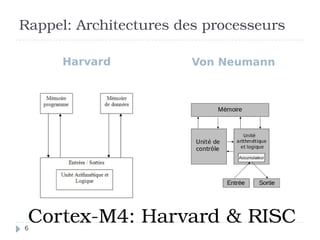

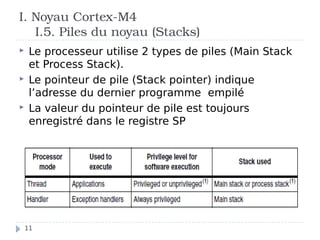

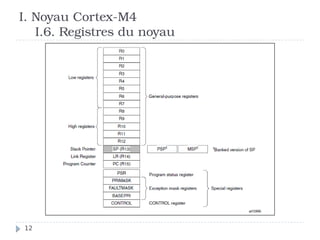

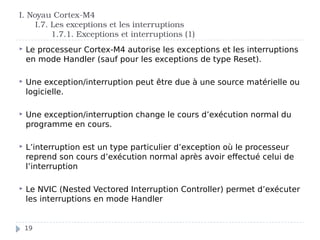

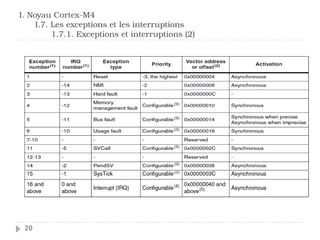

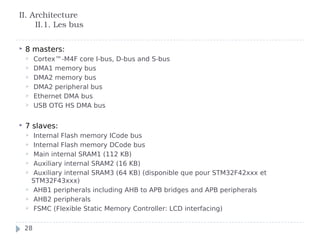

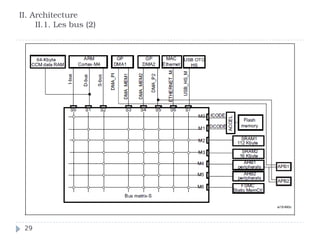

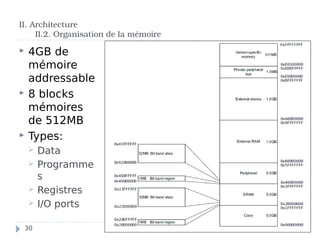

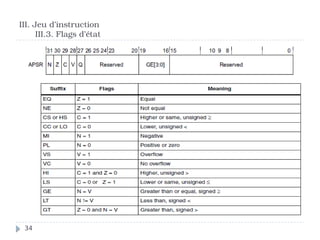

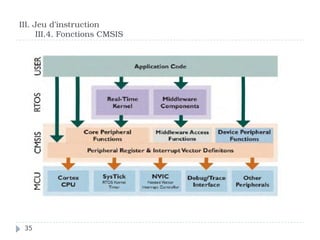

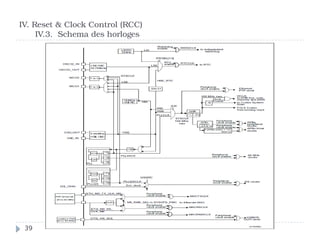

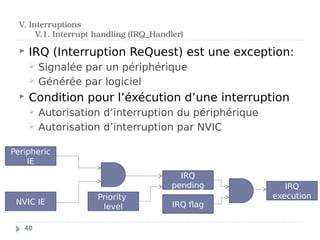

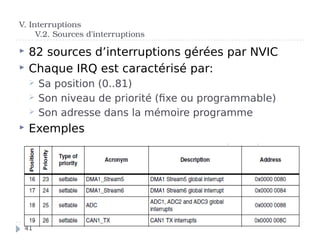

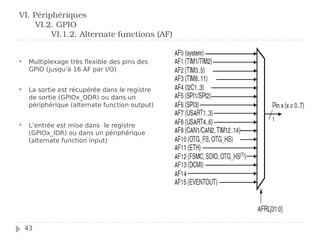

Le document fournit un tutoriel détaillé sur la carte STM32F4, y compris ses caractéristiques, l'architecture du noyau Cortex-M4, et les divers périphériques associés. Il aborde des aspects essentiels tels que les modes de traitement, la gestion des exceptions et des interruptions, ainsi que la bibliothèque CMSIS pour faciliter le développement. Les détails techniques incluent les unités de protection de la mémoire, les horloges système et la gestion des GPIO.