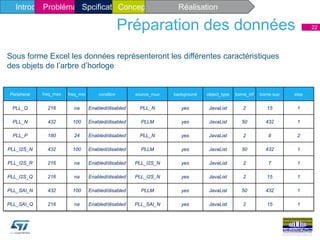

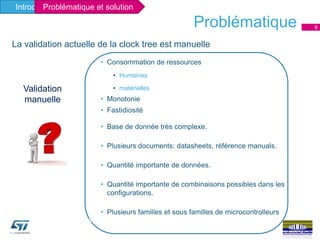

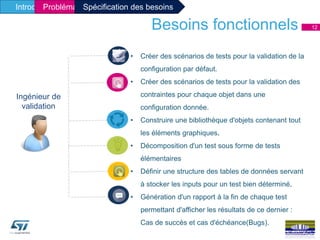

Le document présente un projet de fin d'études axé sur l'automatisation des tests de validation pour le module de configuration d'horloge de l'outil STM32CubeMX. L'objectif principal est d'améliorer la validation actuelle, qui est manuelle, en mettant en place une suite de tests automatiques pour assurer rapidité, précision et fiabilité. Les perspectives incluent l'augmentation de la couverture des tests par l'automatisation de la validation du code généré et des paramètres électriques.

![18

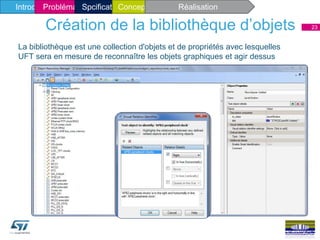

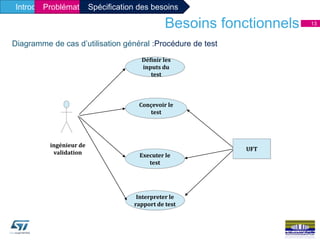

Clock TreeHP UFT

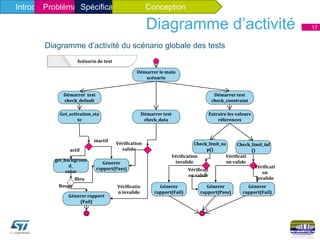

Ingénieur validation

Saisir le bloc à tester

Bloc saisi

Démarrer le test

Test démarré

Sélectionner

composant du bloc

Composant du bloc

selectionné

Loop

[List des

composant du

bloc n'est pas

terminée]

Diagramme Check_constraint

Excel

Check_limit_sup() Extraire les valeurs

réferencesValeurs

extraites

vérification

Vérification terminée

Génerer rapport ()

check_limit_inf()

Extraire les valeurs

réferences

Valeurs extraites

Vérification terminée

vérificationGénerer le rapport()

alt

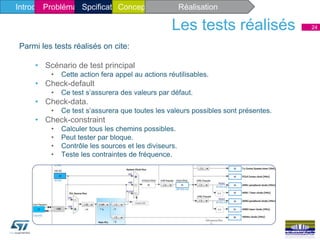

Diagramme de séquence du test: conformité aux contraintes

Diagramme de séquence

Introduction généraleProblématique et solutionIntroduction généraleProblématique et solutionProblématique et solutionIntroduction généraleProblématique et solutionSpécificattique et solutionConception](https://image.slidesharecdn.com/d747742e-598c-4e9d-ab5a-ed5f0a15d531-160907162706/85/Final-18-320.jpg)