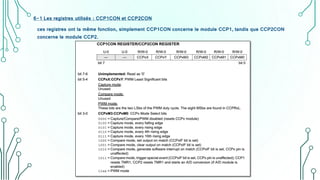

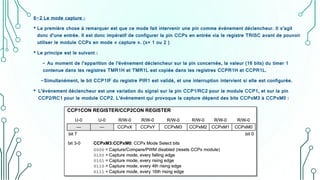

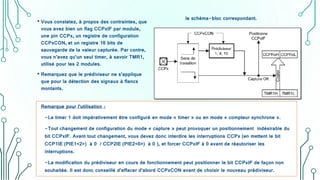

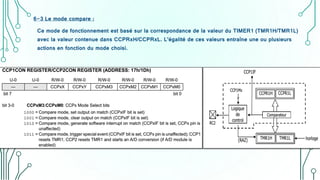

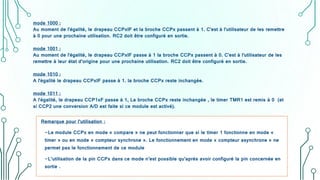

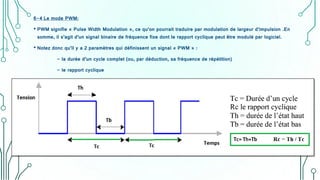

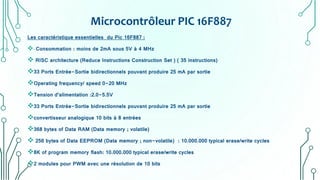

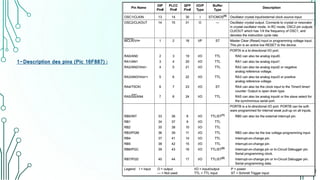

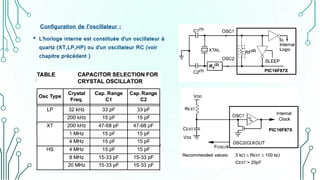

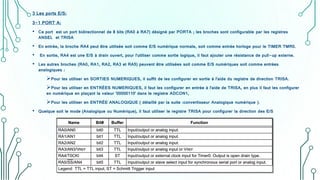

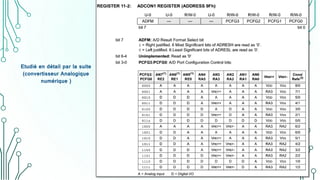

Le document présente une introduction au microcontrôleur PIC 16F887, détaillant ses caractéristiques techniques, notamment sa consommation, son architecture RISC, et ses ports d'entrée/sortie. Il aborde également la programmation des microcontrôleurs, les interruptions, ainsi que les timers et modules intégrés pour le traitement des signaux. Enfin, le document explique le fonctionnement d'un convertisseur analogique-numérique et des modules CCP pour la capture, la comparaison et le PWM.

![Les valeurs représentées

Ne restent plus que les formules qui nous donnent les relations entre valeurs analogiques et représentations

numériques.

Nous pouvons dire que pour une numérisation sur 10 bits, on obtiendra la valeur numérique :

Val = [(VIN - VREF-) / (VREF+ - VREF-)] * 1023

VIN = ((Val/1023) * (VREF+ - VREF-)) + VREF

avec :

VREF- : tension minimale analogique (référence négative)

VREF+ : tension maximale analogique (référence positive)

VIN : tension d’entrée à numériser

Val : valeur numérique obtenue sur 10 bits](https://image.slidesharecdn.com/microcontroleurpicpart2-160922001548/85/Microcontroleur-PIC-Microchip-part2-2-35-320.jpg)