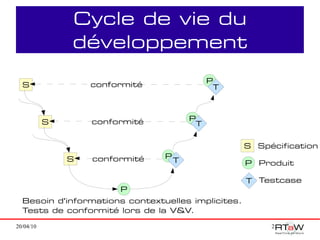

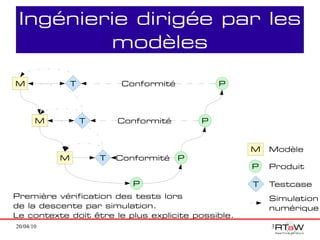

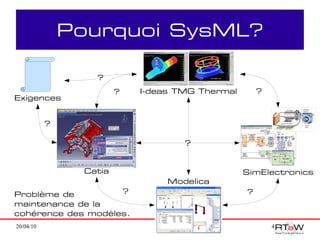

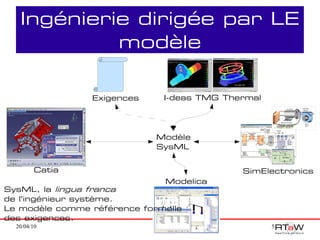

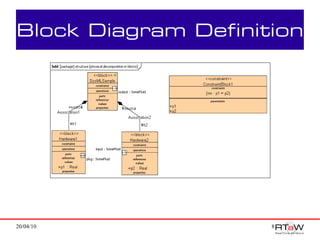

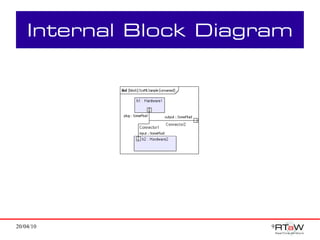

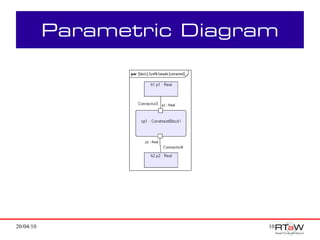

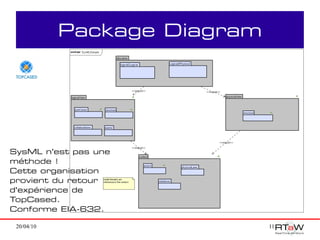

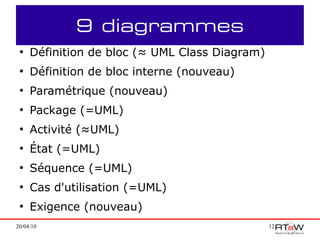

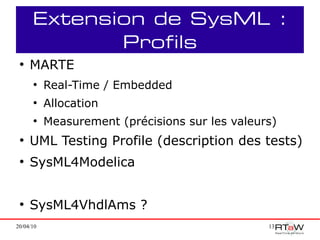

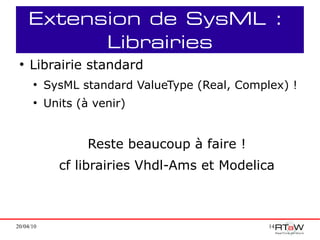

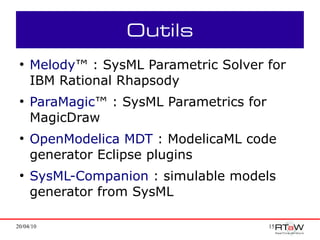

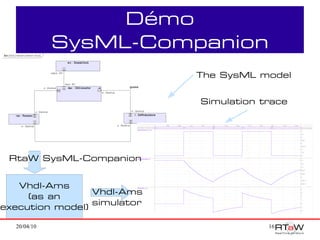

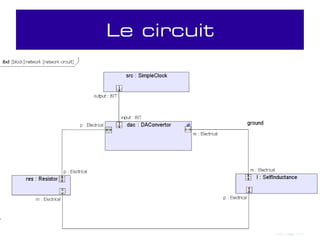

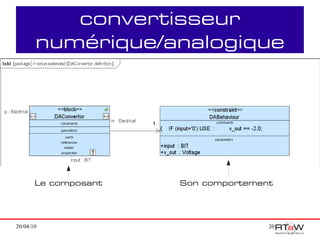

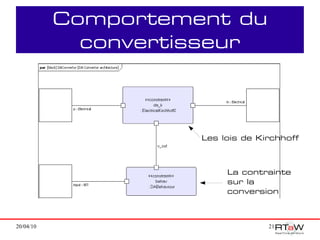

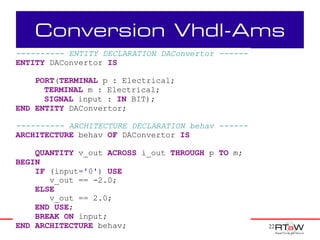

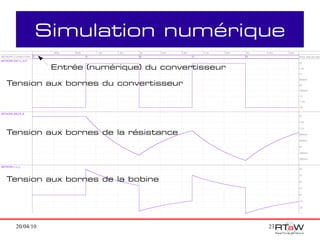

Le document aborde le prototypage virtuel en utilisant SYSML, en soulignant les avantages de l'ingénierie dirigée par les modèles, comme une meilleure maturité de la conception et un time-to-market réduit. Il explique que SYSML, une simplification de l'UML pour les ingénieurs système, est un cadre formel normalisé pour la gestion des exigences et la simulation. Il présente également des outils et extensions pour SYSML, ainsi que des exemples d'utilisation dans la conception de circuits électroniques.