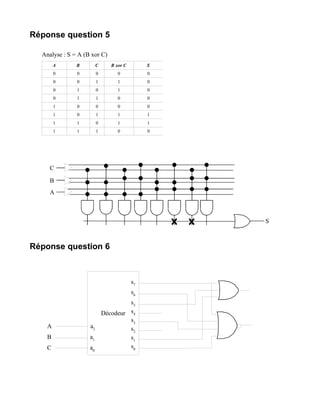

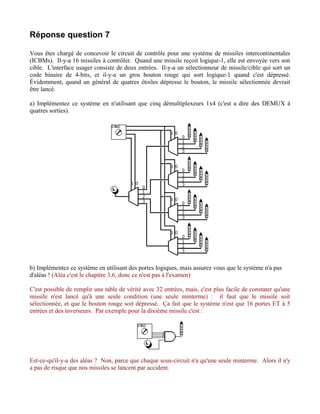

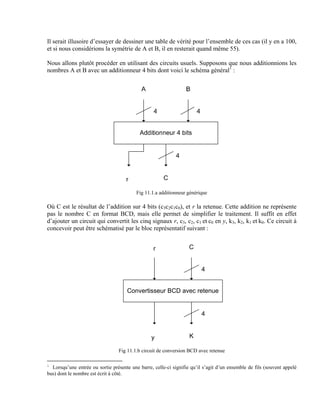

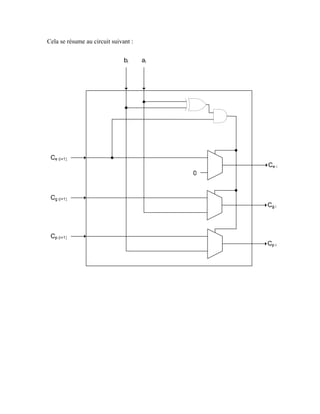

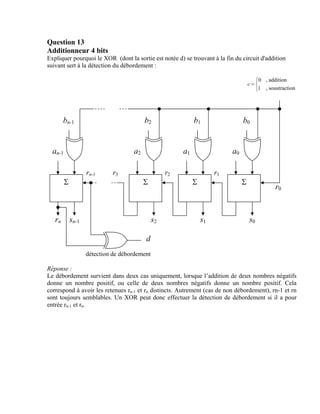

Le document contient des réponses à une série de questions sur la conception de circuits logiques, abordant des sujets tels que les portes logiques, les multiplexeurs, et les décodeurs. Il décrit également la création de systèmes de contrôle pour des missiles intercontinentaux, des additionneurs BCD, ainsi que des méthodes de simplification de circuits logiques. Enfin, des équations et des schémas sont présentés pour illustrer les principes discutés.

![Réponse question 1

A[3..0] B[3..0]

b a 1

= 0 1

E4 E0

G4 Comp. Comp. Comp. Comp. G0

P4 1-bit 1-bit 1-bit 1-bit P0

0 1 0 1 0 1 0 1

0 1 0 1 0 1 0 1

S0 S1 S2 S3

Réponse question 2

Pour obtenir l'équivalent d'une porte logique avec un multiplexeur, il suffit d'utiliser la méthode de

table de Karnaug à table inscrite et d'inscrire une des deux entrées :

OU ET

XOR

0 1 A B S S (B A B S S (B

1 XOR inscrit) inscrit)

0

1 1

0 0 0 0 B 0 0 0 0

a 0 0

1 1 s 0 1 1 0 1 0

b 0

1 0 1 1 1 0 0 B

ri-1

1 1 1 1 1 1

1

0 0 OU

1 1 r

ET 0 XOR

ET Pour réaliser le XOR,

A B S S (B

1 inscrit) puisqu'une valeur

0 0 0 0 0 B inscrite est inversée, il

0 1 1 faut également utiliser

1 0 1 B' un multiplexeur pour

créer un inverseur

1 1 0](https://image.slidesharecdn.com/td02corrige-120312183057-phpapp02/75/Td02-corrige-1-2048.jpg)

![Réponse question 3

A[3..0] B[3..0]

b a

E4 E0

G4 Comp. Comp. Comp. Comp. G0

P4 1-bit 1-bit 1-bit 1-bit P0

r4 Σ Σ Σ Σ r0

1-bit 1-bit 1-bit 1-bit

S3 S2 S1 S0

Réponse question 4

SD1 e3

e3

s1

s1

SD2 e2

e2 Encodeur 3

s0

s0 2 O[1]

e1 Priorité 1

SD3 e1

0 0

0 e0

e0

S1[1]

S1[0] 3

2 O[0]

S2[1] 1

0 0

S2[0]

S3[1] Partie b)

S3[0] s3 A1

e1 s2 A2

Demux

s1 A3

e0

s0](https://image.slidesharecdn.com/td02corrige-120312183057-phpapp02/85/Td02-corrige-2-320.jpg)