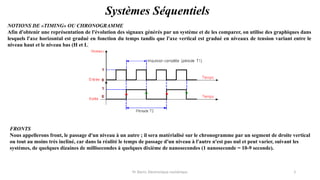

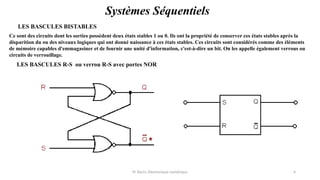

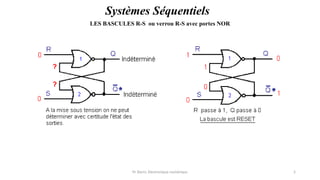

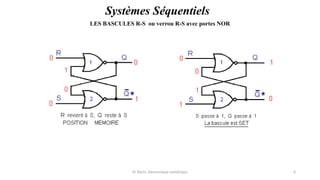

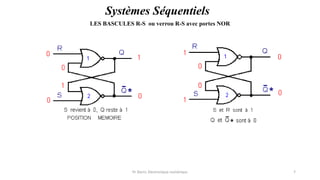

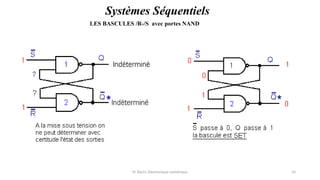

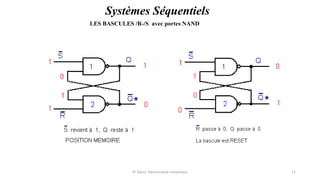

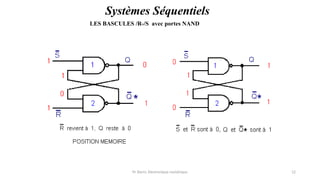

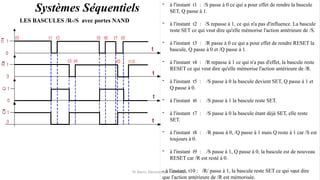

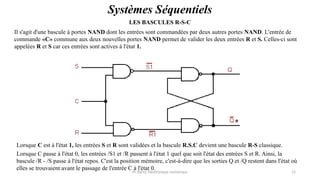

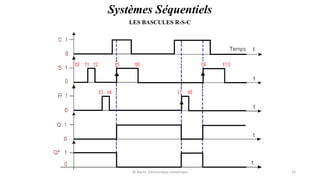

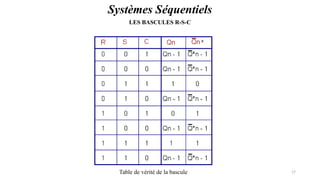

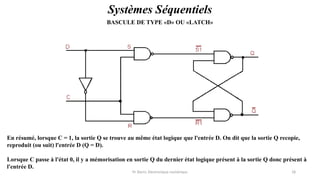

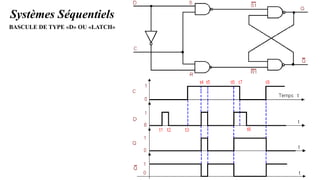

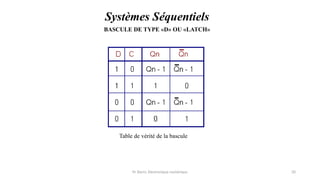

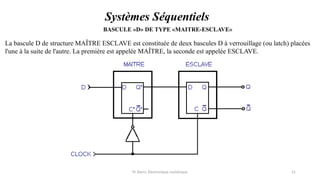

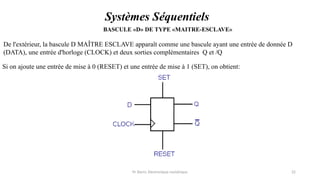

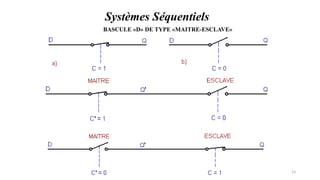

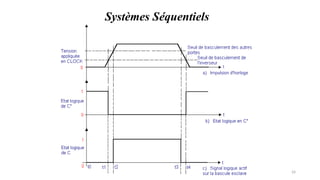

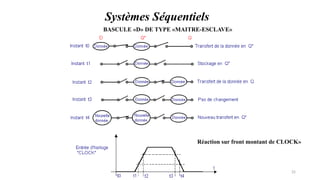

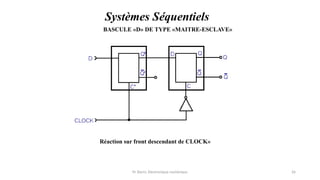

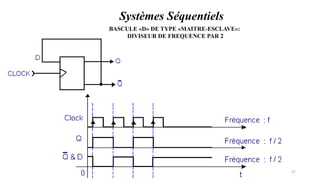

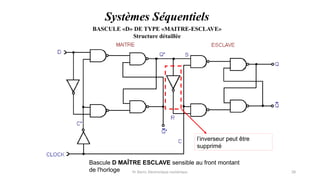

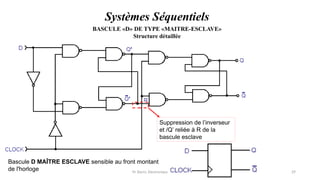

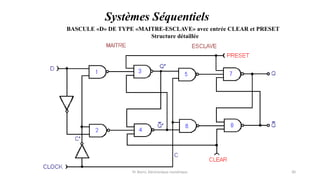

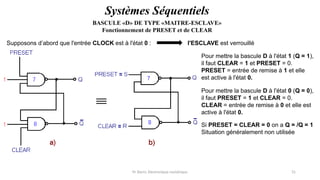

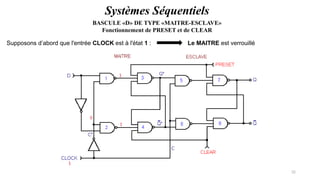

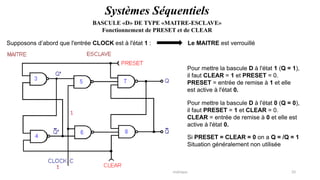

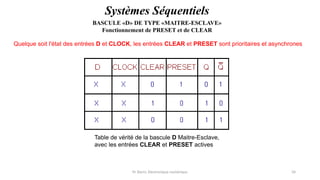

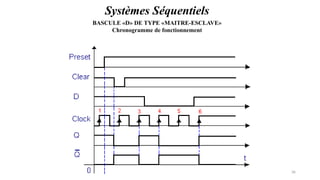

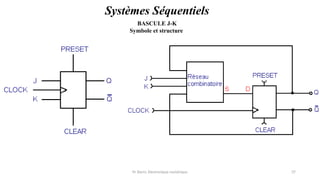

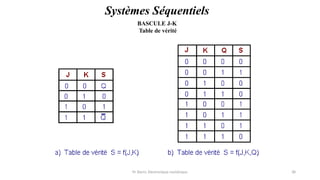

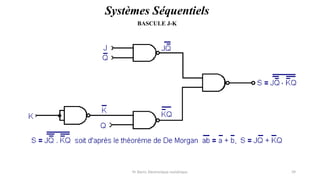

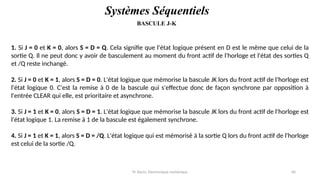

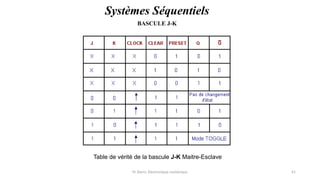

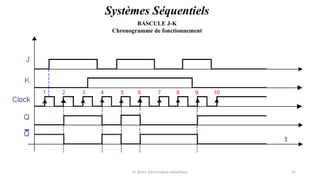

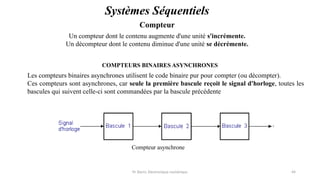

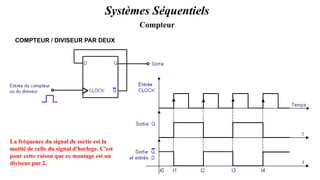

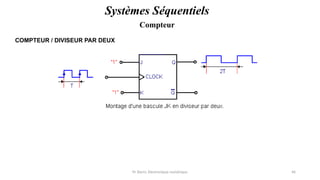

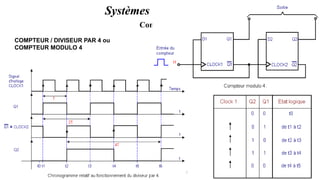

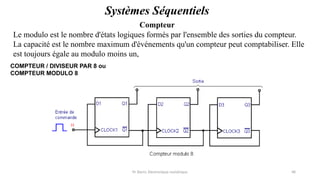

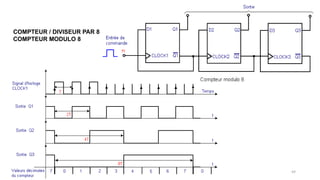

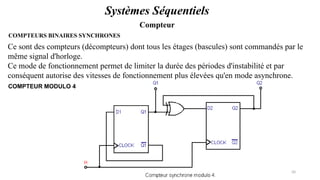

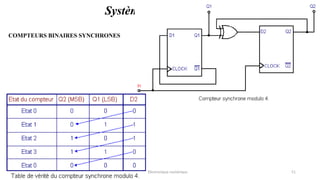

Ce document présente les systèmes séquentiels en électronique numérique, en expliquant la distinction entre circuits combinatoires et séquentiels. Il détaille les différents types de bascules, telles que les bascules R-S et D, ainsi que leur fonctionnement et leurs tables de vérité. Le texte aborde également les compteurs, y compris les compteurs asynchrones et synchrones, et leur rôle dans la comptabilisation des événements.