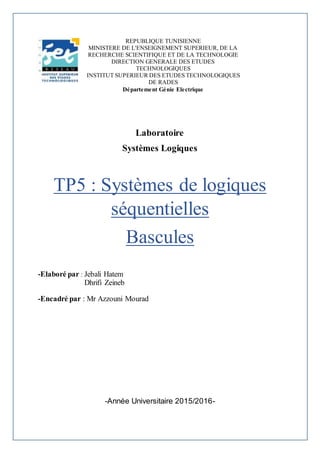

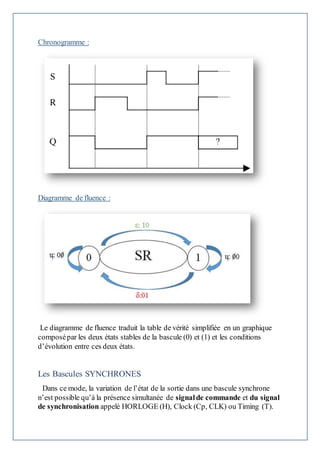

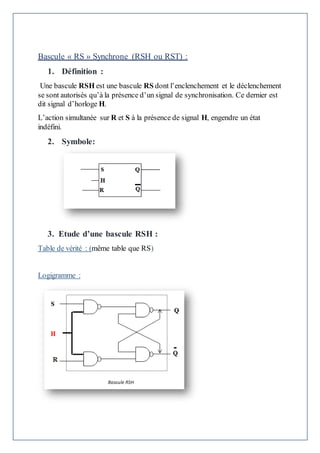

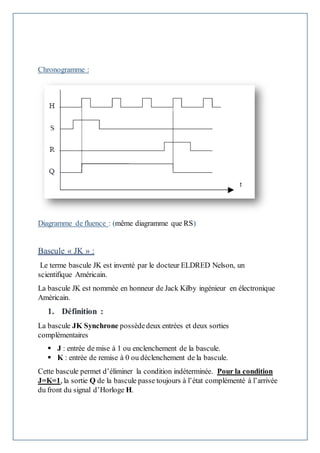

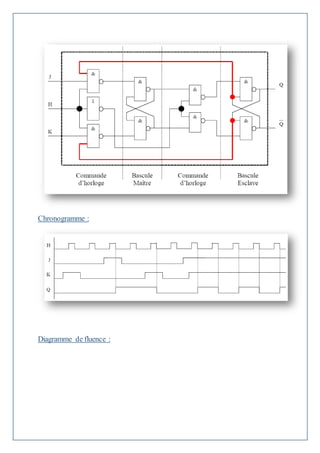

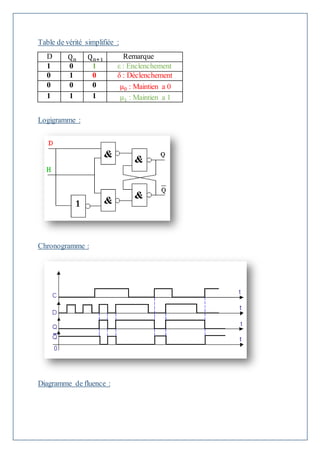

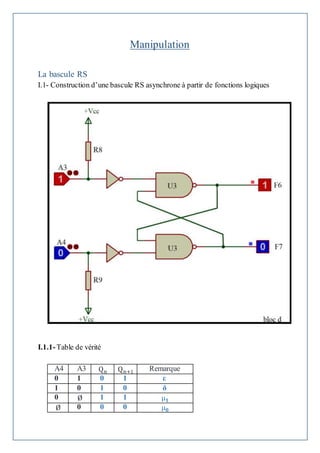

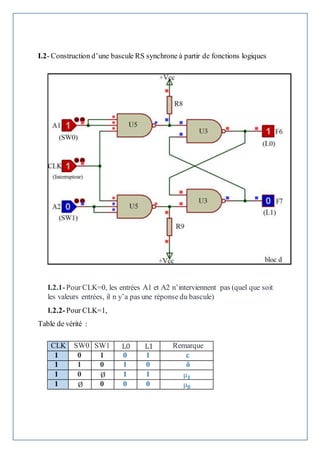

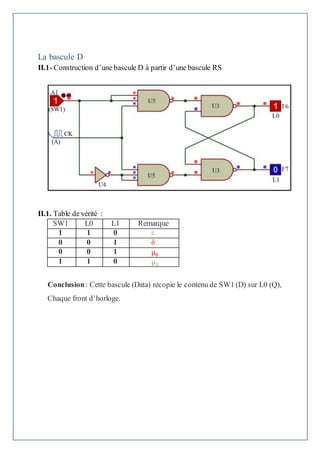

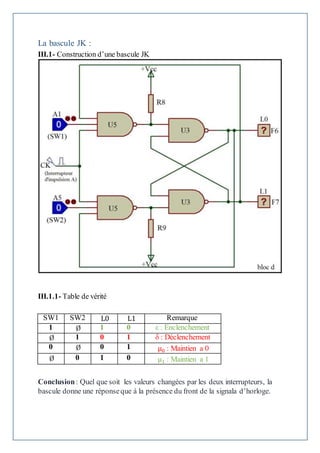

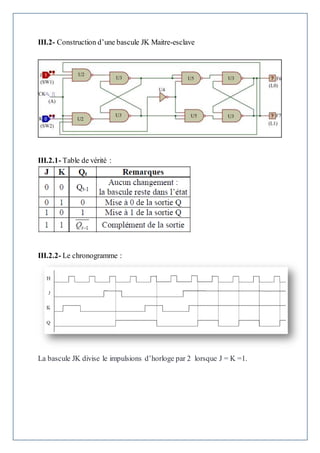

Le document est un rapport technique sur les systèmes logiques séquentiels, en particulier les bascules (RS, D, JK, T) et leurs constructions ainsi que leurs tables de vérité. Il fournit des définitions, des constructions pratiques, et des manipulations liées à ces circuits logiques dans le cadre de l'éducation supérieure en Tunisie. En outre, il aborde les compteurs binaires et leur fonctionnement basé sur les bascules utilisées.