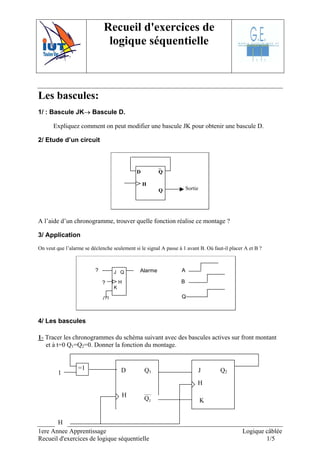

Le document est un recueil d'exercices de logique séquentielle, notamment sur les bascules et les compteurs. Il aborde divers circuits et montages, y compris des compteurs asynchrones et synchrones, des circuits de division de fréquence, ainsi que des registres et des systèmes de sérialisation/désérialisation. Chaque exercice présente des problèmes pratiques à résoudre, liés à la conception et la synthèse de circuits logiques.