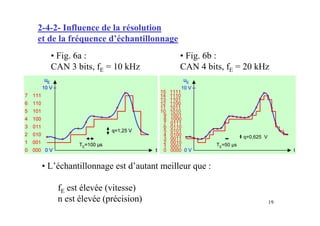

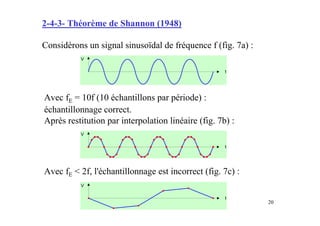

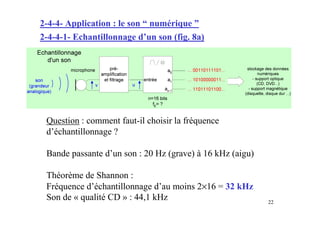

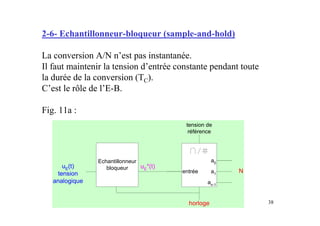

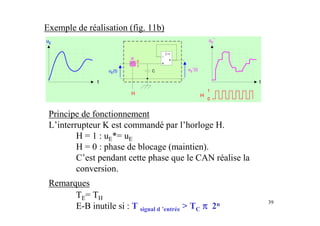

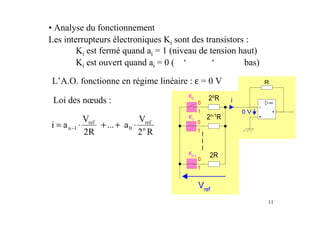

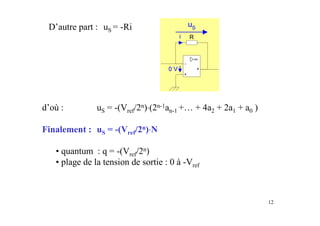

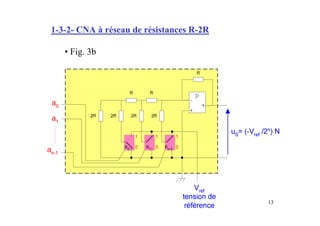

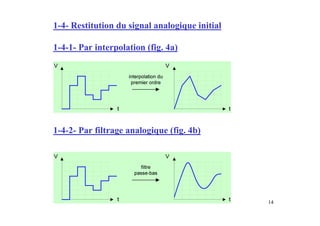

Ce document présente les convertisseurs analogique-numérique (CAN) et numérique-analogique (CNA), expliquant leur fonctionnement et leurs caractéristiques essentielles. Il aborde les types de CAN et CNA, la numérisation des signaux et les concepts associés à l'échantillonnage, notamment le théorème de Shannon. Des exemples pratiques illustrent les types de circuits et leurs applications dans des systèmes électroniques.

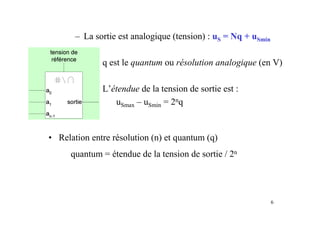

![• Exemple n°1 (fig. 2a) : CNA 3 bits, plage [0,10 V]

q = (10 - 0)/ 23 = 10/8 = 1,25 V

N a2 a1 a0 uS (V)

0 0 0 0 0

1 0 0 1 1,25

2 0 1 0 2,5

3 0 1 1 3,75

4 1 0 0 5

5 1 0 1 6,25

6 1 1 0 7,5

7 1 1 1 8,75

8](https://image.slidesharecdn.com/courselectroniqueconversiondedonnees-120228054214-phpapp02/85/Cours-electronique-conversion-de-donnees-8-320.jpg)

![• Exemple n°2 (fig. 2b) : CNA 8 bits, plage [-5,+5 V]

q = (5 - (-5))/ 28 = 10/256 ≈ 0,04 V

N a7 a6 a5 a4 a3 a2 a1 a0 uS (V)

0 0 0 0 0 0 0 0 0 -5

1 0 0 0 0 0 0 0 1 -4,96

2 0 0 0 0 0 0 1 0 -4,92

128 1 0 0 0 0 0 0 0 0

254 1 1 1 1 1 1 1 0 +4,92

255 1 1 1 1 1 1 1 1 +4,96

9](https://image.slidesharecdn.com/courselectroniqueconversiondedonnees-120228054214-phpapp02/85/Cours-electronique-conversion-de-donnees-9-320.jpg)

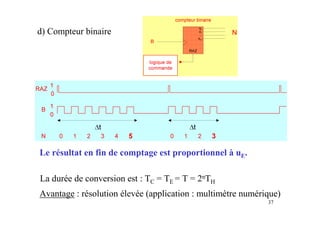

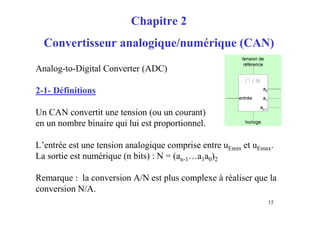

![2-2- Fonction de transfert

• N = [(uE – uEmin) /quantum]

[les crochets désignent la partie entière]

• Exemple (fig. 5) : CAN 3 bits, plage [0,10 V]

16](https://image.slidesharecdn.com/courselectroniqueconversiondedonnees-120228054214-phpapp02/85/Cours-electronique-conversion-de-donnees-16-320.jpg)