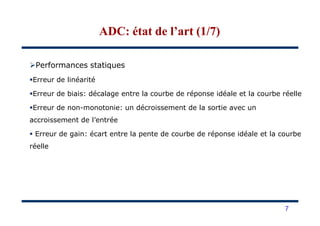

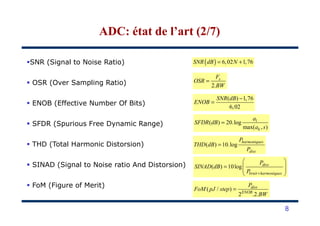

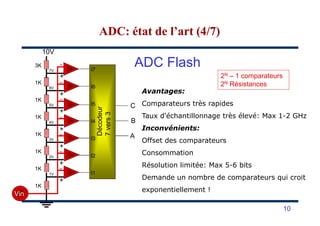

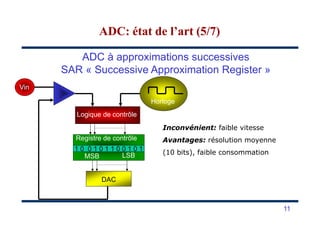

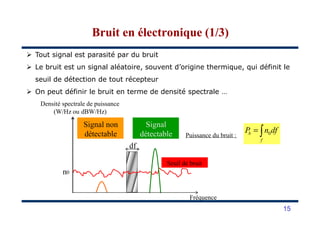

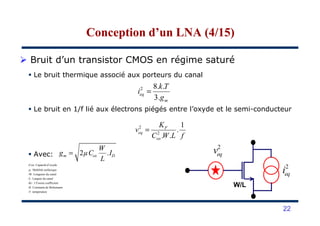

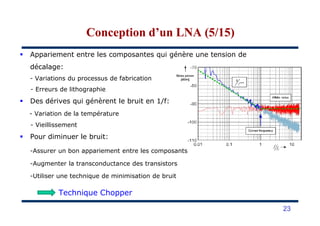

Le document traite de la modélisation et de la conception d'interfaces pour des systèmes de communication à faible consommation, notamment à travers le développement de circuits adaptatifs. Il aborde les défis de détection de signaux faibles et de la conception d'amplificateurs à faible bruit et consommation. Le document présente également des détails techniques sur l'architecture des circuits, les performances des ADC et les sources de bruit en électronique.

![Introduction (1/3)Introduction (1/3)

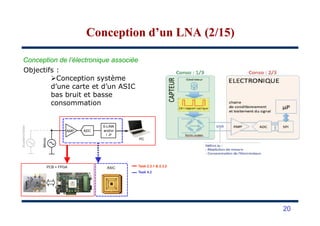

Architecture physique de la radio intelligente

Trois étages:

Etage radiofréquence (RF)

Etage de conversion ADC/DAC

Etage de traitement en bande de base

3[Akyildiz, Computer Networks Elsevier 2006]](https://image.slidesharecdn.com/2014-04-10nebhen-160417231216/85/2014-04-10-nebhen-4-320.jpg)

![Les ADC sont des circuits principaux dans les systèmes de communication

modernes:

• de 80 à 90 dB de SNR

• plus de 90dB de SFDR

• 10-100 MHz de bande passante

ADC: état de l’art (3/7)ADC: état de l’art (3/7)

• 10-100 MHz de bande passante

• 0,5 pJ par étape de conversion

Par exemple: ADC 16 bits, 2,2 GHz: puissance de 1 à 10 W

Consommation d'énergie très élevée!

9[Linear Technology, LTC2217]](https://image.slidesharecdn.com/2014-04-10nebhen-160417231216/85/2014-04-10-nebhen-10-320.jpg)

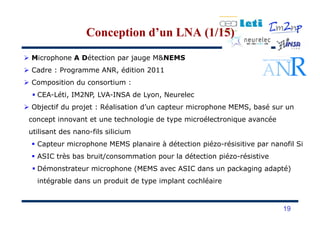

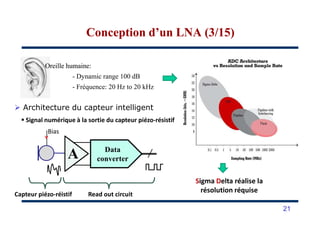

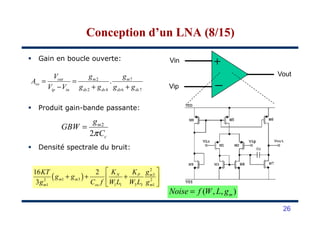

![Conception d’un LNA (6/15)Conception d’un LNA (6/15)

La technique Chopper est bien adaptée pour le traitement des signaux

qui sont continus dans le temps

Eliminer le bruit en 1/f et la tension de décalage

Réduire la distorsion harmonique d’intermodulation de deuxième ordre

du modulateur

Le signal est transposé, amplifié, ramené en bande de base et filtré

Le signal existe d’une façon continue

24[C. C. Enz, Proceedings of the IEEE 1996]](https://image.slidesharecdn.com/2014-04-10nebhen-160417231216/85/2014-04-10-nebhen-25-320.jpg)

![Conception d’un LNA (7/15)Conception d’un LNA (7/15)

Circuit de préamplificateur + polarisation

[Nebhen, DTIS 2013] 25

CT-ΣΔM

R1=R2=R3=R4=4KΩ

M&NEMS sensor](https://image.slidesharecdn.com/2014-04-10nebhen-160417231216/85/2014-04-10-nebhen-26-320.jpg)

![Courbes de Gain et de Phase Bruit de l’AI

Conception d’un LNA (9/15)Conception d’un LNA (9/15)

Gain=62 dB et Phase=70° HzBruit=6 nV/

[Nebhen, DTIS 2013] 27](https://image.slidesharecdn.com/2014-04-10nebhen-160417231216/85/2014-04-10-nebhen-28-320.jpg)

![Circuit de l’ADC Sigma-Delta:

Sensor

input

Sampling

clock

Output

Conception d’un LNA (10/15)Conception d’un LNA (10/15)

FIR

Decimator

filter

input

Output

Implementation technology

• CMOS 65 nm

• 2.5 V Supply

28

FIR

[Nebhen, IEEE Sensos 2013]](https://image.slidesharecdn.com/2014-04-10nebhen-160417231216/85/2014-04-10-nebhen-29-320.jpg)

![Conception d’un LNA (11/15)Conception d’un LNA (11/15)

OTA-Miller totalement differentiel + circuit de contre réaction (CMFB)

Courbes de Gain et de Phase

+

+

−

−

29[Nebhen, DTIP 2014]

Gain=70 dB Phase=63°](https://image.slidesharecdn.com/2014-04-10nebhen-160417231216/85/2014-04-10-nebhen-30-320.jpg)

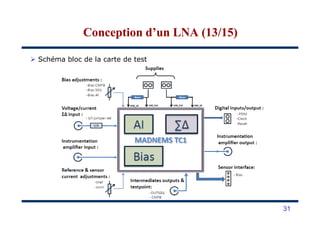

![Conception d’un ASIC faible bruit et faible tension d'alimentation en technologie

CMOS ST 65nm

Simulation niveau système: VHDL® et MATLAB®

Simulation niveau transistor sous le logiciel CADENCE® VIRTUOSO®

Dessin des masques de l’ASIC

Conception d’un LNA (12/15)Conception d’un LNA (12/15)

Dessin des masques de l’ASIC

30[Nebhen, DTIP 2014] [Nebhen, ICECS 2013]

[Nebhen, IEEE SENSORS 2013]

Technology: CMOS 65 nm

Alimentation: VDD = 2.5 V

Area: 1mm x 1mm

Package: TQFP64](https://image.slidesharecdn.com/2014-04-10nebhen-160417231216/85/2014-04-10-nebhen-31-320.jpg)

![Bruit de l’ADC Bruit de l’amplificateur

Conception d’un LNA (14/15)Conception d’un LNA (14/15)

SNR = 92.5 dB

Résolution > 15 bits Hz

Bruit de l’amplificateur

• PSD = 8 nV/

[Nebhen, IEEE SENSORS 2013] 32](https://image.slidesharecdn.com/2014-04-10nebhen-160417231216/85/2014-04-10-nebhen-33-320.jpg)

![Ce travail 1 2 3 4

Process

(nm)

ST 65 65 65 65 65

Supply (V) 2.5 1.2 0.9 0.5 1

fs (MHz) 3.072 12 0.25 0.5 3.072

BW

20Hz- 20Hz-

500Hz 500Hz 24kHz

Mesure de SNR et de SNDR Comparaison avec l’état de l’art

Conception d’un LNA (15/15)Conception d’un LNA (15/15)

BW

20Hz-

20kHz

20Hz-

2kHz

500Hz 500Hz 24kHz

SNR (dB) 92.5 77 80 75 88

SNDR (dB) 91 74 76 65 92

DR (dB) 93.5 95 68 72 93

THD (dB) 83 82 80 - -

OSR 120 300 250 500 64

Power

(mW)

0.3 2.2 2.1 0.25 0.25

1- [Dorrer, ESSCIRC 2006]

2- [Yeknami, IEEE Transaction Cir. Syst 2013]

3- [Liu, VLSI Design 2013]

4- [Luo, IEEE JSSC 2013]

[Nebhen, IEEE SENSORS 2013]

SNR = 92.5 dB

SNDR = 91 dB

DR = 93.5 dB

33](https://image.slidesharecdn.com/2014-04-10nebhen-160417231216/85/2014-04-10-nebhen-34-320.jpg)