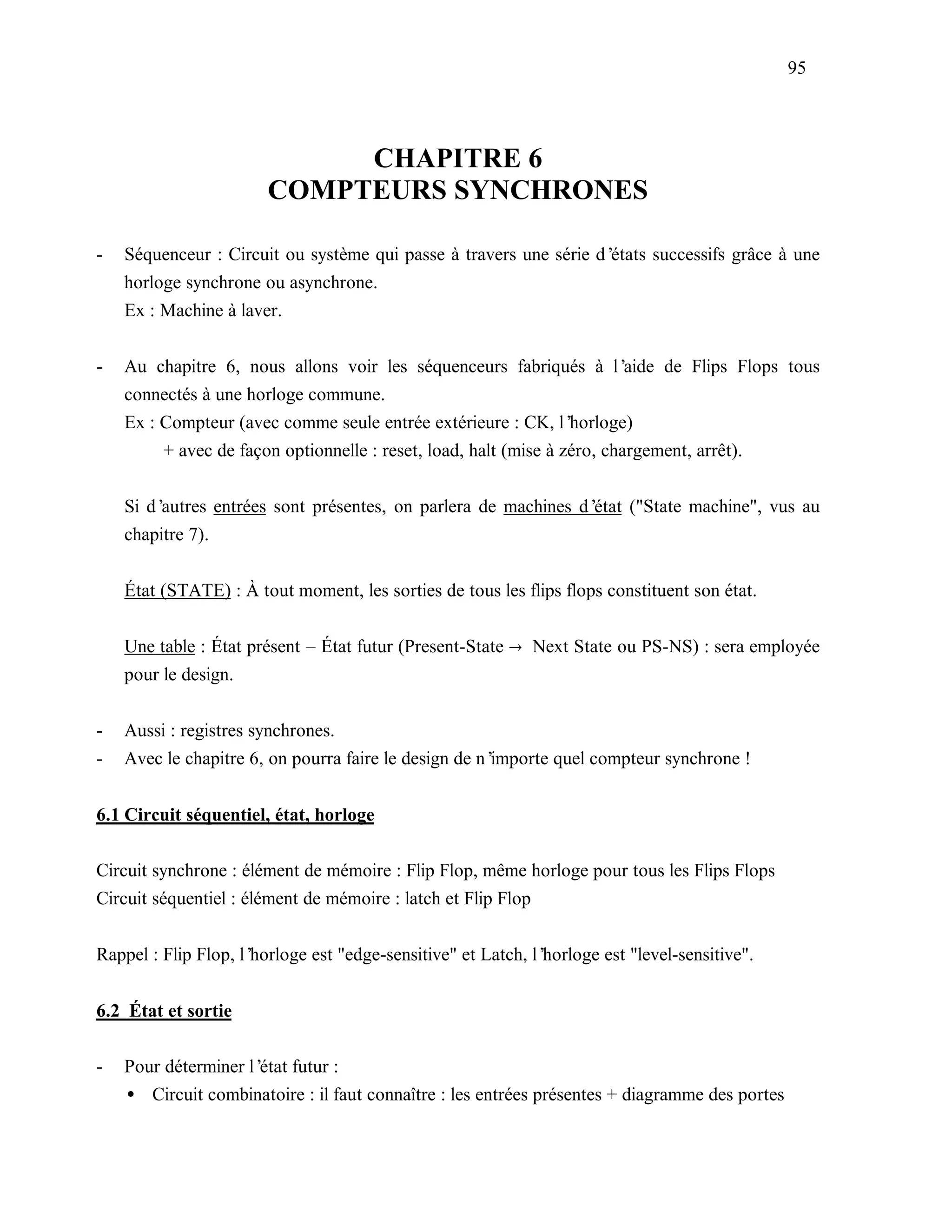

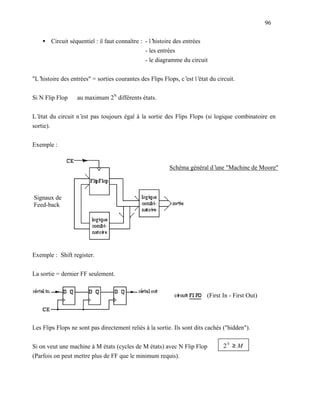

Le chapitre 6 aborde la conception de compteurs synchrones et séquenceurs utilisant des flips flops synchronisés à une horloge, expliquant les concepts de circuits séquentiels et combinatoires ainsi que les méthodes de design associées. Plusieurs types de compteurs, tels que les compteurs à décade et les registres à décalage, sont présentés, en expliquant la manière de minimiser et d'optimiser les états. Les étapes d'analyse et de design, ainsi que des considérations pratiques sur la fréquence d'horloge et les états des circuits, sont détaillées pour guider la réalisation de circuits efficaces.

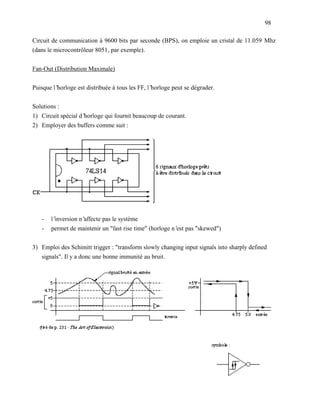

![107

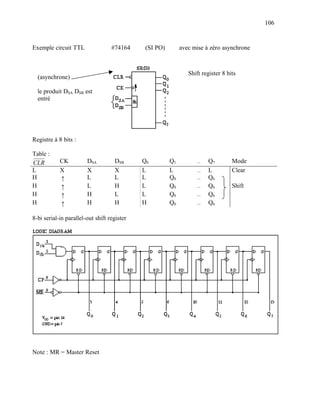

FUNCTION TABLE

INPUTS OUTPUTS

OPERATING MODE

MR CP Dsa Dsb Q0 Q1… . Q7

L X X X L L L Reset (clear)

H ↑ l l L q0 q6

H ↑ l h L q0 q6

Shift

H ↑ h l L q0 q6

H ↑ h h H q0 q6

H = High voltage level

h = High voltage level one set-up time prior to the Low-to-High clock transition

L = Low voltage level

l = Low voltage level one set-up time prior to the Low-to-High clock transition

Qn = Lower case letters indicate the state of the referenced input (or output) on setup time prior to the Low-to-

High

clock transition

X = Don’ care

t

↑ = Low-to-High clock transition

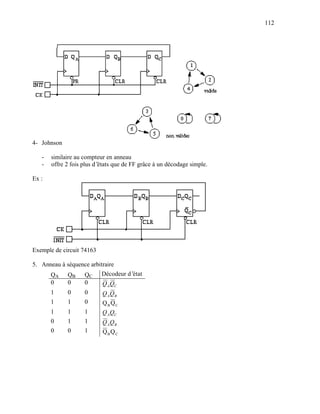

6.11 Analyse des Registres SR Cycliques [CSR] cyclic Shift Register

On décode comme ceci : Qi → Qi + 1, i = 0, … N –1 N = Nb de bits

Qo = f(Qi, i = 0, … N) ≤ fonction booléenne

( )

Après un certain nb de cycles, ≤2 N la séquence recommence

- Pour déterminer la séquence : - simulation

- la faire à la maison

Ex : CSR](https://image.slidesharecdn.com/compteursynchrone-130410134100-phpapp02/85/Compteur-synchrone-13-320.jpg)