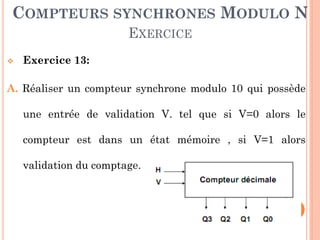

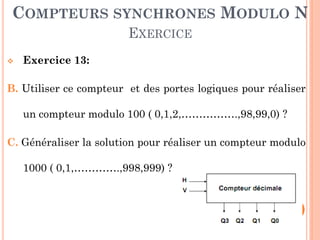

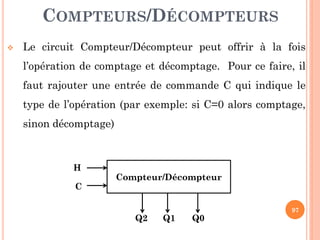

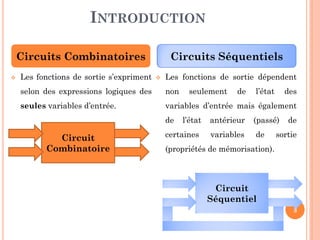

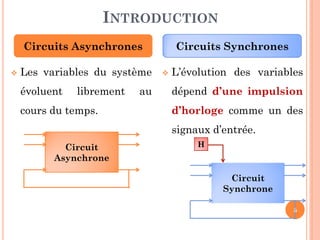

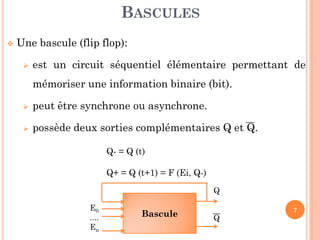

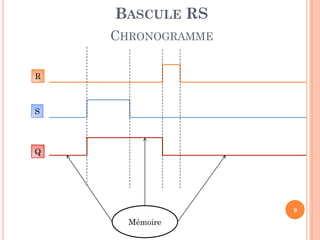

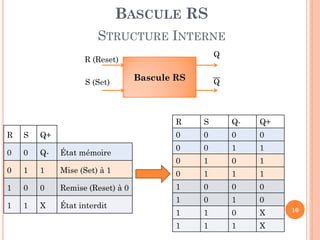

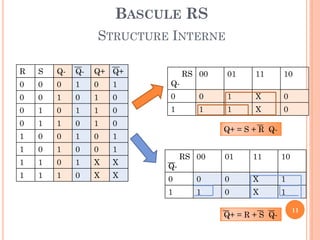

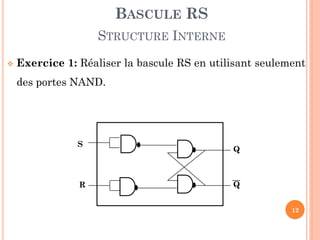

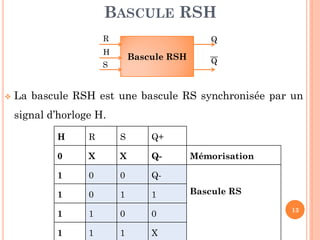

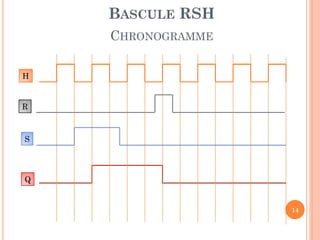

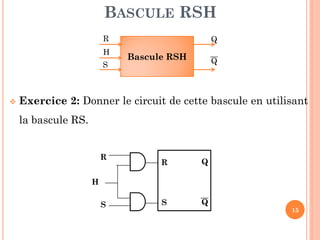

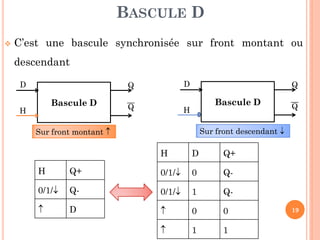

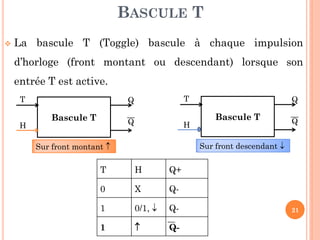

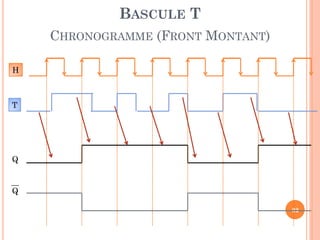

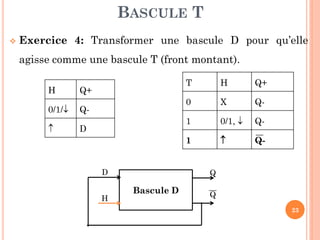

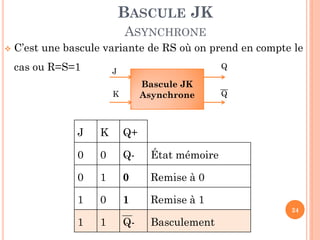

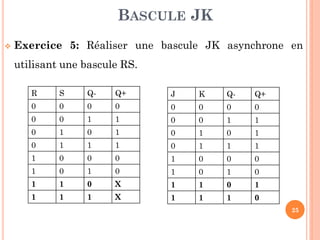

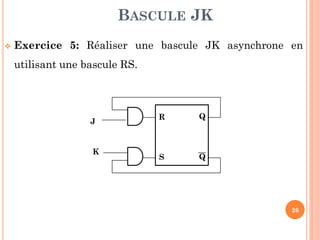

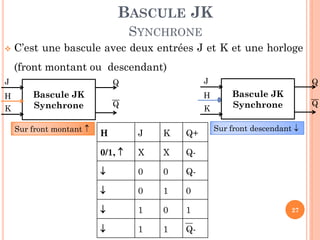

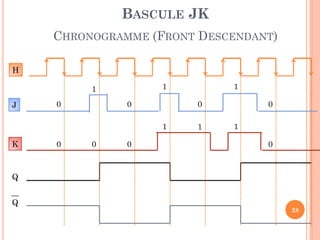

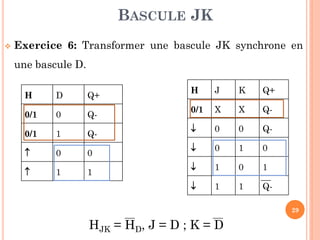

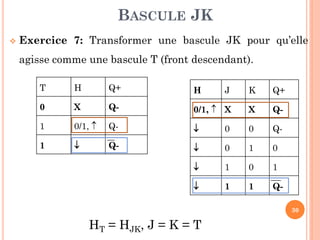

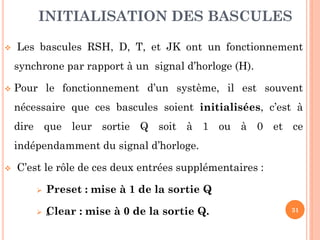

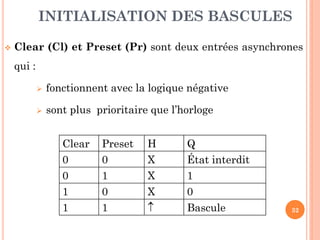

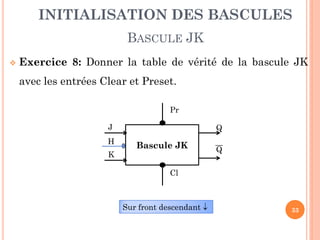

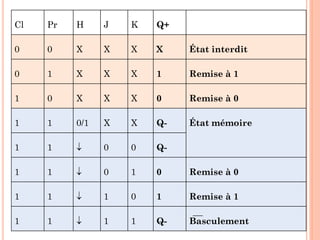

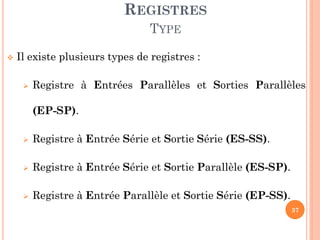

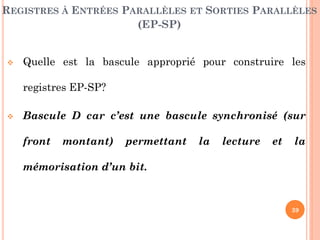

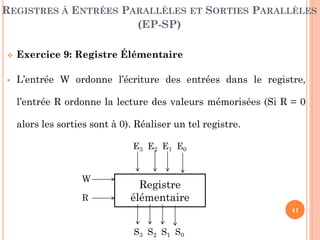

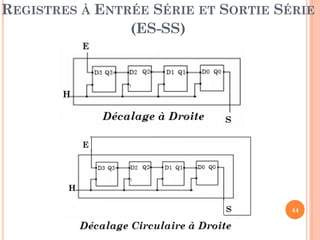

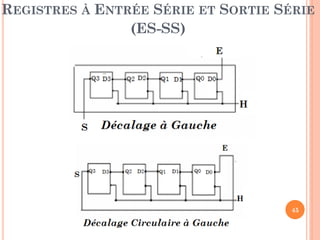

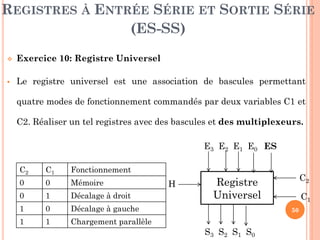

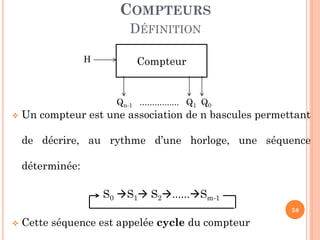

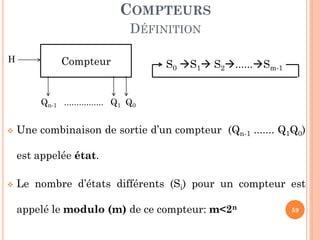

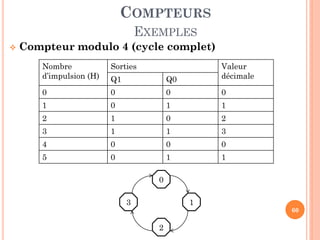

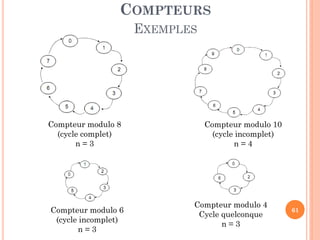

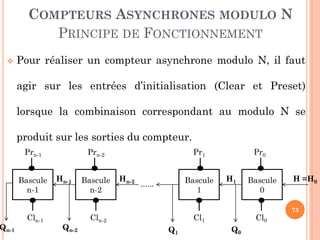

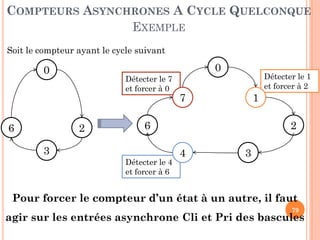

Ce document présente un cours sur la conception de machines digitales, se concentrant principalement sur les circuits séquentiels, y compris les bascules, registres et compteurs. Il décrit des concepts fondamentaux tels que le rôle de l'horloge, les différents types de bascules (RS, D, T, JK) et leurs structures internes, ainsi que les registres et leurs types de fonctionnement. Chaque sujet est illustré par des exemples et des exercices pratiques permettant d'appliquer les notions théoriques.

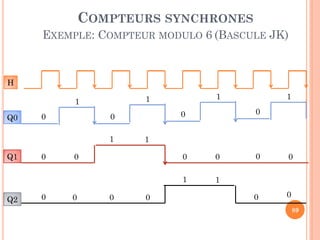

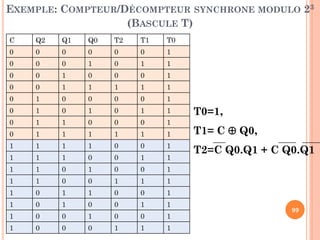

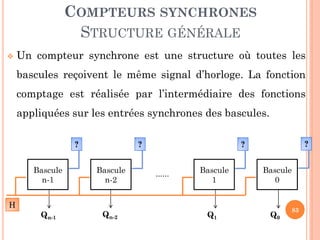

![COMPTEURS SYNCHRONES

ÉTAPES DE RÉALISATION

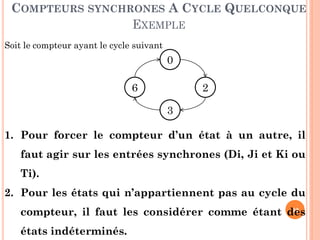

1.

Déterminer le nombre de bascules nécessaires « n »

2.

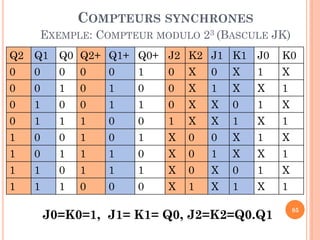

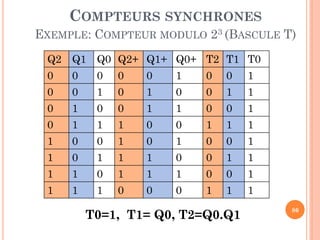

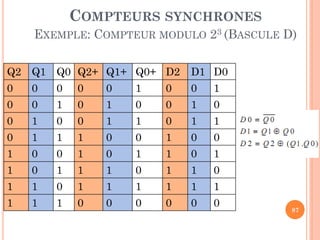

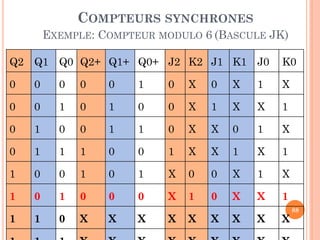

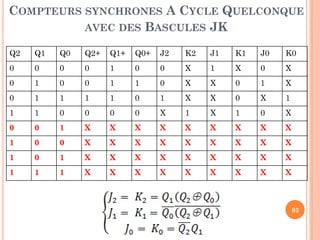

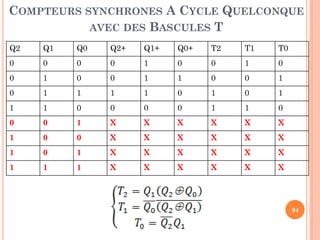

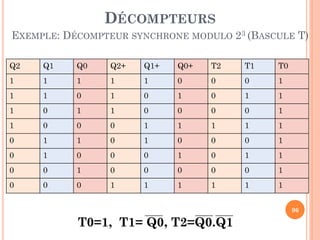

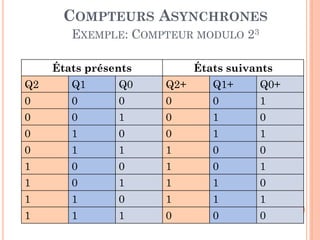

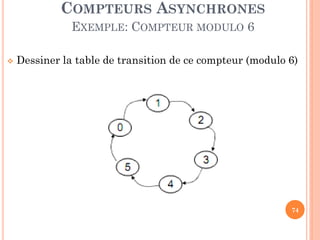

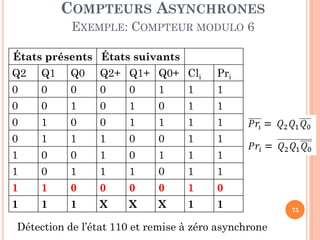

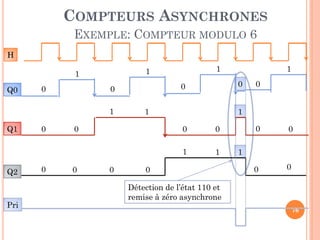

Établir la table de transition du compteur [état suivant

(Qi+) en fonction de l'état présent (Qi)]

3.

Déterminer l'expression des entrées des bascules

84](https://image.slidesharecdn.com/chapitreiiicircuitssquentiels-140116154011-phpapp02/85/Chapitre-iii-circuits-sequentiels-84-320.jpg)