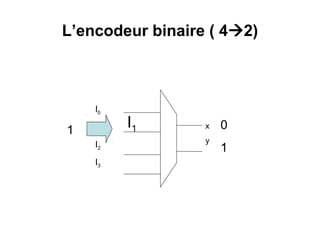

Le document traite des circuits logiques, y compris les circuits combinatoires, les additionneurs, les multiplexeurs et les décodeurs. Il explique les fonctions et les équations associées aux circuits, ainsi que des exercices pratiques pour appliquer les concepts. Des exemples de circuits comme le demi additionneur et l'additionneur complet sont présentés avec des schémas et des tables de vérité.