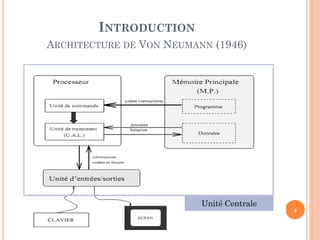

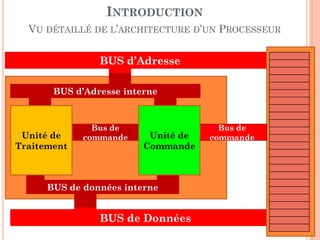

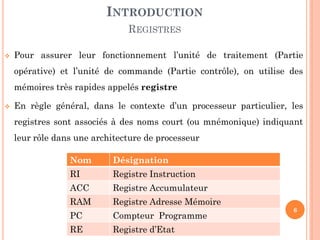

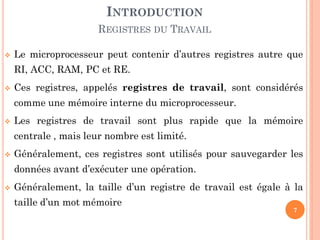

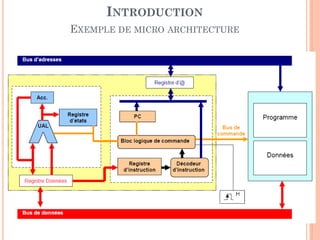

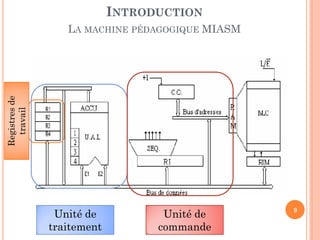

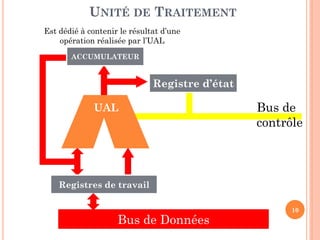

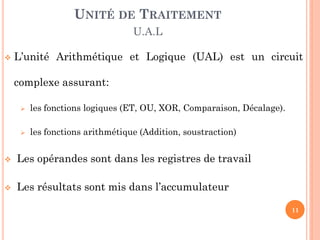

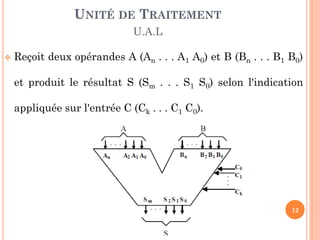

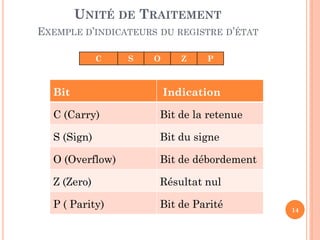

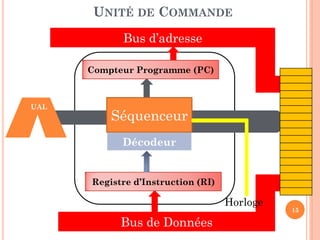

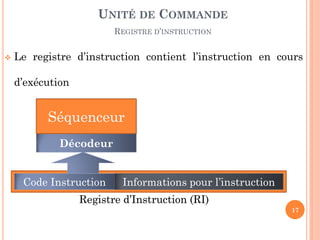

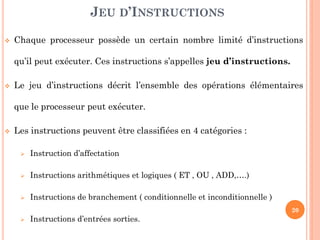

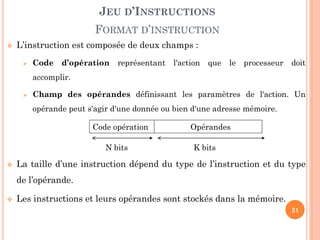

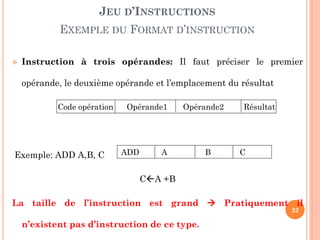

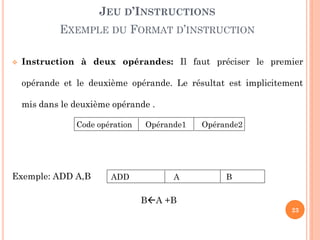

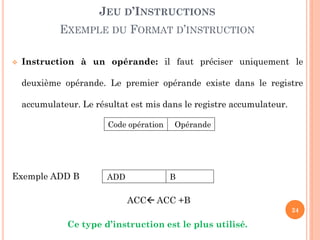

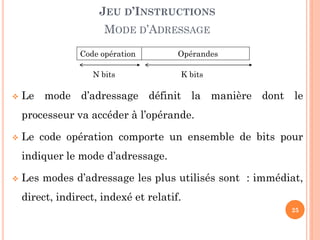

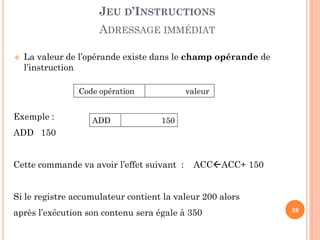

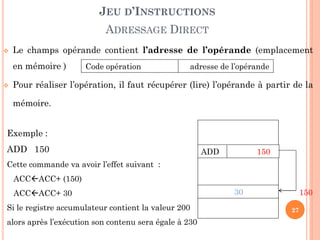

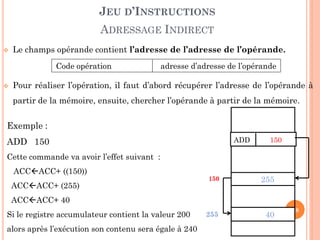

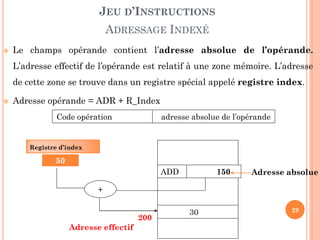

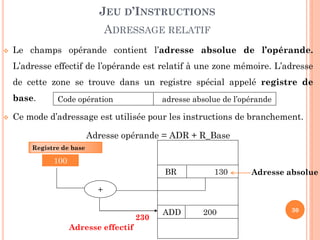

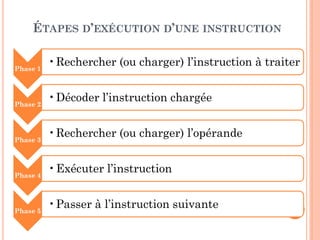

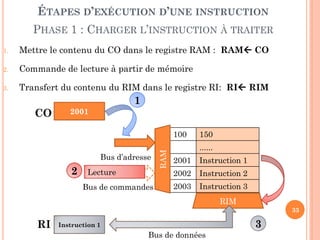

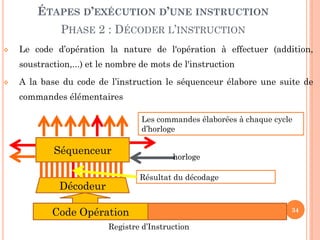

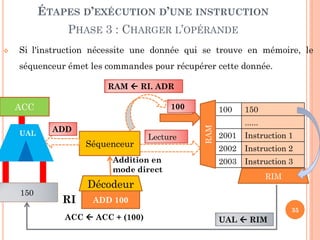

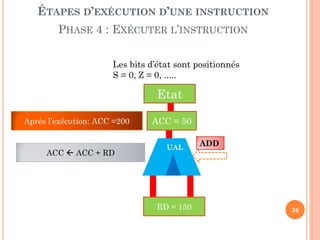

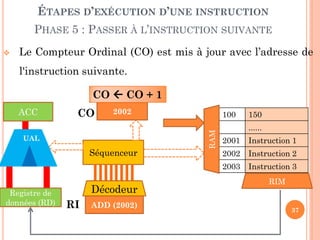

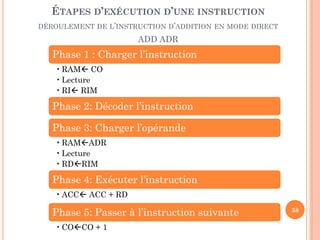

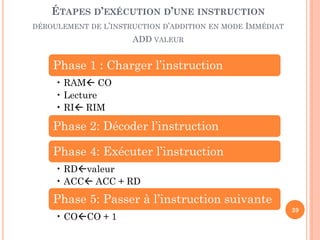

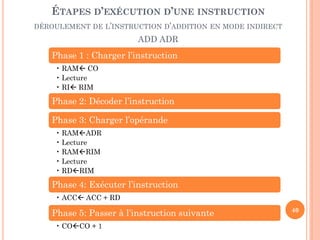

Le document traite de l'architecture interne des processeurs, en décrivant les unités arithmétiques et logiques, l'unité de commande, et les étapes d'exécution des instructions. Il présente également les types d'instructions et les modes d'adressage qu'un processeur peut utiliser. Enfin, il détaille le processus d'exécution d'une instruction à travers plusieurs phases allant du chargement à l'exécution, en passant par le décodage.