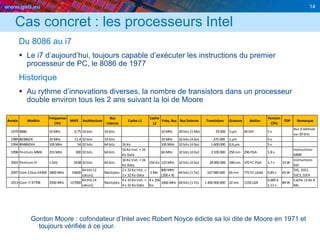

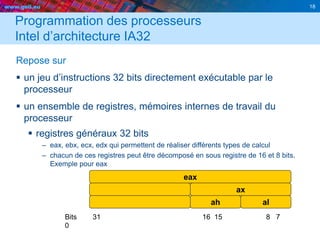

Le document traite de l'architecture des systèmes à microprocesseur, décrivant les différences entre microprocesseurs et microcontrôleurs, ainsi que les architectures de mémoire de Von Neumann et Harvard. Il explore également la structure interne des CPU modernes, les bus système et offre un aperçu des instructions d'assemblage pour les processeurs Intel. Enfin, il montre l'évolution historique des processeurs et les innovations technologiques qui les ont façonnés.

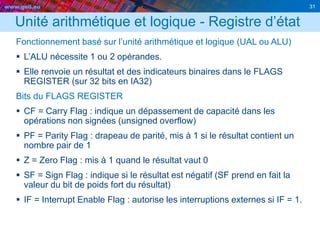

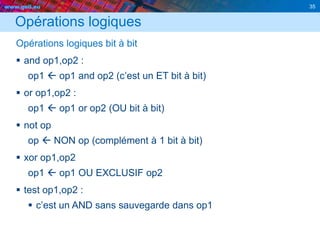

![www.geii.eu 29

Modes d’adressage

Différents modes d’adressage (suite)

Adressage mémoire direct : donnée située à un emplacement

mémoire indiqué explicitement

Exemple : eax (0ACA9910h)

mov eax, [0ACA9910h]

Note : on dit que eax reçoit le contenu de l’emplacement

mémoire 0ACA9910h

Adressage mémoire indirect : donnée située à un emplacement

mémoire indiqué par un registre

Exemple : eax (ebp)

mov eax, [ebp]

Note : on dit que eax reçoit le contenu de l’emplacement

mémoire pointé par ebp](https://image.slidesharecdn.com/assembleuria32-160128225828/85/Base-des-systemes-a-microprocesseur-29-320.jpg)

![www.geii.eu 30

Modes d’adressage

Différents modes d’adressage (suite)

Adressage mémoire indexé : donnée située à un emplacement

mémoire indiqué par calcul Base+Décalage

Exemple : eax (ebp+10)

mov eax, [ebp + 10]

Note : ebp est le registre de Base ; 10 est le décalage

Exemple : ebx (ebp + esi + 10)

mov ebx, [ebp+esi+10]

Note : esi + 10 constitue le décalage (esi seul est l’index)

Mixage des modes d’adressage

Exemple : (ebp) 12

mov word ptr [ebp], 12

Note : word ptr précise que la valeur 12 est une donnée sur 16 bits

(donc les adresses ebp et ebp+1 seront modifiées)

mov byte ptr [ebp], 12

Note : byte ptr précise que la valeur 12 est une donnée sur 8 bits

(donc seul l’octet pointé par ebp est modifié)](https://image.slidesharecdn.com/assembleuria32-160128225828/85/Base-des-systemes-a-microprocesseur-30-320.jpg)