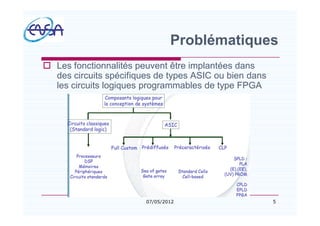

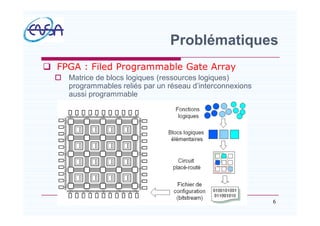

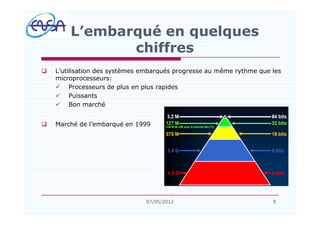

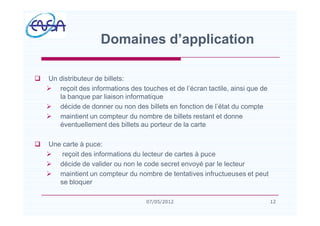

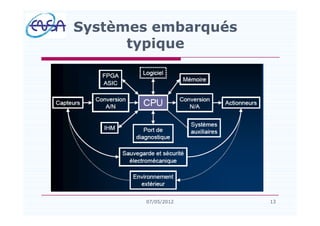

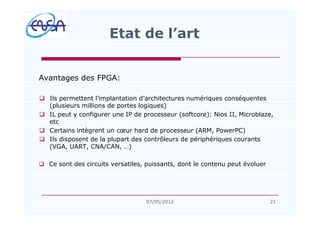

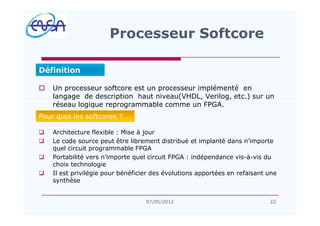

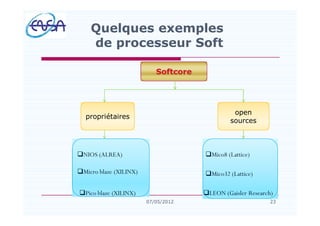

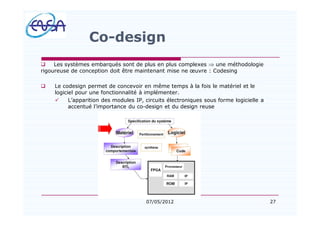

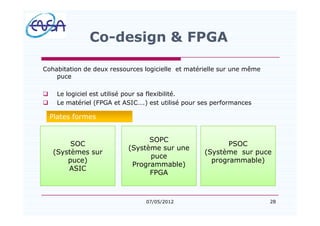

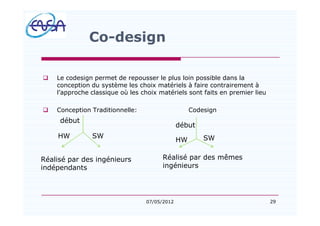

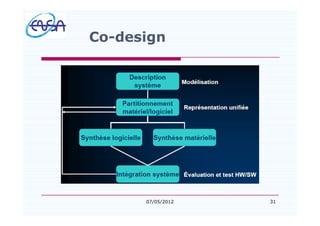

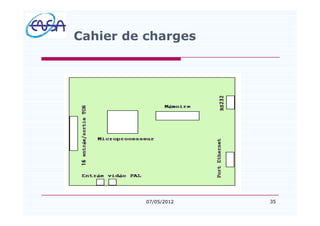

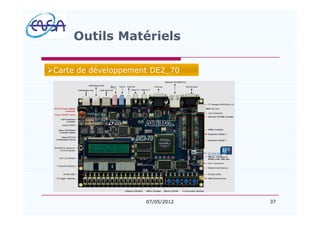

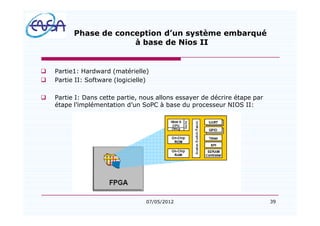

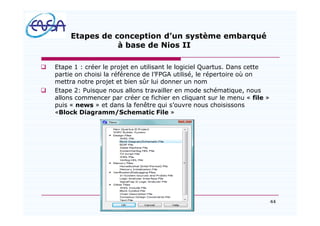

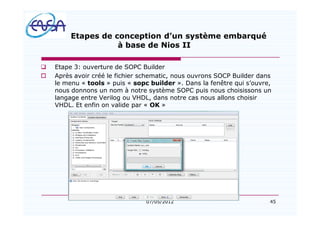

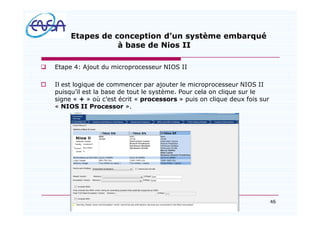

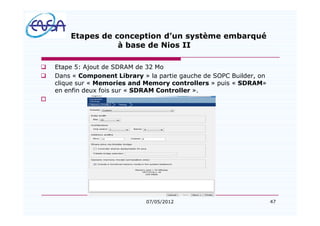

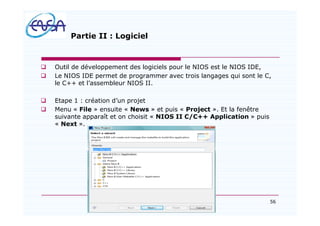

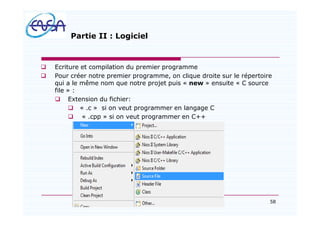

Le document aborde la conception des systèmes embarqués, soulignant leur complexité croissante et la nécessité d'un compromis entre flexibilité, performance et coût. Il discute des contraintes spécifiques auxquelles ces systèmes font face, telles que la consommation d'énergie et la robustesse, tout en mettant en avant les avantages des architectures basées sur FPGA. Enfin, il souligne l'importance d'une méthodologie rigoureuse comme le co-design pour optimiser le développement matériel et logiciel des systèmes embarqués.