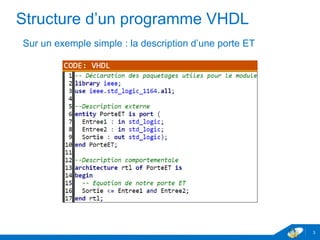

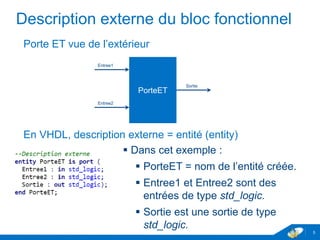

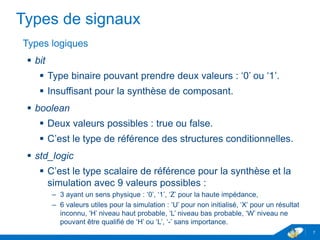

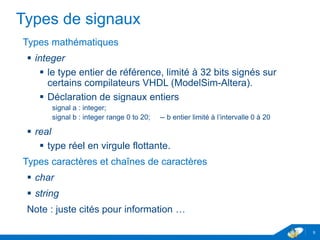

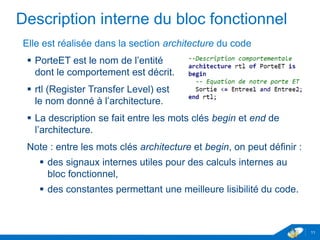

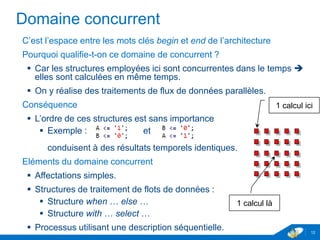

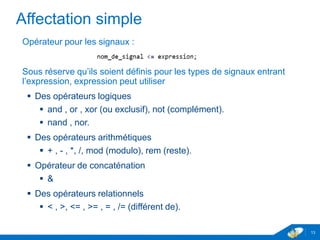

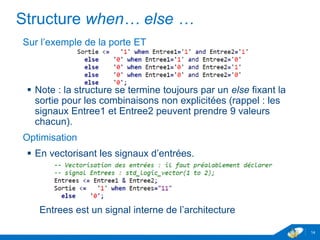

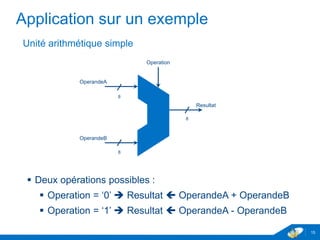

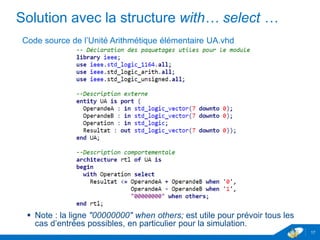

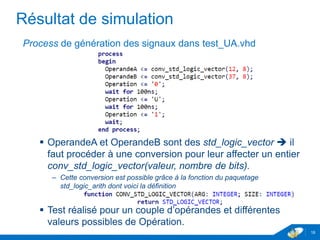

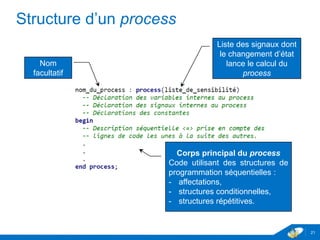

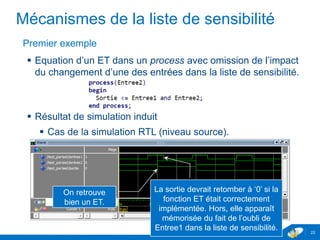

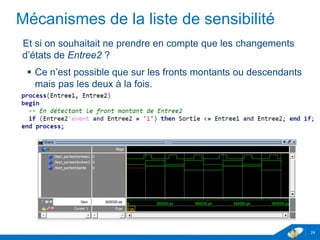

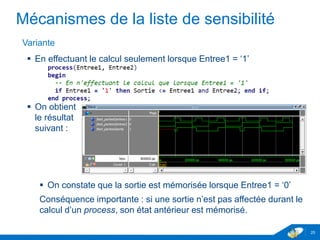

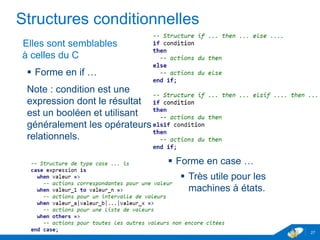

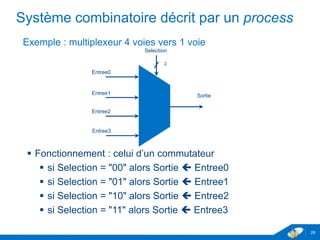

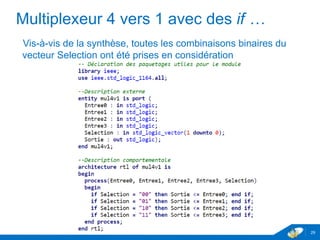

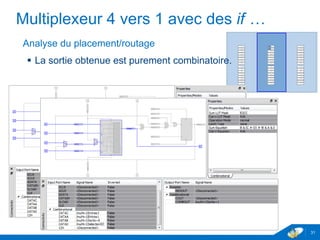

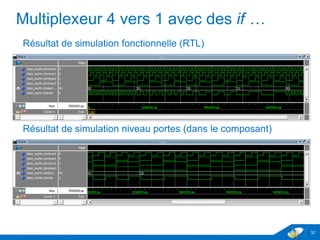

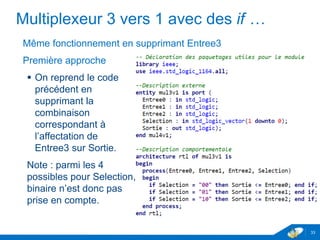

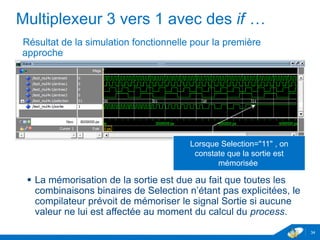

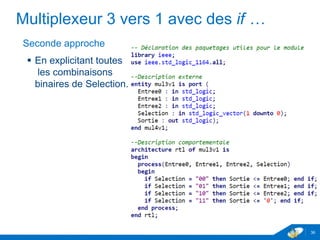

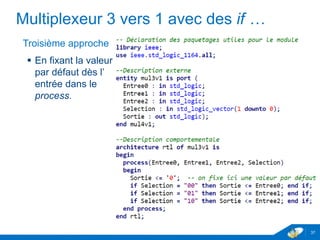

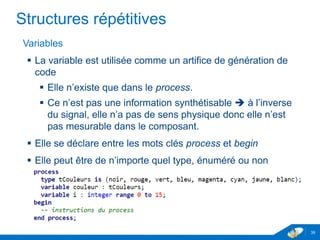

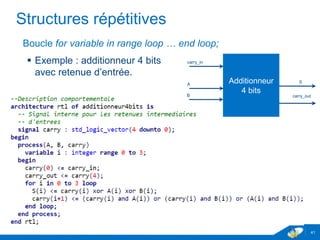

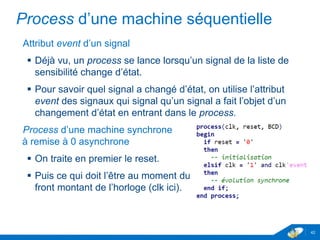

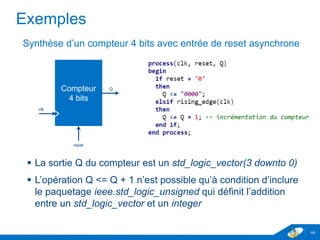

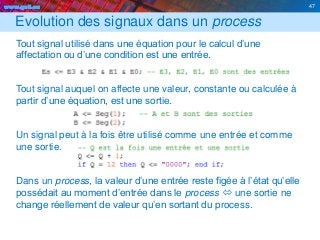

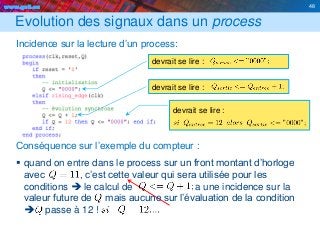

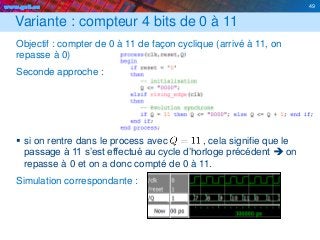

Ce document est une introduction au langage VHDL pour la description de composants électroniques numériques, en mettant l'accent sur les structures de programme, la déclaration de signaux, types logiques et mathématiques, ainsi que les processus séquentiels. Il présente des exemples pratiques, incluant la conception d'une porte logique et d'un multiplexeur, tout en discutant des mécanismes de simulation et des structures conditionnelles. Le texte aborde également les enjeux de la mémorisation des sorties et des ressources FPGA, fournissant des recommandations pour un design efficace.