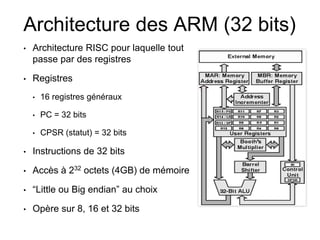

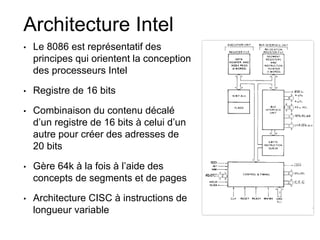

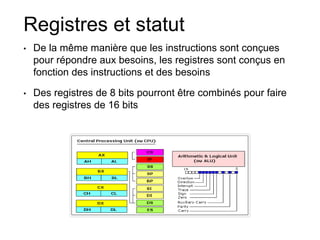

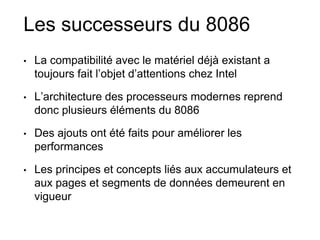

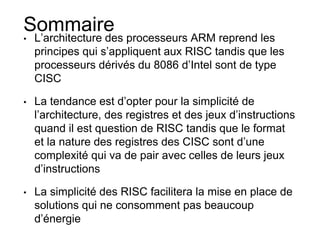

Le document traite de l'architecture ARM et de ses évolutions, en comparant brièvement avec l'architecture x86 d'Intel. Il décrit les caractéristiques des processeurs ARM, leur architecture RISC, et leur utilisation généralisée dans l'industrie, notamment dans les smartphones. Le résumé se termine en soulignant la simplicité et l'efficacité énergétique des architectures ARM par rapport aux architectures CISC comme celles d'Intel.