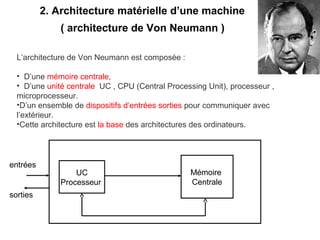

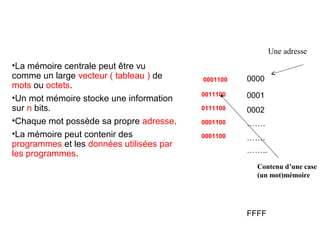

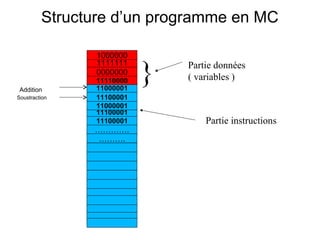

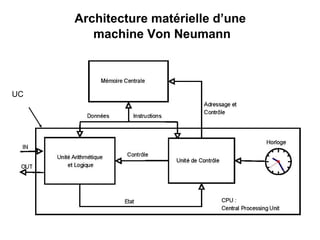

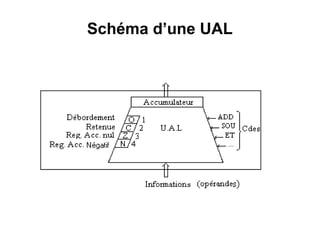

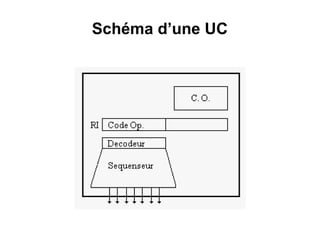

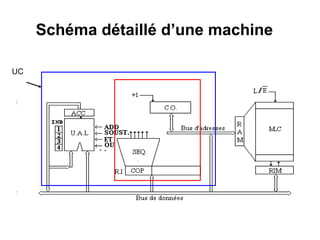

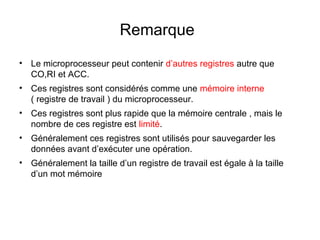

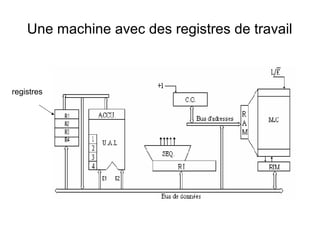

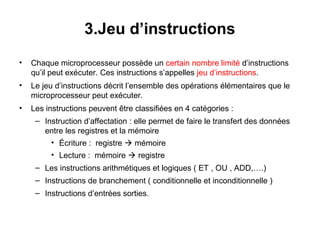

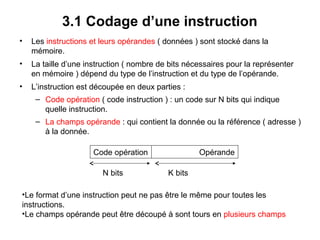

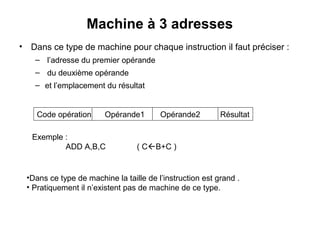

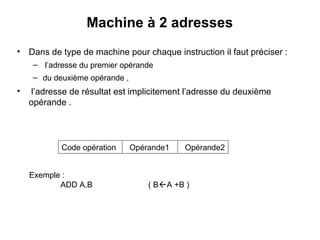

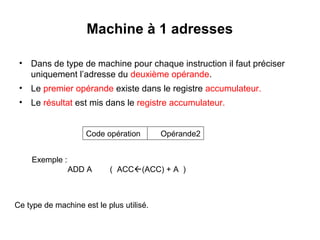

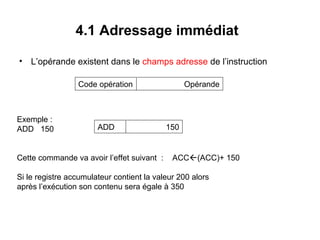

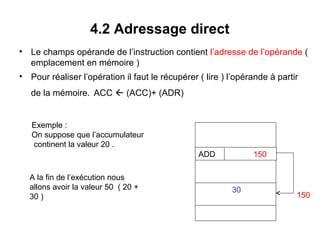

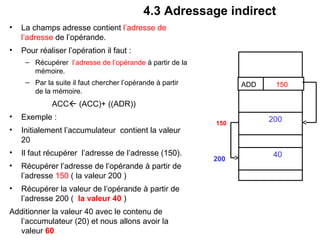

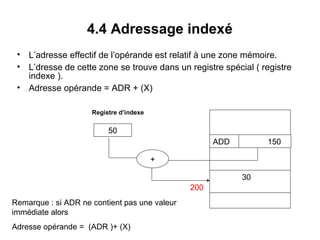

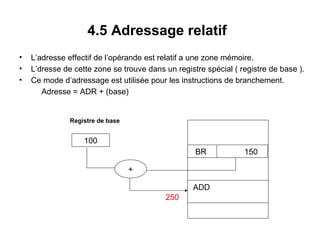

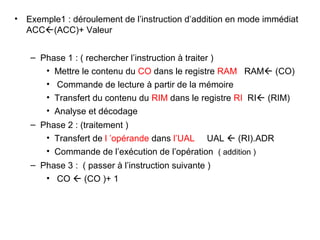

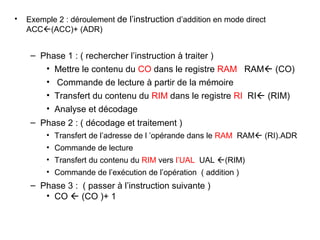

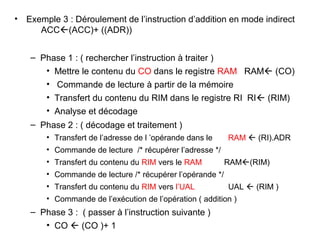

Le document traite de l'architecture de base des ordinateurs, en se concentrant sur l'architecture de von Neumann qui comprend la mémoire centrale, l'unité de contrôle et l'unité arithmétique et logique. Il détaille le processus de programmation et d'exécution d'instructions, ainsi que les modes d'adressage et les cycles d'exécution. Enfin, il présente les différents types d'instructions et leur codage dans le contexte de l'exécution par le microprocesseur.