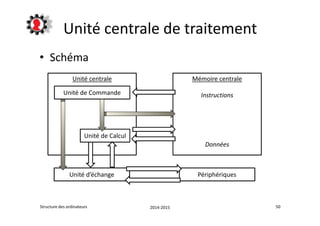

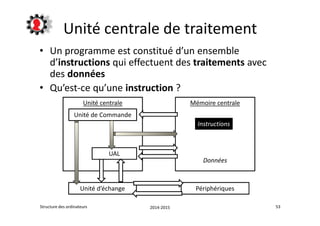

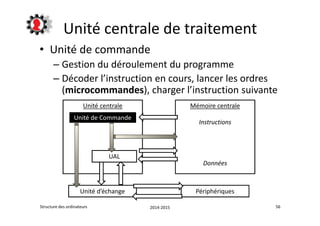

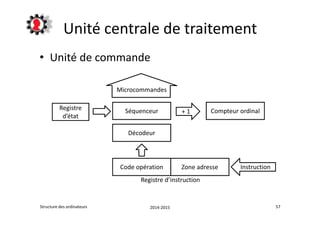

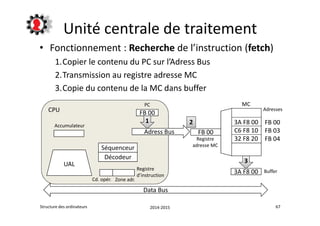

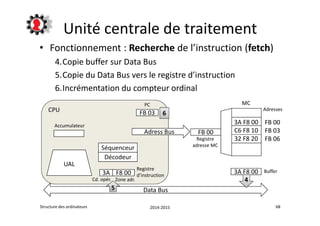

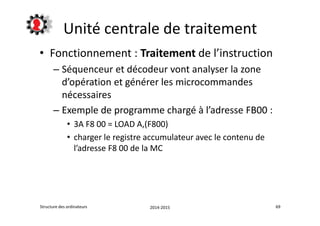

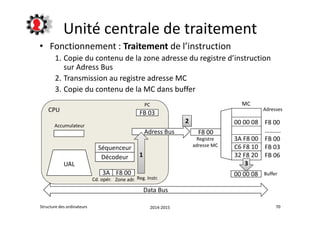

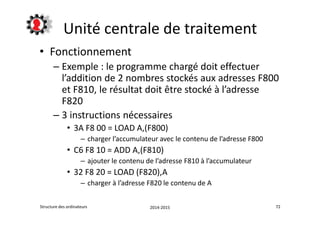

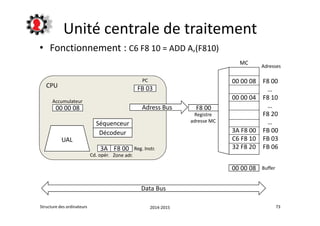

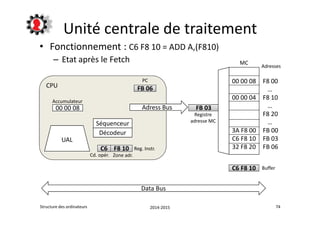

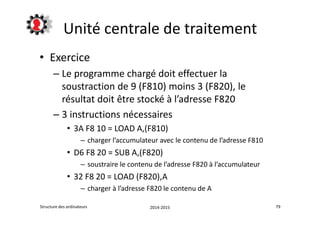

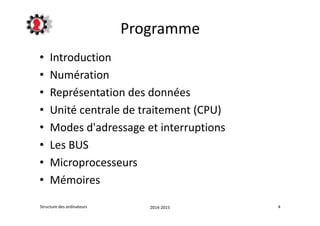

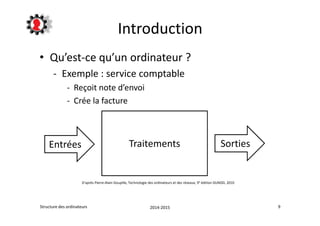

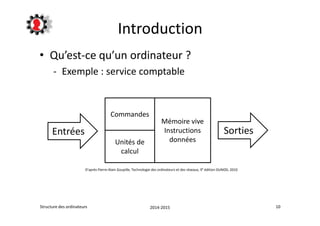

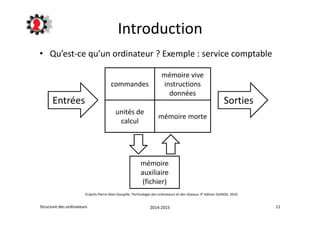

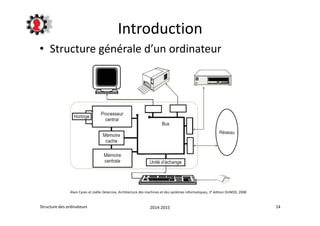

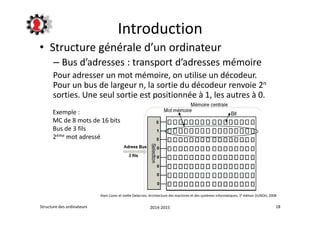

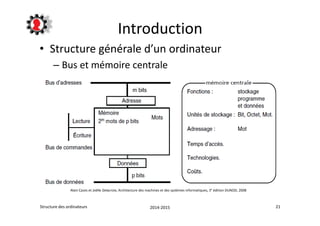

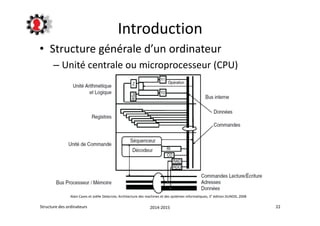

Le document présente un cours sur la structure des ordinateurs, abordant à la fois l'architecture matérielle et les systèmes d'exploitation. Il traite des composants internes tels que le processeur, la mémoire, et les bus de communication, ainsi que des concepts fondamentaux comme la numération binaire. Des exemples pratiques, tels que la facturation, illustrent comment un ordinateur exécute des instructions.

![Représentation des données

• Représentation des entiers positifs

– Conversion en base 2

• Sur 8 bits, on a un intervalle en base 10 [0,256]

• 8 bits ==> 28 valeurs possibles

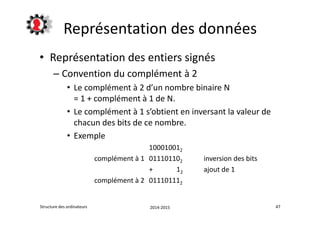

• Représentation des entiers signés

– Convention de la valeur signée

• Le bit de poids fort est le bit de signe

• Si sa valeur est 0, alors le nombre codé est positif

• Si sa valeur est 1, alors le nombre codé est négatif

• Sur 8 bits, l’intervalle en base 10 est modifié

[- 127, + 127]

Structure des ordinateurs 2014-2015 46](https://image.slidesharecdn.com/structure-des-ordinateurs-140902082733-phpapp02/85/Structure_Des_Ordinateurs-46-320.jpg)