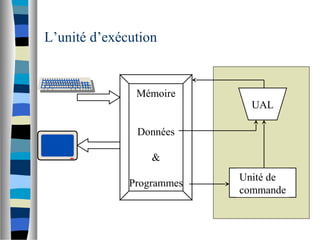

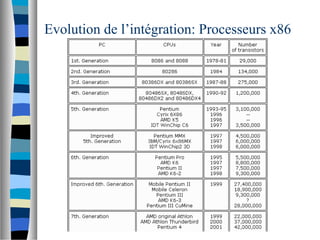

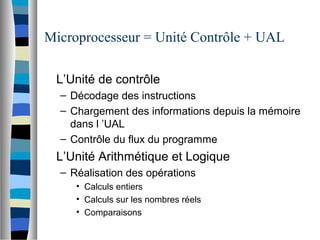

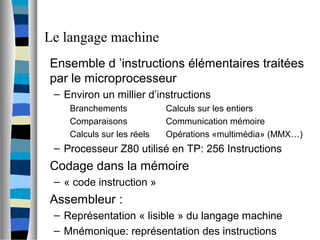

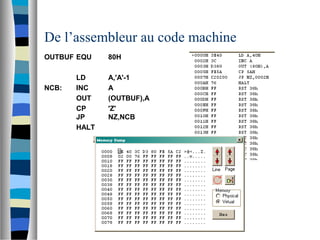

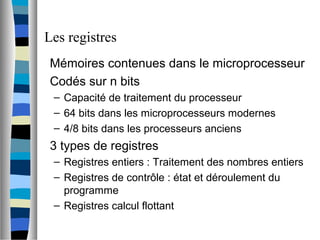

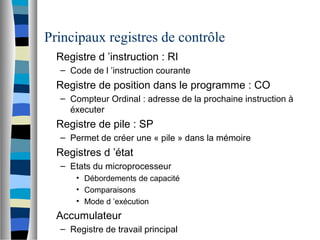

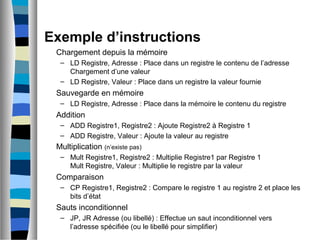

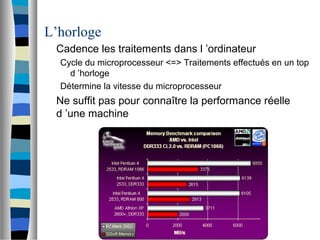

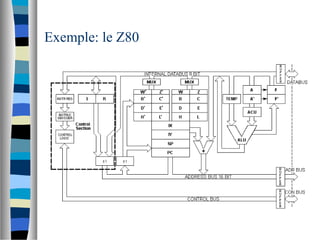

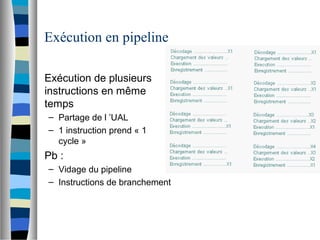

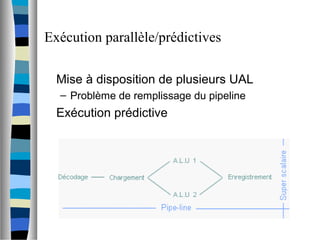

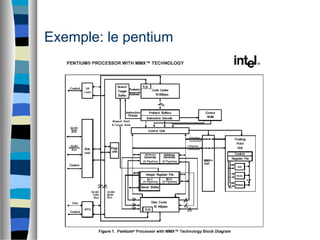

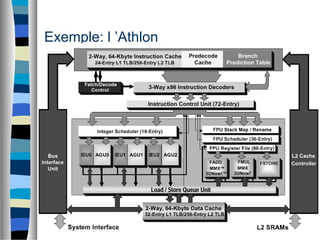

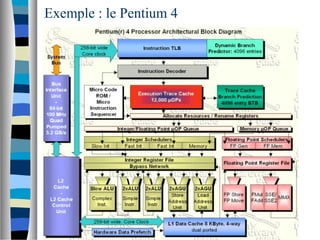

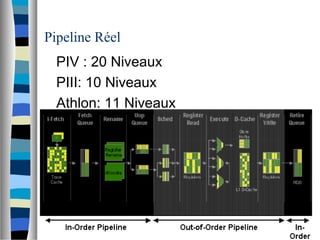

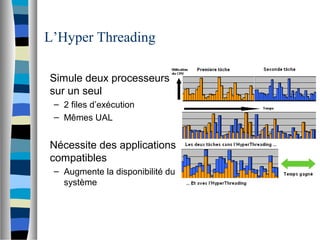

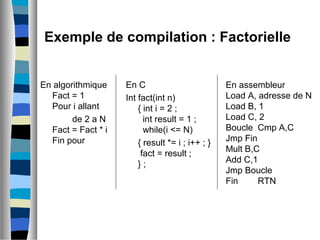

Le document traite de l'architecture des microprocesseurs, en détaillant les composants tels que l'unité de contrôle, l'unité arithmétique et logique (UAL), et les différents types de registres. Il aborde également le langage machine, les instructions, les modes d'adressage, ainsi que les techniques d'exécution comme le pipeline et l'exécution prédictive. Enfin, il présente des exemples d'instructions et leur fonctionnement dans le contexte de la programmation en assembleur.