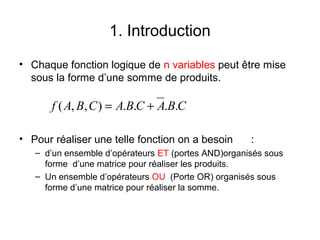

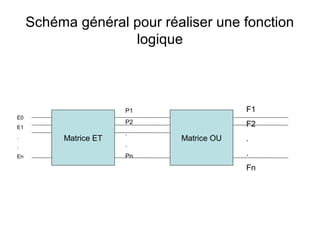

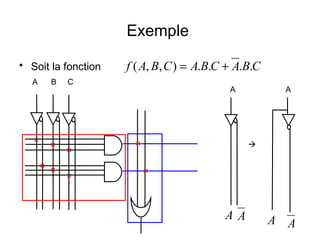

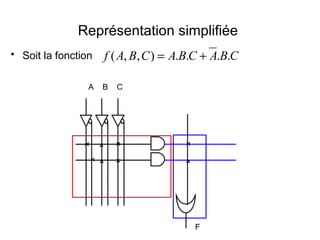

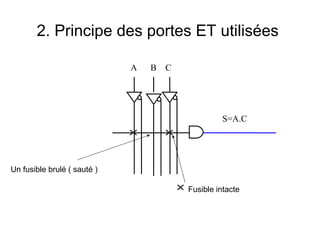

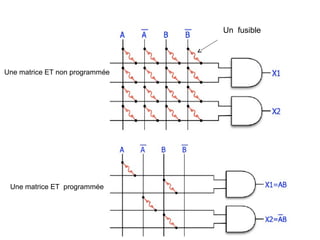

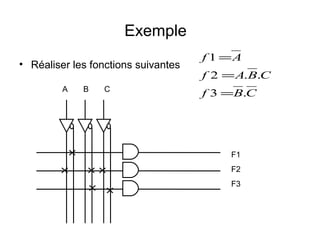

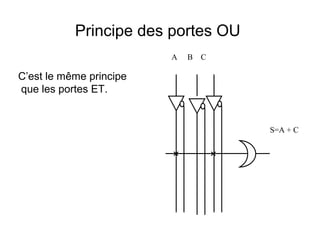

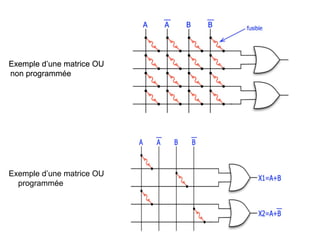

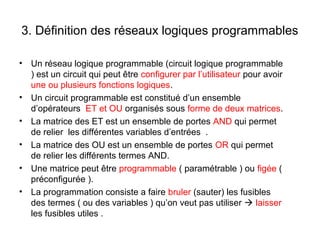

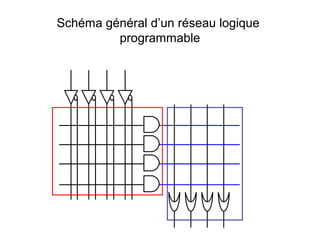

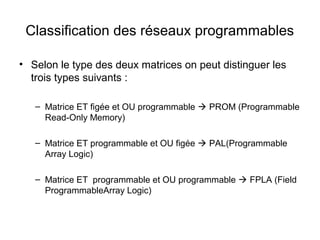

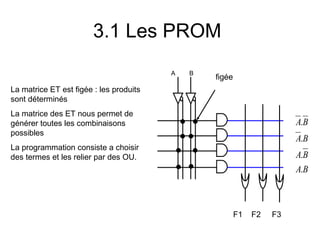

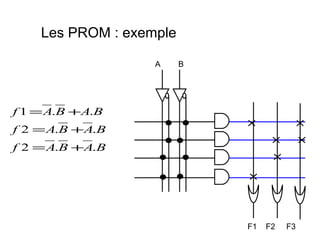

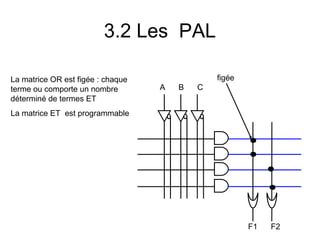

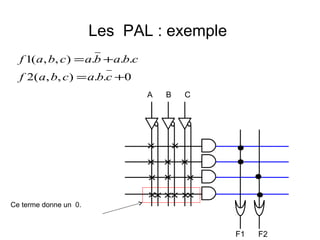

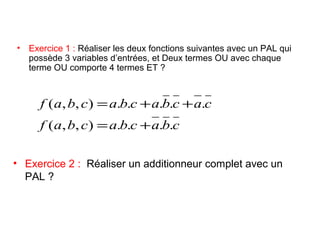

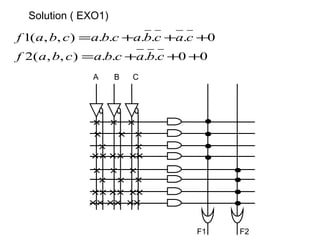

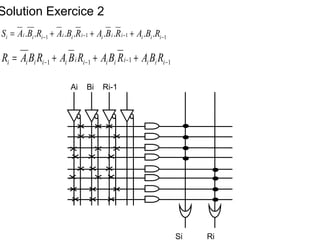

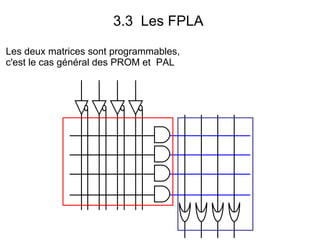

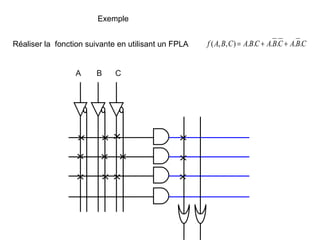

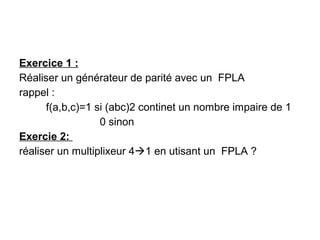

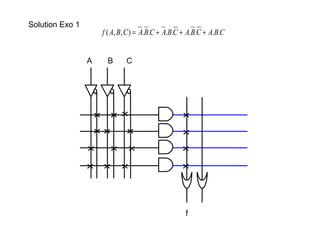

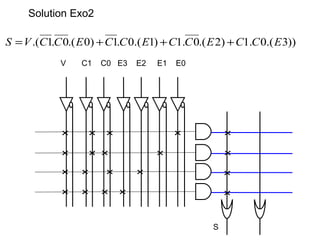

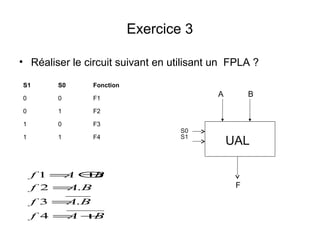

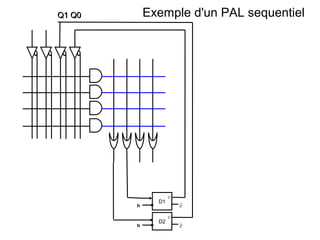

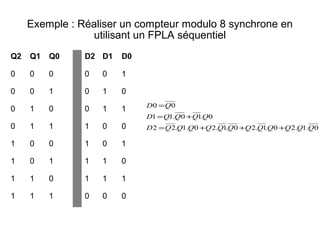

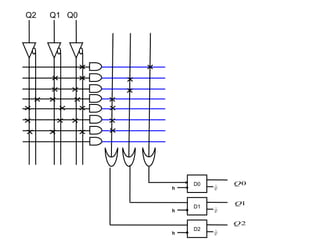

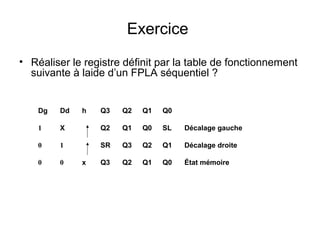

Le document présente les réseaux logiques programmables, qui permettent de configurer des circuits logiques pour réaliser différentes fonctions. Il décrit les types de réseaux programmables, notamment les PROM, PAL et FPLA, ainsi que leur fonctionnement à travers des matrices AND et OR, et introduit également les réseaux séquentiels. Des exemples et exercices pratiques sont fournis pour illustrer la réalisation de diverses fonctions logiques et circuits.