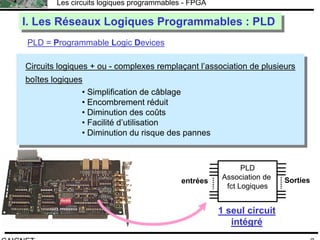

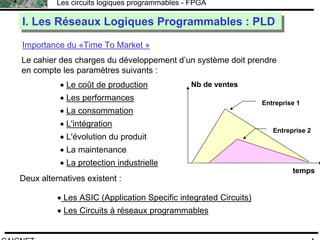

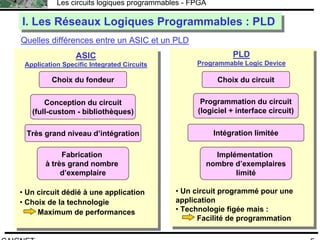

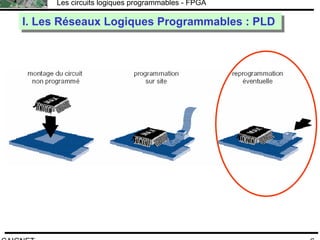

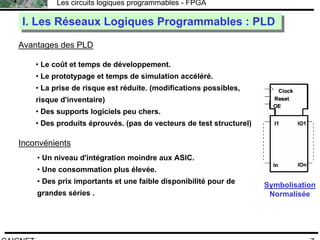

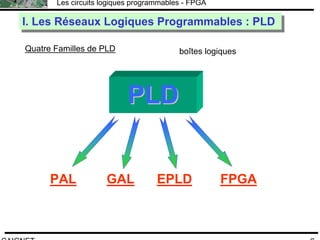

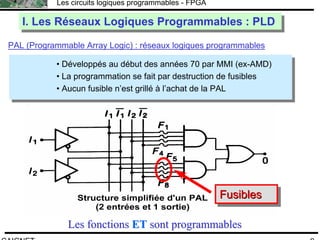

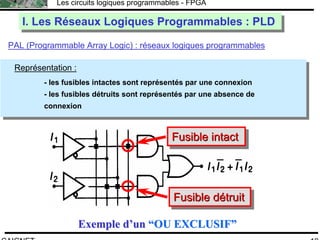

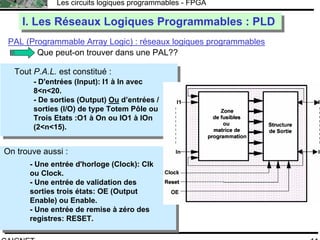

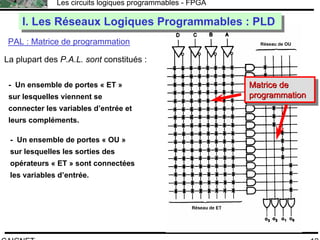

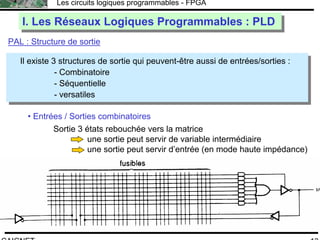

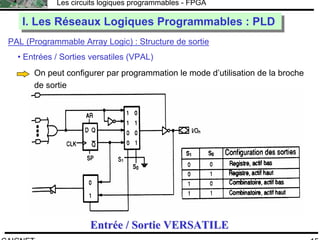

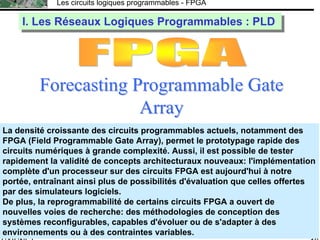

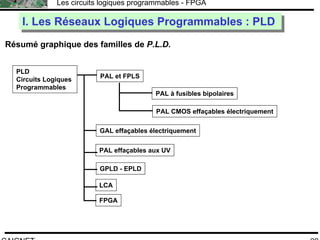

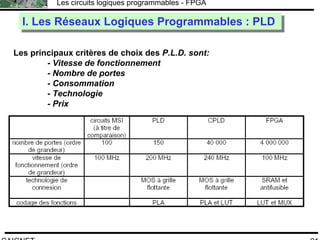

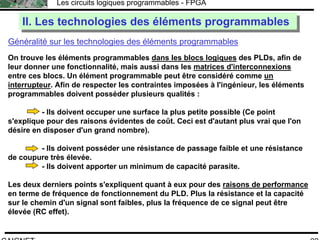

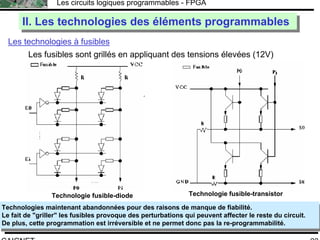

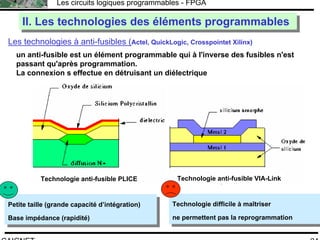

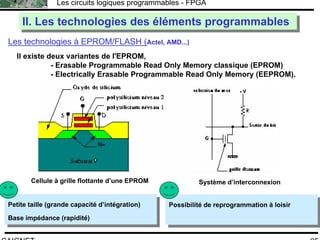

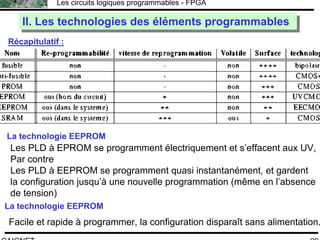

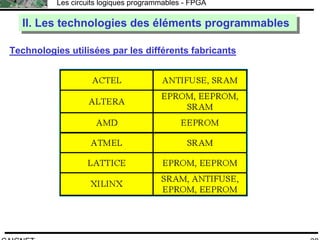

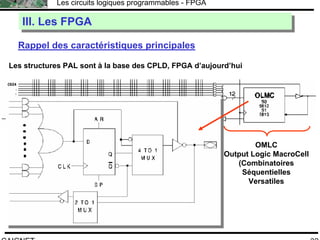

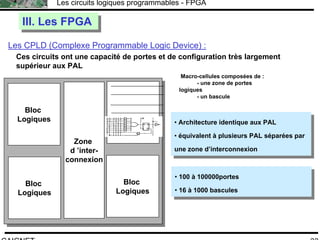

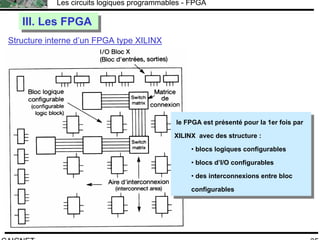

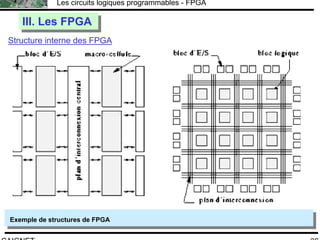

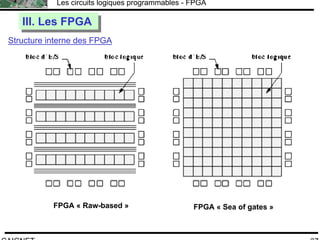

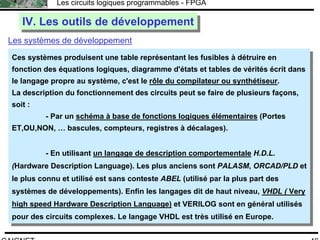

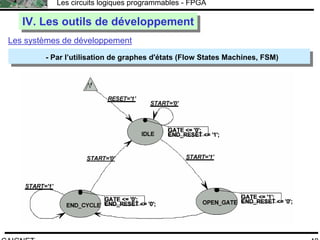

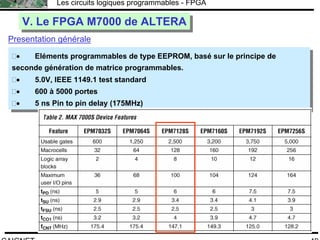

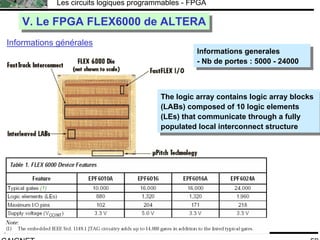

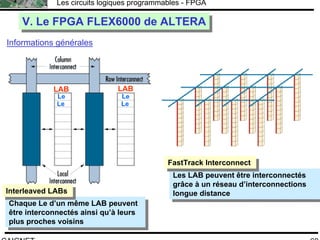

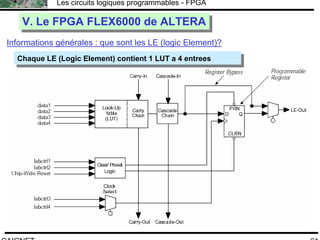

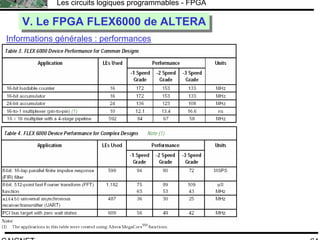

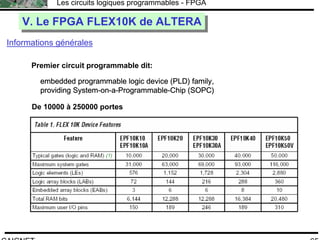

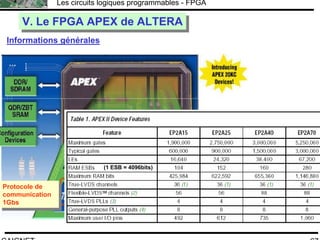

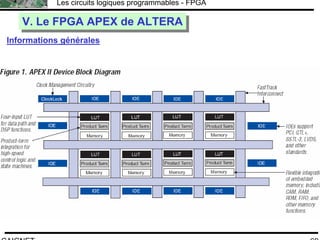

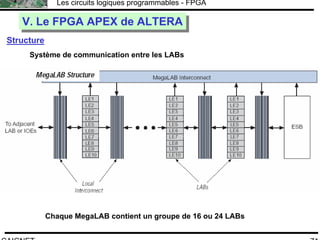

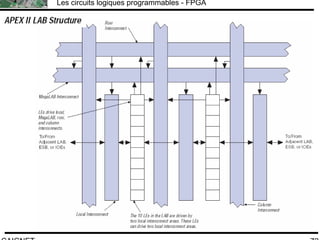

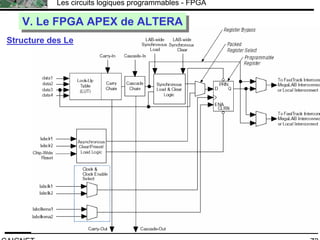

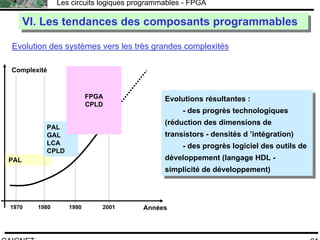

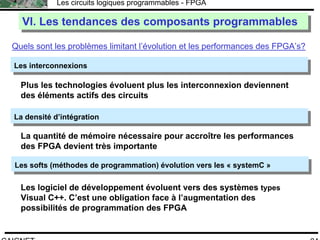

Le document présente une étude approfondie des circuits logiques programmables, particulièrement les FPGA, en discutant de leurs caractéristiques, avantages et technologies. Il compare les ASIC et les PLD, décrit différentes familles de PLD telles que les GAL et les PAL, et examine les technologies de programmation. Les tendances actuelles et futures des circuits programmables ainsi que les critères de choix des PLD sont également abordés.