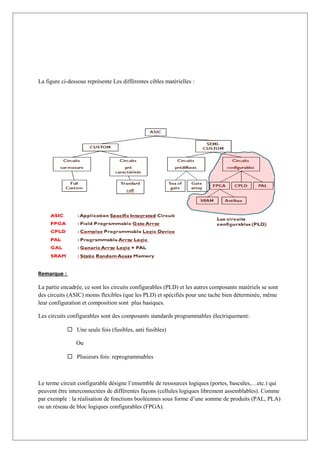

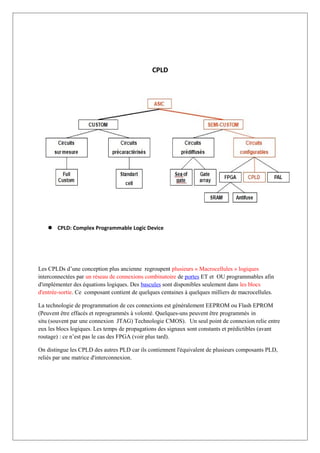

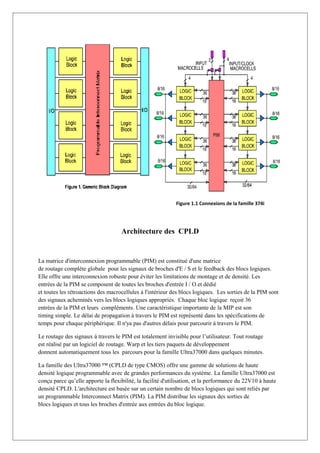

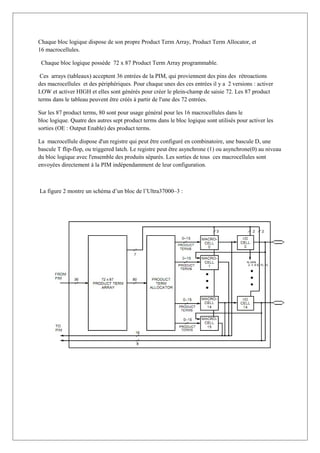

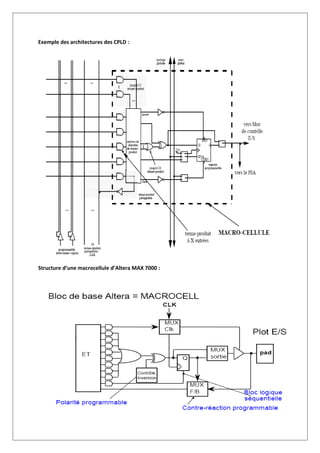

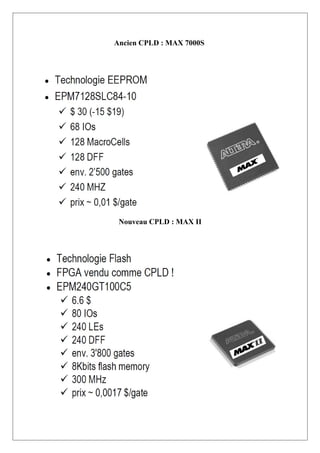

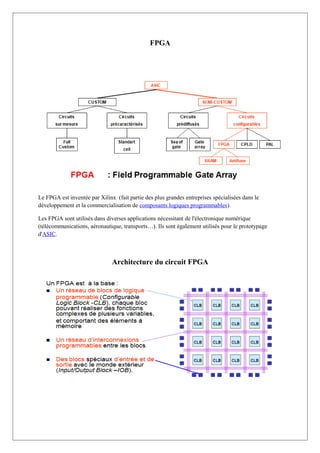

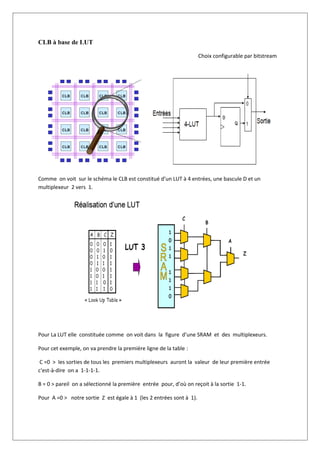

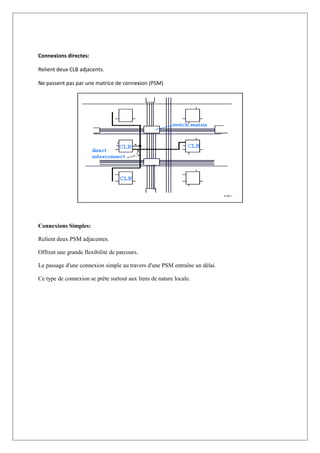

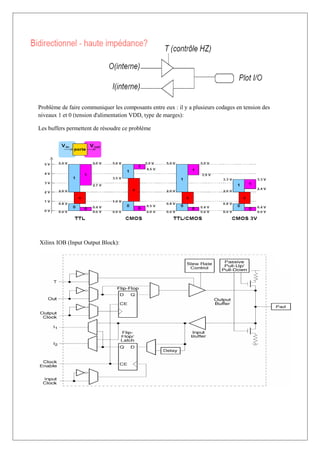

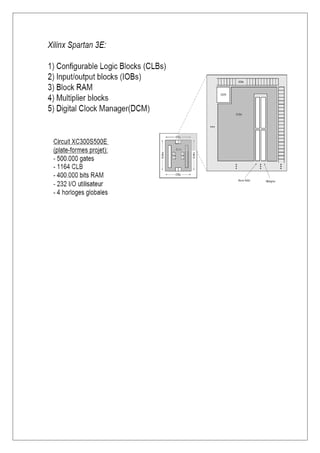

Le document traite de l'architecture et de la programmation des circuits CPLD et FPGA, en mettant en évidence l'évolution technologique et applicative qui a permis des systèmes électroniques plus complexes et miniaturisés. Il explique les différentes cibles matérielles, en soulignant les avantages des CPLD et FPGA pour des applications spécifiques, tout en abordant les contraintes de conception. En outre, le texte décrit en détail l'architecture interne des CPLD et FPGA, ainsi que leur fonctionnement et leurs utilisations dans divers domaines industriels.