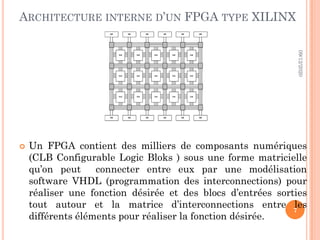

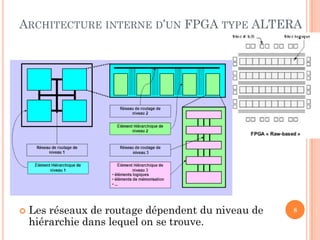

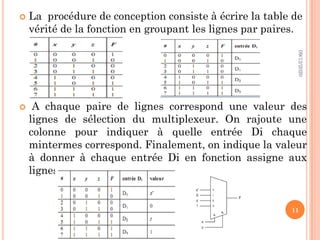

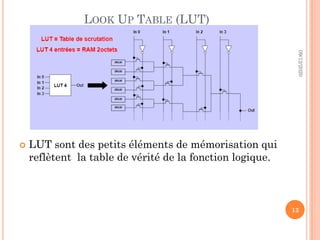

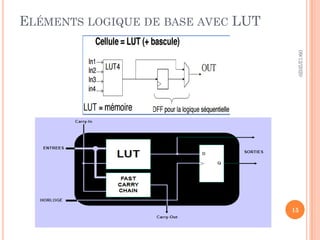

Le document traite de l'architecture des FPGA, en expliquant leurs caractéristiques, familles principales (Xilinx et Altera), ainsi que leur structure matérielle comprenant des blocs logiques programmables. Il décrit également les éléments de base tels que les LUTs et les multiplexeurs pour réaliser des fonctions logiques complexes. Enfin, il met en lumière la flexibilité des FPGA qui permettent des configurations rapides selon les besoins des systèmes numériques.