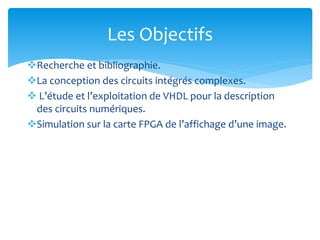

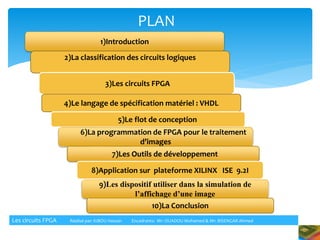

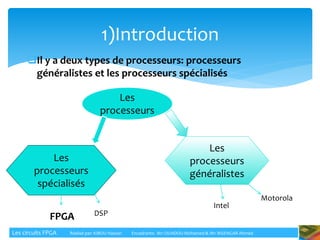

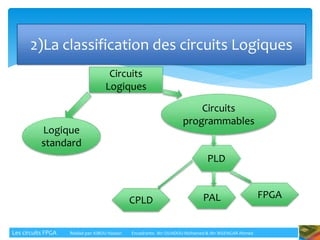

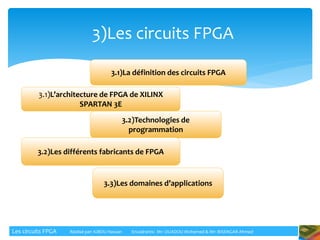

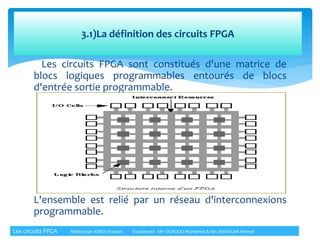

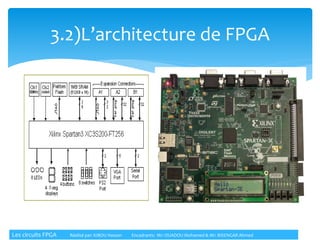

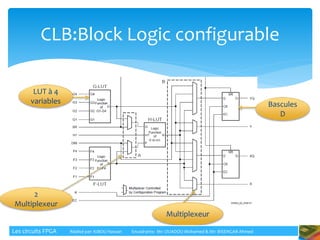

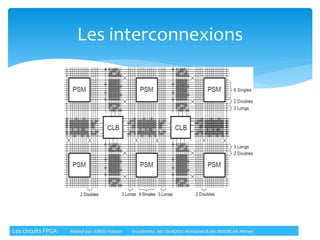

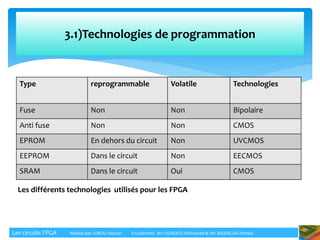

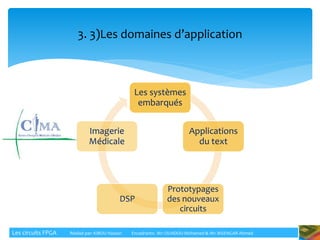

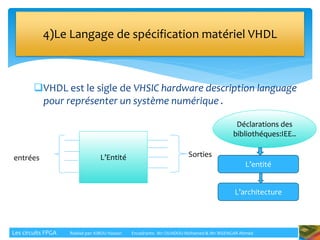

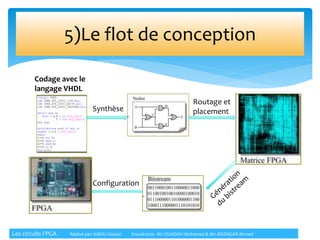

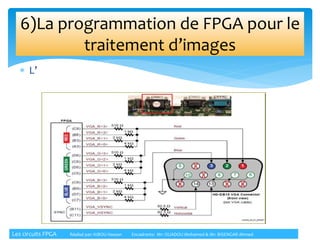

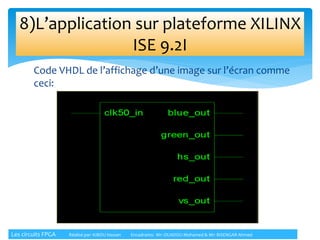

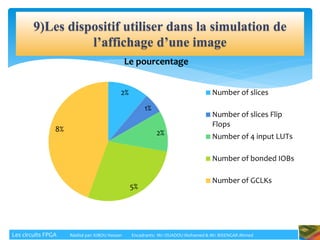

Le document présente un projet de fin d'étude sur les circuits FPGA, impliquant la recherche, la conception et la simulation d'affichage d'images sur une carte FPGA. Il aborde des sujets tels que le langage VHDL, la classification des circuits logiques, et les outils de développement utilisés. Les objectifs incluent l'étude des architectures FPGA et leur application potentiel dans le traitement d'images.