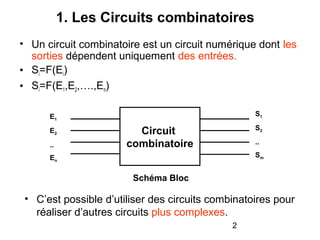

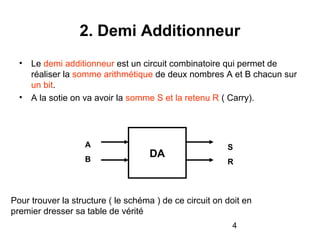

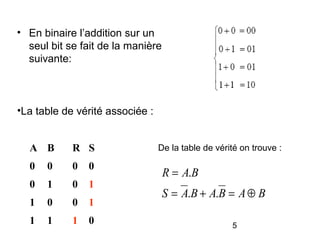

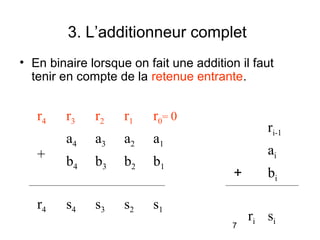

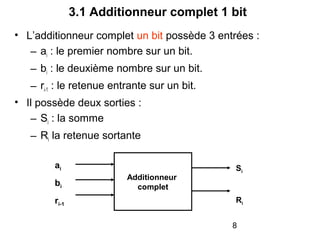

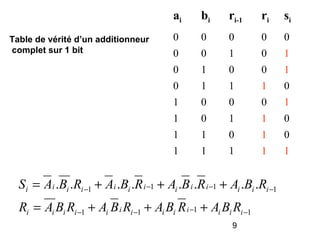

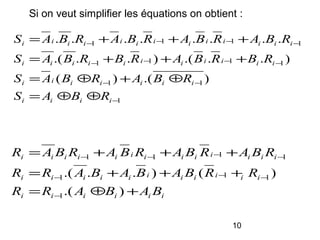

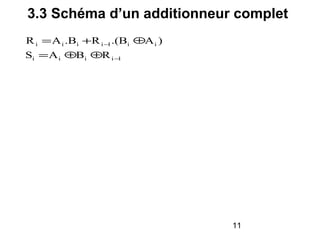

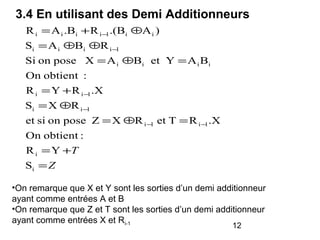

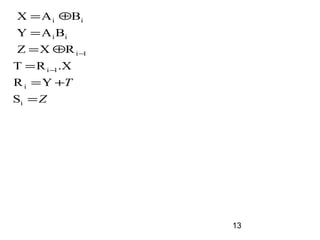

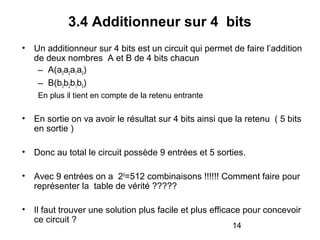

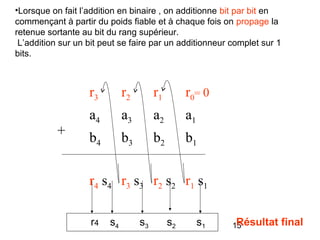

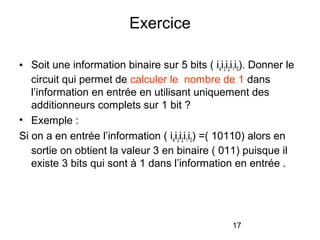

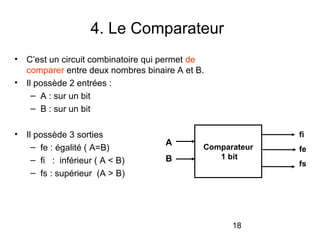

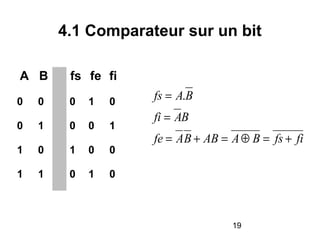

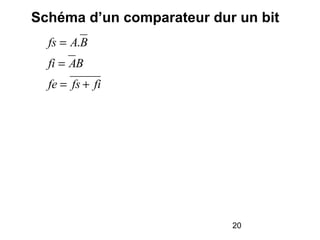

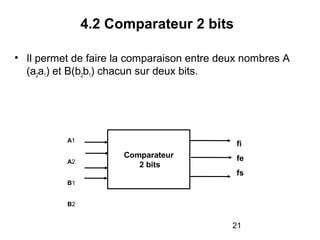

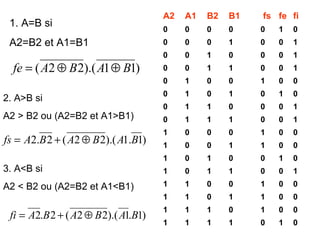

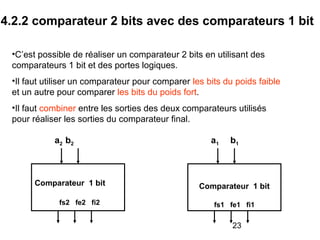

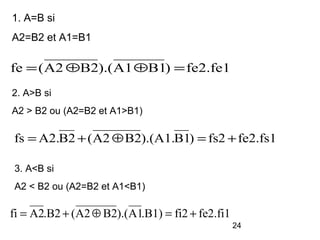

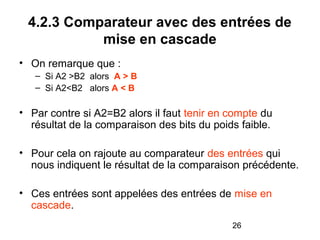

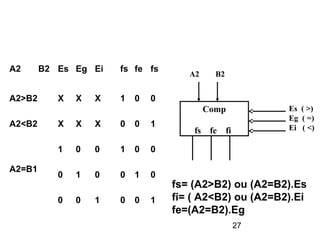

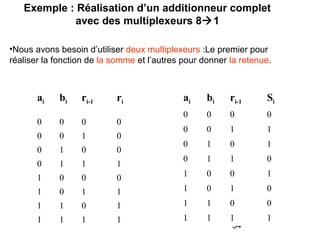

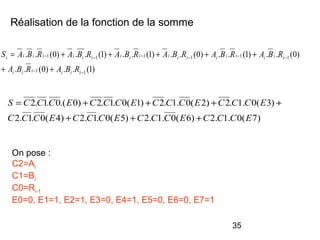

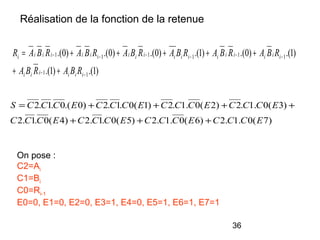

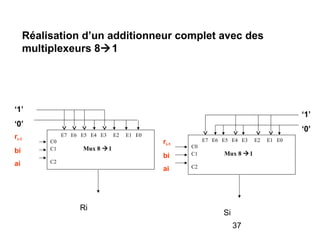

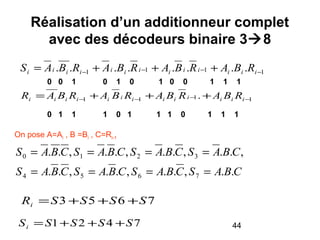

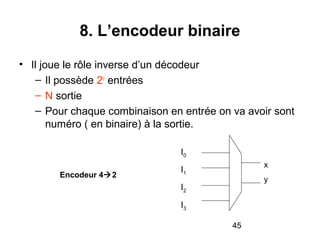

Le document traite de la conception et de la structure des circuits combinatoires, notamment des objets tels que le demi additionneur, l'additionneur complet, et le comparateur. Il explique comment ces circuits peuvent être utilisés pour créer des systèmes plus complexes en utilisant des tables de vérité et en illustrant des exemples pratiques. Les circuits sont décrits avec leurs entrées, sorties et schémas structurels pour clarifier leur fonctionnement.