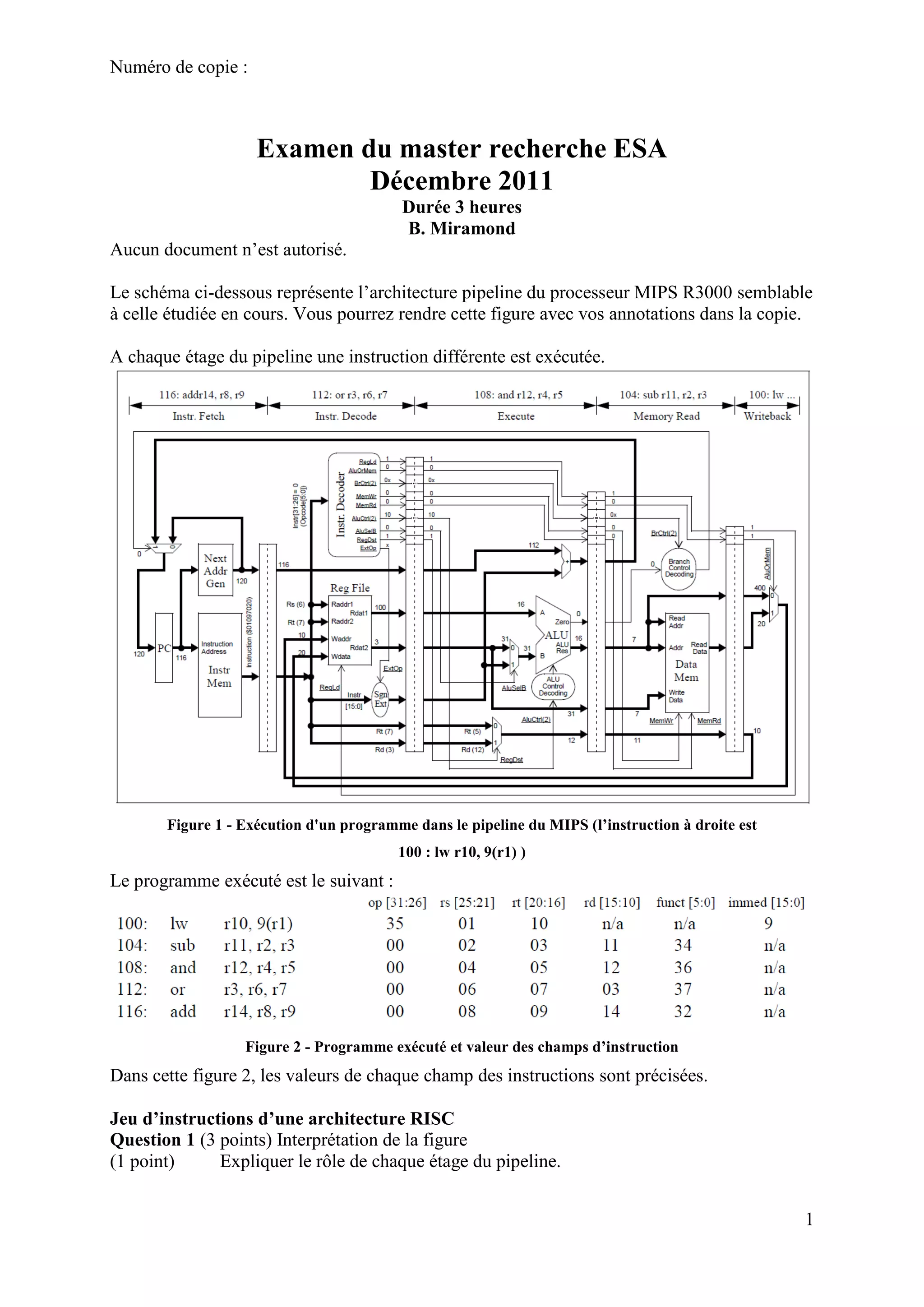

Le document est un examen de master recherche sur l'architecture du processeur MIPS R3000, comprenant des questions sur l'interprétation du pipeline, les types d'instructions, les performances des instructions, et l'exécution de programmes en virgule fixe et flottante. Les questions abordent également le fonctionnement du pipeline, l'architecture multiprocesseur pour une application de somme matricielle, et les mécanismes pour maintenir le remplissage du pipeline. Les réponses exigent des représentations graphiques et des explications détaillées sur diverses instructions et architectures.