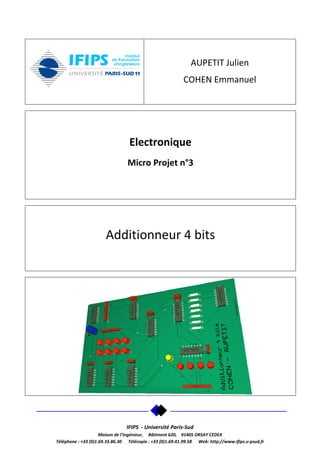

Le document décrit la conception d'un circuit additionneur pour des nombres en binaire, abordant initialement un additionneur de 3 bits avant d'étendre à 4 bits. Il inclut des sections sur la commande des entrées, visualisation des sorties à l'aide de diodes LED, et un afficheur à 7 segments pour afficher les résultats. Bien que le circuit soit alimenté correctement, il présente des problèmes de logique, entraînant des résultats d'addition incorrects.