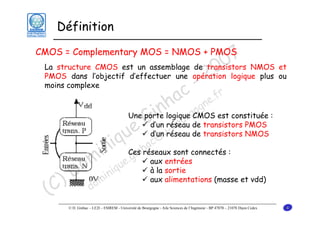

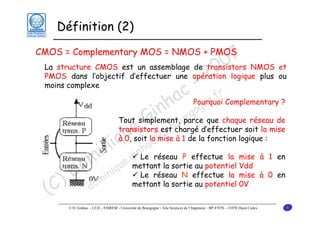

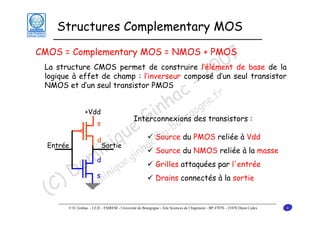

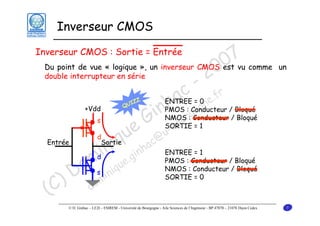

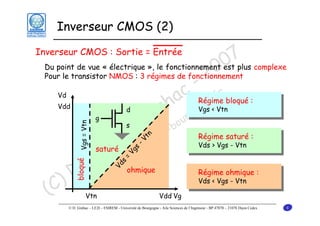

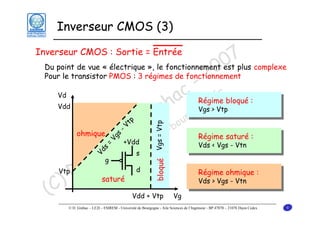

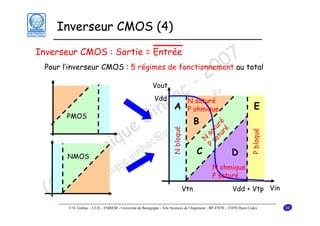

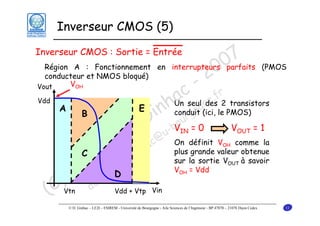

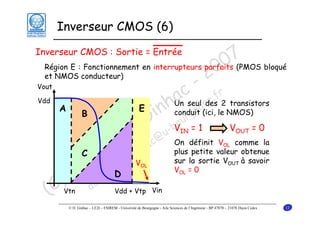

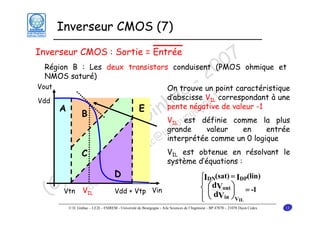

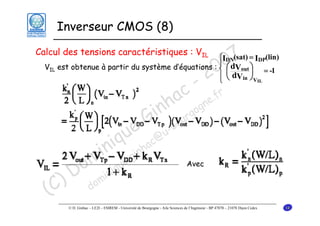

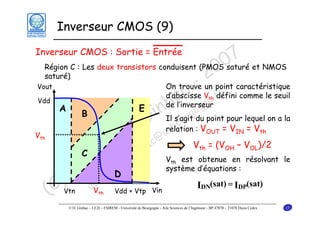

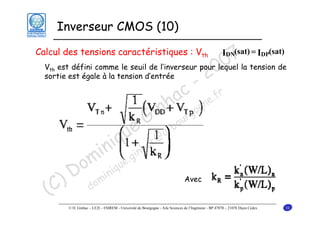

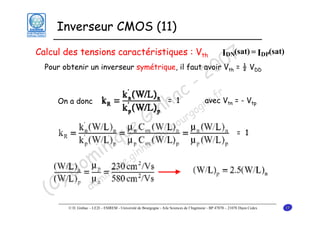

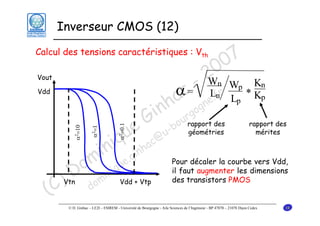

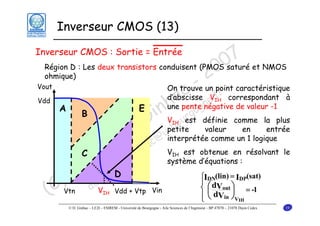

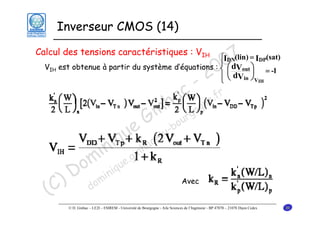

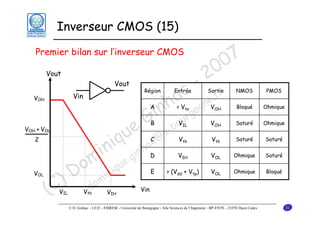

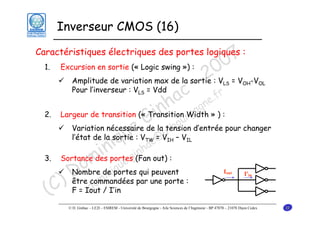

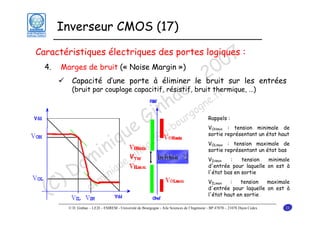

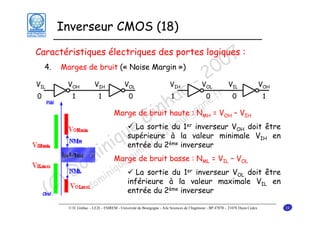

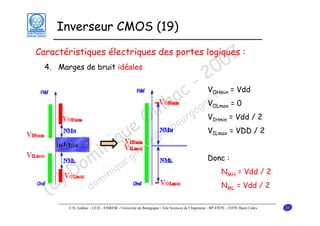

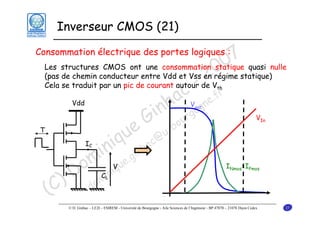

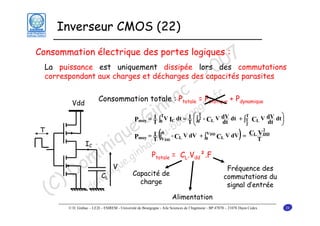

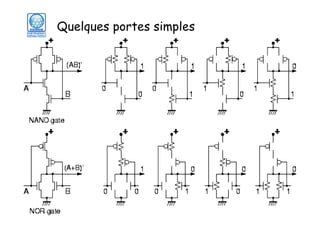

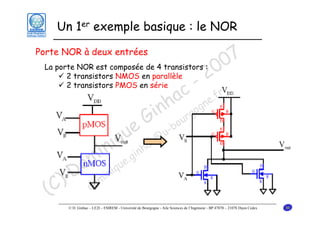

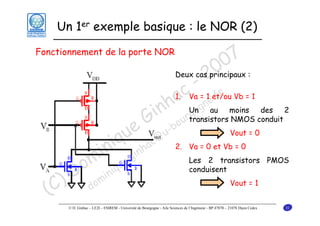

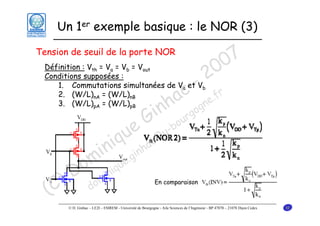

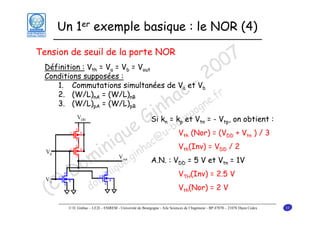

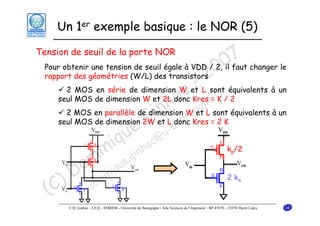

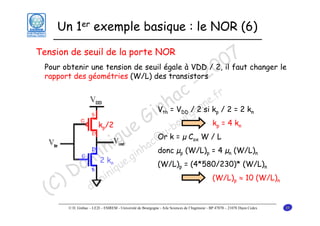

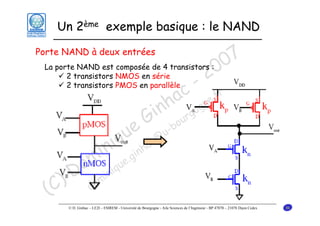

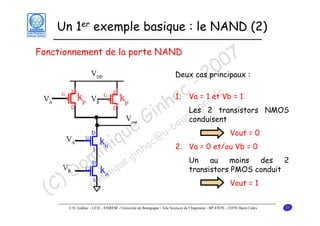

Le document traite des principes fondamentaux de la microélectronique numérique, notamment de la technologie CMOS, qui combine des transistors NMOS et PMOS pour réaliser des opérations logiques. Il présente des détails sur le fonctionnement et le design des inverseurs CMOS, y compris les régimes de fonctionnement des transistors et les calculs associés aux tensions caractéristiques. L'objectif du cours est de fournir une compréhension approfondie de la structure et du fonctionnement des circuits logiques en utilisant la technologie CMOS.