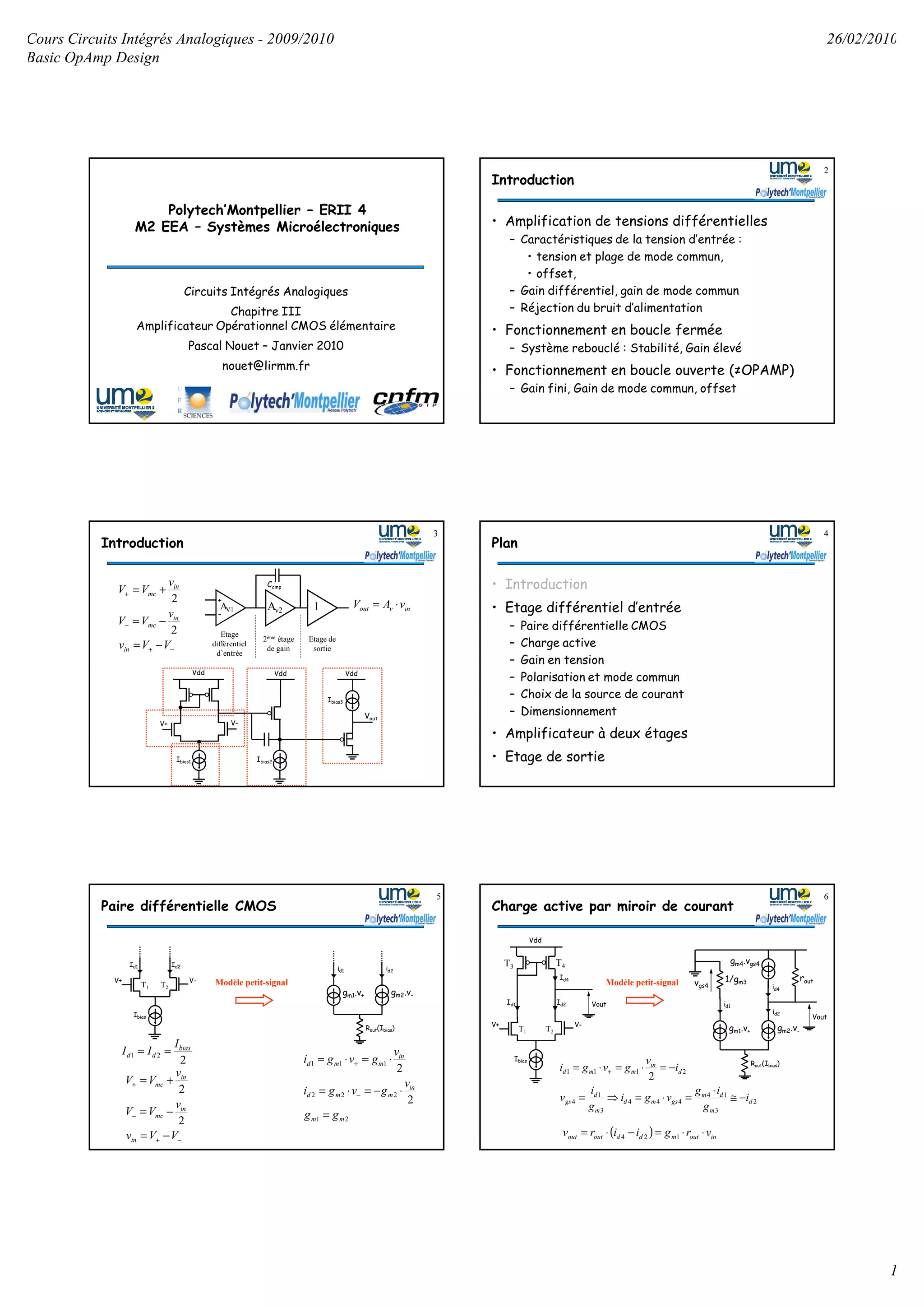

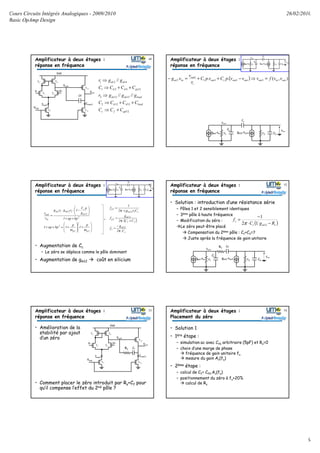

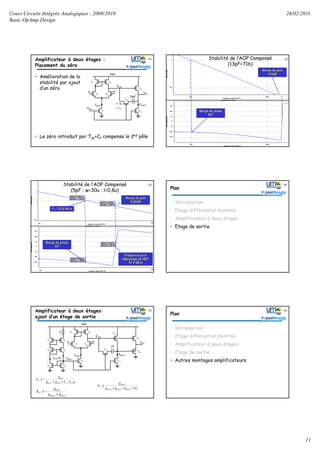

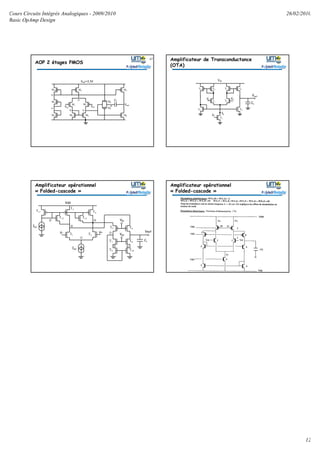

Ce document traite de la conception des amplificateurs opérationnels CMOS, incluant les principes d'amplification, les caractéristiques des étages différentiels, et les méthodes de dimensionnement pour optimiser le gain. Il aborde également la réponse en fréquence, les effets des résistances en sortie, et les implications sur la stabilité et les performances dynamiques. Des calculs et des simulations sont présentés pour illustrer les concepts discutés.