Chapitre3 prog dsplf3

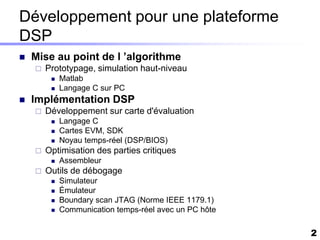

- 1. Développement pour une plateforme DSP Mise au point de l ’algorithme Prototypage, simulation haut-niveau Matlab Langage C sur PC Implémentation DSP Développement sur carte d'évaluation Langage C Cartes EVM, SDK Noyau temps-réel (DSP/BIOS) Optimisation des parties critiques Assembleur Outils de débogage Simulateur Émulateur Boundary scan JTAG (Norme IEEE 1179.1) Communication temps-réel avec un PC hôte 2

- 2. Développement pour un DSP Outils de Compilateur *.asm conception *.c C IDE *.asm Assembleur *.obj *.lst Editeur de Texte *.cmd Linker *.out *.map Simulateur *.hex DSP Chargement sur la cible 3

- 3. C vs. assembleur Assembleur Langage C Langage bas-niveau Langage de plus haut- Fastidieux niveau Jeux d’instructions Plus rapide à coder complexes et irréguliers Meilleure portabilité Spécifique à chaque Code machine généré constructeur moins efficace Plus puissant Malgré l’optimisation par Accès direct à certains le compilateur registres inconnus du C Outils de développement Nécessaire pour une Noyau temps-réel optimisation poussée (DSP/BIOS) Configuration de la carte Librairies de calculs optimisées (DSPLIB) 4

- 4. Outils d'aide au développement User Application Drivers DSP/BIOS™ Dsplib CSL Kernel/Scheduler Imglib CODEC Timer McBSP EMIF CPU DSP DIP Switches Target Board 5

- 5. CSL (Chip Support Library) Librairie pour faciliter C67x™ DSP Modules l'utilisation des CHIP périphériques internes du DAA DSP Plateformes C5000 et C6000 DAT Texas Instruments DMA Accessible depuis le EBUS langage C GPIO Organisation en modules HPI Un module par périphérique IRQ MCBSP PLL PWR UART WDTIM 6

- 6. Avantages d'une librairie de support de type CSL Abstraction du matériel à travers une API logicielle Configuration Accès aux ressources Macros pour accéder au niveau des contenus de registres Intégré au noyau temps-réel DSP/BIOS Interface graphique CSL Facilitation du développement Méthodes standards d'accès aux périphériques Temps de développement réduit Programmation à plus haut-niveau Utile pour compenser l'augmentation de la complexité des processeurs et des applications 7

- 7. Librairies spécialisées (DSPLIB, IMGLIB) Librairies de support pour le calcul Traitement du signal ou des images Déjà programmées Optimisées Utilisables depuis le langage C Fonctionnalités de base FFT Filtrage Mathématiques et trigonométrie Calcul matriciel 8

- 8. Propriétés des systèmes temps-réel Piloté par évènements Synchrones (chronomètre) Asynchrones (interruptions des E/S) Contraint dans le temps Contraintes dures (deadlines critiques) Contraintes souples (deadlines non critiques) Concurrence de l'exécution Contraintes sur plusieurs traitements en parallèle Nécessite un ordonnancement multi-tâches (plusieurs traitements à la fois) préemptif (toute tâche peut être interrompue par une tâche plus prioritaire) Déterministe et fiable Comportement du système prédictible Temps de réponse bornés 9

- 9. Système temps-réel DSP BIOS Noyau temps-réel Ordonnanceur temps-réel Gestion multi-threads préemptive Outils d'analyse temps-réel Débogage sans interruption de l'exécution Profiling, vision des threads Intégration avec Real-time data exchange (RTDX) Communication hôte↔DSP pendant l'exécution Chip Support Library (CSL) 10

- 10. Stratification des traitements sous DSP/BIOS Hard Real-time 1st-TIER Interruptions matérielles Traitement par échantillon Réaction à la microseconde 2nd-TIER Interruptions logicielles Traitement par blocs Réaction à la milliseconde Traitements ordonnancés Multi-tâche Exécution concurrente Tâche de fond (idle) S'il reste du temps Soft Real-time 11

- 11. Mise en œuvre et implémentation de filtres RIF et RII 12

- 12. Méthodologie d'implantation d'un filtre Étape 0 : Choix du filtre Choix du filtre et calcul des coefficients Étape 1 : Choix de structure Choix d'un schéma d'implantation Écriture des équations correspondantes Étape 2 : Choix algorithmiques Choix de l'implantation mémoire et des variables Écriture de l'algorithme Étape 3 : Choix numériques Choix du format Qk Écriture du programme Étape 4 : Validation Définir un protocole de test et l'appliquer Etape 5 : Optimisation 13

- 13. Étape 1 : Schéma et équations |H(f )| pass-band stop-band 1 fc : cut-of f f requency fs/2 f (norm) (a) |H(f )| pass-band transition band stop-band |H(f )| (dB) (linear) p 1 p 0 1 1 p pass-band -3 ripple stop-band ripple s s fs/2 f (norm) fs b : stop-band f requency fc : cut-of f f requency fpb : pass-band f requency (b)

- 14. Méthodes de synthèse d'un filtre Il existe de nombreuses méthodes Méthode de la fenêtre Optimisation par moindres carrés Calcul des coefficients par approximation de tchebycheff Par TFD récursive etc.

- 21. Étape 1 : Schéma et équations Exemple sur une cellule RII du 2e ordre s wn b0 xn yn z-1 -a1 w b1 wn sxn a1wn1 a2 wn2 n-1 z-1 yn b0 wn b1wn1 b2 wn2 -a2 b2 Équations correspondantes wn-2 Forme directe II 22

- 22. Étape 2 : Variables et algorithme Entrées : coefs dbuffer x (contient xn) 0 s 0 wn-1 w(n-1) dbuffer (contient wn-1 et wn-2) coefs (contient les coefficients) 1 a1 1 wn-2 w(n-2) Variable temporaire : 2 a2 tableau des w (recevra wn) 3 b2 retards Calcul 4 b1 wn ← s * xn – a1 * w(n-1) – a2 * w(n-2) 5 b0 xn x y ← b0 * wn + b1 * w(n-1) + b2 * w(n-2) tableau des Mise à jour retards ? puis yn y coefficients w(n-2) ← w(n-1) ? puis wn w w(n-1) ← wn variables Sorties : temporaires y (reçoit yn) dbuffer (contient wn'-1 et wn'-2 pour n'=n+1) État de la mémoire lors de l'appel de la fonction 23

- 23. Étape 3 : Format Qk et programme C int coefs[6]; x(n) Q15 int dbuffer[2]; s Q15 int cellule(int x) { ai Q15 int w; int y; bi Q15 /* Calcul */ wk Q15 w=((long)coefs[0]*x +(long)coefs[1]*dbuffer[0] –(long)coefs[2]*dbuffer[1]) >> 15; y=((long)coefs[5]*w +(long)coefs[4]*dbuffer[1] Conversion algorithme (calcul sur des réels) +(long)coefs[3]*dbuffer[0]) >> 15; vers programme (calcul en format Qk) /* Mise à jour retards */ dbuffer[1]=dbuffer[0]; s*x dbuffer[0]=w; devient /* Sortie */ (coefs[0]*x)>>15 return y; pour un résultat en Q15 } 24

- 24. Étape 3 : Programme détaillé Si programmation ACC=x(n) s en assembleur, ACC=ACC - a1 w(n-1) nécessité de ACC=ACC - a2 w(n-2) décomposer en w(n)=ACC>>15 ACC=w(n) b0 calculs élémentaires ACC=ACC + b2 w(n-2) Algorithmedétaillé ACC=ACC + b1 w(n-1) Conversion en y(n)=ACC>>15 assembleur w(n-2)=w(n-1) w(n-1)=w(n) 25

- 25. Implantation mémoire pour cellules en cascade coefs dbuffer 0 w1(n-1) 0 s cellule 1 1 w1(n-2) 1 a11 2+1 w2(n-1) 2 a12 cellule 2 cellule 1 2+2 w2(n-2) … b12 … b11 5 b10 5+1 a21 5+2 a22 … b22 cellule 2 b21 b20 26

- 26. Filtres RIF Structure transverse Implémentation par Buffer linéaire Buffer circulaire 27

- 27. Structures pour filtre RIF Structure transverse avec ligne à retard y n b0 xn b1 xn 1 .... bN 1 xn N 1 -1 -1 -1 x(n) z z z b b b b 0 1 2 N-1 + + + y (n) Structure en treillis (filtres adaptatifs) y0(n) y1(n) y2(n) y3(n) + + + x(n) k1 k2 k3 u1(n) u2(n) u3(n) u0(n) z-1 + z-1 + z-1 + yi(n) = yi-1(n) + ki ui-1(n) et ui(n) = k1 yi-1(n) + ui-1(n-1) avec y0(n)=u0(n)=x(n). 28

- 28. Structures pour filtre RIF Structures en cascade: N 1 k b b z 1 b z 2 ... b N 1 H z bk z z 0 1 2 N 1 k 0 N 1 z N 1 b 1 b 2 b b 1 1 z 2 z ... 0 b b b 0 0 0 M b 1 b z 1 b z 2 0 k 1 k ,1 k ,2 x(n) b0 y (n) + + + z -1 z -1 z -1 b 1,1 b 2,1 b M,1 + + + z -1 z -1 z -1 b 1,2 b 2,2 b M,2 29

- 29. Filtre RIF par structure transverse Deux aspects Mise à jour de la mémoire A chaque réception d’une nouvelle donnée x(n) Calcul du filtre ACCU=0 for i=0 to N-1: ACCU ← ACCU + h(i) x(n-i) Sortie de y(n)=ACCU 30

- 30. N 1 y n bi xn i Buffer linéaire i 0 Schéma "état mémoire" Schéma de structure de filtre x(n) y(n) xtab xtab 0 x(n-1) 0 x(n) b0 1 x(n-2) 1 x(n-1) b1 … 2 x(n-2) b2 … … … … … … … … … N-2 x(n-N+1) N-2 x(n-N+2) bN-2 N-1 x(n-N) N-1 x(n-N+1) bN-1 x(n-N) Mise à jour du buffer Calcul de y(n) 31

- 31. N 1 y n bi xn i Buffer circulaire i 0 Schéma "état mémoire" Schéma de structure de filtre x(n) y(n) xtab xtab 0 x(n-k+1) 0 x(n-k+1) bk+1 1 … 1 … … x(n-N+1) x(n-N+1) bN-1 x(n-N) idx x(n) b0 idx x(n-1) x(n-1) b1 x(n-2) x(n-2) b2 N-2 … N-2 … … N-1 x(n-k) N-1 x(n-k) bk Mise à jour du buffer Calcul de y(n) 32

- 32. Quantification des coefficients RIF Virgule fixe: N 1 B=16 bits pour h(i) , x(n-i) et y(n) y n hi xn i i 0 40 bits pour les accumulateurs Représentation Qk Coefficient de magnitude maximale: hmax = max |h(i)| Nombre de bits nécessaires pour la partie entière : BE = log2(hmax) Codage Qk avec k = B – BE h(i) = round(h(i)/2k) 33

- 33. Filtre RIF avec buffer circulaire en assembleur N 1 y n hi xn i N .set 32 ; adr_x+d supposé chargé i 0 dans AR2 Adresses Contenu STM #(coef)+N-1, AR3 Adresses Contenu k = adr_x x(n-N+d-1) STM #(adr_y), AR5 i = coef h(N-1) …… …… i +1 h(N-2) k+d-1 x(n-N+1) STM #N, BK STM #1, AR0 i+2 h(N-3) k+d x(n) …… …… …… …… RPTZ A, #N-1 i+N-1 h(0) k+N x(n-N+d) MAC *AR2+0%, *AR3-, A Mémoire Programme Mémoire Données STH A, *AR5 Rmq: les log2(N) bits de poids faible de adr_x doivent être nuls 34

- 34. Exemple d’implémentation d’un filtre RIF en Q15 short fir_filter (short input) { int i; short output; int acc=0; int prod; R_in[0] = input; /* lire les valeurs des échantillons */ acc = 0; /* initialisation de l’acc à zéro*/ for (i=0; i<128; i++) { prod = (h[i]*R_in[i]); /* Q.15 */ acc = acc + prod; /* mise a jour des 32-bit de l’acc */ } output = (short) (acc>>15); /* mise en forme de l’output (16-bits) */ for (i=127; i>0; i--) /* décalage des échantillons */ R_in[i]=R_in[i-1]; return output; }

- 35. Filtres RII Structures de filtres Décomposition en élements simples Problèmes de quantification 36

- 36. Filtre RII Fonction de transfert rationnelle Q N(z) bi z i i0 H(z) P D( z ) 1 ak z k k 1 Equation aux différences Q P yn bi xni ak ynk i 0 k 1 37

- 37. Filtre RII – Pôles et zéros Zéros au numérateur Q Q bi z b0 1 zi z 1 i 0 i i 0 Pôles au dénominateur P P 1 ai z 1 pi z 1 i i 1 i 0 38

- 38. Forme directe I (ND) Q P yn bi xni ak yn k b0 xn yn z-1 z-1 i 0 k 1 b1 -a1 z-1 -a2 z-1 b2 1 z-1 z-1 H ( z) N ( z) b3 -a3 D( z ) •Forme non canonique : •Nécessite Q+P mémoires z-1 z-1 bQ-1 -aQ-1 Forme directe I (ND) 39

- 39. Forme directe II (DN) b0 xn yn 1 -a1 z-1 b1 H ( z) N ( z) D( z ) z-1 -a2 b2 •Forme canonique •Nécessite max(Q,P) mémoires -a3 z-1 b3 z-1 -aQ-1 bQ-1 Forme directe II (DN) 40

- 40. Forme directe II transposée b0 b0 xn yn xn yn z-1 z-1 -a1 b1 b1 -a1 z-1 -a2 b2 z-1 b2 -a2 z-1 -a3 b3 z-1 b3 -a3 z-1 z-1 -aQ-1 bQ-1 bQ-1 -aQ-1 Forme directe II Forme directe II transposée 41

- 41. Quantification des coefficients b0 xn yn -a1 z-1 b1 ak ak ak z-1 -a2 b2 -a3 z-1 b3 bk bk bk Quantification d’un coef : z-1 -aQ-1 bQ-1 aq = round(a*q)/q avec un pas de quantification q=2-k Forme directe II 42

- 42. Quantification des coefficients Q N(z) bi z i i0 H(z) a k a k a k P D( z ) 1 ak z k k 1 Le dénominateur quantifié devient : Q 1 Q 1 D z 1 ak z k 1 pl z 1 k 1 l 1 La fonction de transfert est donc perturbée. Plus le degré du polynôme est élevé, plus la fonction de transfert sera perturbée. 43

- 43. Décomposition d’un filtre RII en sections du deuxième ordre choisies pour leur stabilité coefficients réels (racines conjuguées) Structure parallèle Structure cascade c0 b0 b1 z 1 b0 b1 z 1 b2 z 2 b0 b1 z 1 b2 z 2 xn 1 a1 z 1 a2 z 2 1 a1 z 1 a2 z 2 yn 1 a1 z 1 a2 z 2 xn yn b0 b1 z 1 1 a1 z 1 a2 z 2 Factorisation Expansion partielle B( z ) N 1 1 bi 1 z 1 bi 2 z 2 b0 1 B( z ) N 1 bi 0 bi 1 z 1 A( z ) i 0 1 ai 1 z ai 2 z 2 c0 1 A( z ) i 0 1 ai 1 z ai 2 z 2 44

- 44. Décomposition en cascade x(n) s0 s1 s2 s3 y(n) H1 H2 H3 B( z ) N 1 1 bi1 z 1 bi 2 z 2 b0 1 2 b0 H1 ( z ) H 2 ( z ) H 3 ( z ) A( z ) i 0 1 ai1 z ai 2 z avec : 1 bi1 z 1 bi 2 z 2 et s0 s1s2 s3 b0 H i ( z) 1 ai1 z 1 ai 2 z 2 45