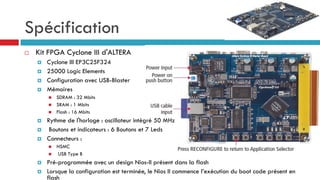

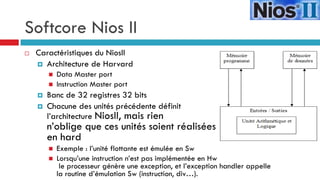

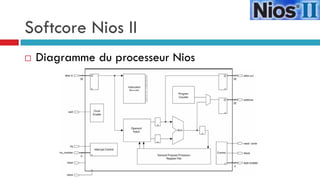

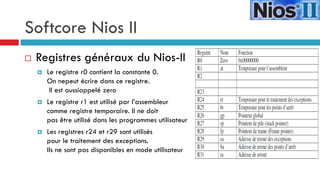

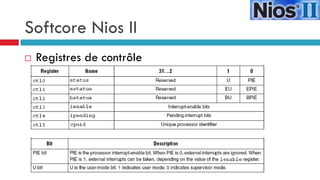

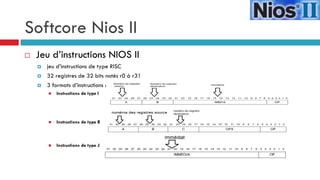

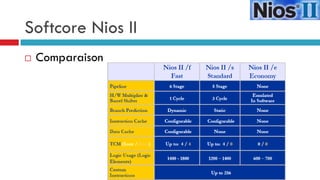

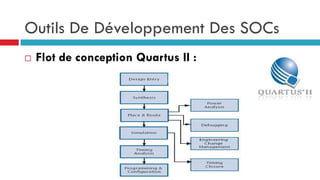

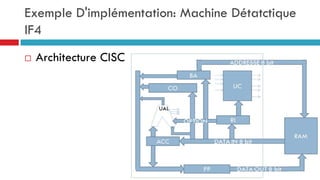

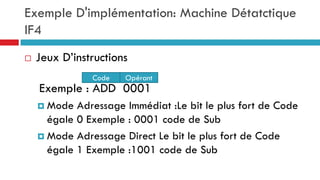

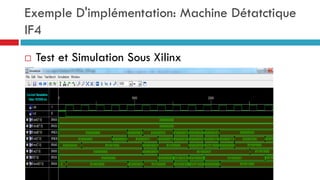

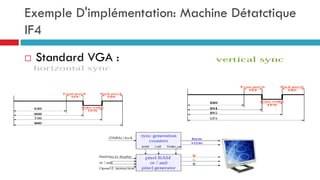

Le document traite d'un kit d'évaluation Nios II d'Altera, incluant les spécifications d'une carte fille LCD, d'un kit FPGA Cyclone III et de diverses caractéristiques du processeur Nios II. Il aborde également les systèmes d'exploitation temps réel comme μc/os II et μclinux, et fournit des détails sur des outils de développement comme Quartus II et SOPC Builder. Enfin, il présente un exemple d'implémentation d'une machine d'état logique montrant la prise en charge des instructions et des fonctionnalités de base du processeur.